一种基于FPGA和ARM的线阵 CCD图像采集系统设计

严帅

摘要: 设计了一种基于Altera的FPGA芯片EP4CE10F17C8以及基于CortexM3构架的ARM处理器STM32F103VE,该系统通过FPGA对线阵CCD进行时序的驱动,并完成像素信号的采集、硬件处理以及传输工作。ARM作为FPGA的外挂处理器,实现数据信息的软件处理以及对整个系统的控制。介绍了该系统的基本原理,并给出了详细的基于FPGA和ARM的软硬件联合设计方案。

关键词: CCD; FPGA; ARM; 软硬件联合设计

中图分类号: TP 39文献标志码: Adoi: 10.3969/j.issn.10055630.2015.03.013

Abstract: The CCD driving system is based on a combinational system with Altera FPGA chip EP4CE10F17C8 and ARM processor STM32F103VE which is powered by CortexM3. The system uses FPGA to control CCD by timing drive circuit as well as information acquisition, data processing and data transmission. ARM is used as an external processor for FPGA. It accomplishes data processing based on software and controlling the entire system. The paper introduces the basic principle of the system, gives the results of the design of software and hardware based on FPGA and ARM.

Keywords: CCD; FPGA; ARM; CoDesign

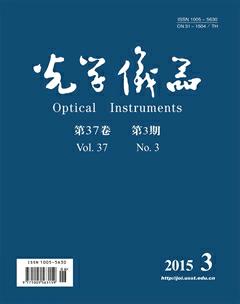

引言CCD(Charge Coupled Device)是一种可以实现光电转换的图像传感器,其将图像信号直接转换成电荷信号,后端一般通过调理电路连接至AD转换器件,从而获得各像素点对应的数字信号量为嵌入式设备所用[1]。CCD图像传感器具有精度高、灵敏度高、自扫描和宽光谱响应范围等诸多优点,广泛应用在图像扫描、条码扫描、非接触式位移测量、非接触式尺寸检测等工业测量与成像领域[2]。传统的CCD驱动系统普遍采用单一的MCU或DSP作为整个系统驱动控制的核心,以MCU为例,其信号采集速度较慢,遇到高速信号任务时需要外接FIFO起到数据缓存的作用,处理器功能比较简单,已经无法满足应用于现在检测系统的需求。采用FPGA+ARM作为该类系统的基本构架,可以利用FPGA的灵活性简化驱动电路的设计,并利用FPGA的并行性提高数据采集处理的速度,同时外挂的ARM芯片作为整个系统的控制器,可以实现一些通用且功能丰富的嵌入式系统应用[3]。1系统组成基于FPGA和ARM的线阵CCD图像采集系统在硬件上主要包括线阵CCD、CCD输出信号调理电路、FPGA芯片、ARM芯片、显示以及数据传输接口,其基本的原理框图如图1所示。

从图1可以看出由于系统采用FPGA+ARM的系统构架,整个采集系统可以分为前端和后端两个部分。系统的前端即FPGA之上的系统主要完成外部芯片驱动以及数据流的采集和缓存功能,FPGA提供CCD、AD芯片正常工作所需的驱动时序。线阵CCD在FPGA的驱动脉冲控制下进行自扫描,每个像素点将进行光电转换将光信号转换为电信号,并通过移位寄存器输出,线阵CCD的输出信号包含暗电流信号、直流分量信号以及各类噪声信号,为了取得良好的信噪比需要在CCD输出的后端接一级信号调理放大电路并配合AD芯片,AD芯片在FPGA产生的采样时钟的控制下将CCD的模拟信号转成相应的数字信号,并通过FPGA进行采集[4]。ARM与FPGA数据的交互主要通过ARM总线接口控制器完成,ARM通过对对应地址的读写操作完成采集系统的配置以及数据的采集工作。ARM微处理器采用意法半导体的STM32f103系列芯片,其内核基于CortexM3,具有72 MHz的主频,存储容量包括512 kbit的Flash以及64 kbit的RAM,外设方面包括UART、SPI、USB等常用通信接口,可以方便的实现外部各类通信方式,同时该系列芯片具有静态存储器控制器(FSMC)可外接片外存储器芯片,在本系统中,通过将FPGA连接至该控制器,实现ARM与FPGA的数据交互。

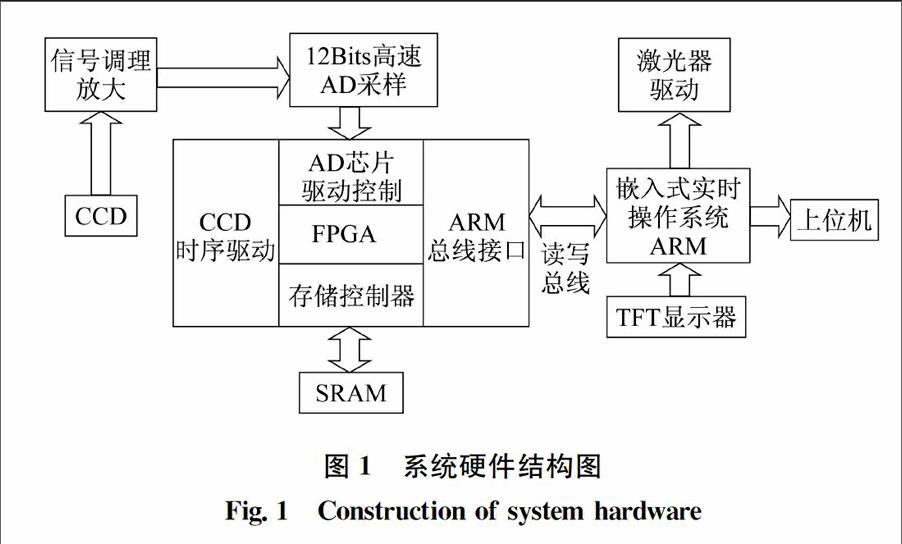

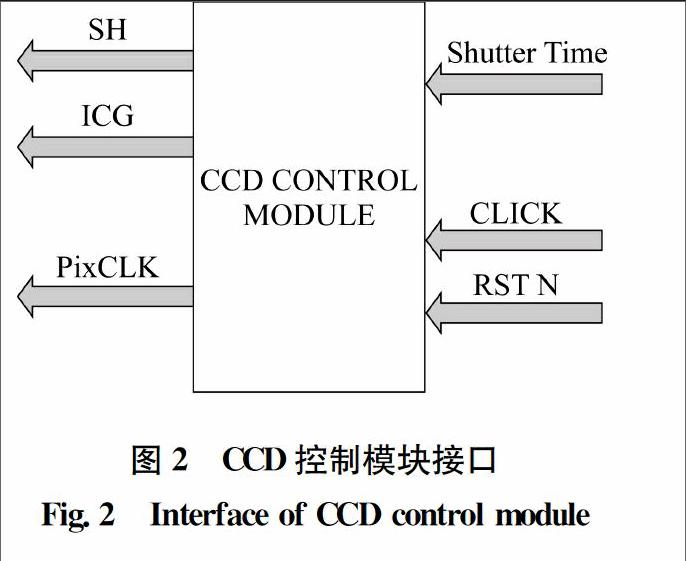

1.1线阵CCD及其驱动设计选用的CCD是TCD1304AP,该线阵CCD为日本TOSHIBA公司生产的一款高速、低暗电流线阵CCD,其内部总共具有3 694个像素,并具有电子快门功能以及采样保持电路。其中前32个像素以及后14像素为无效像素点用作暗电流的检测,实际有效像素点为3 648个。TCD1304AP的工作频率为2 MHz,像素速率为0.5 MHz,接口方面处理提供工作时钟以外,配合时序要求还需要提供ICG信号以及SH信号,其中ICG信号为帧起始信号,其上升沿的跳变控制一帧信号的开始。SH信号为电子快门功能信号,TCD1304具有独特的电子快门功能,可由外部驱动时序决定是否开启该功能,因此该线阵CCD具有两种工作模式:普通模式、电子快门模式。两种工作模式的主要区别在于SH信号。模式一中,每个CCD采集周期中间只有两个SH脉冲信号,其对应的有效光积分时间为第一个SH脉冲的下降沿到后一个SH脉冲的下降沿之间的时间。而模式二中,有效光积分时间为SH脉冲信号的周期。实际上,有效光积分时间其实就是采样结束后(ICG下降沿标志一帧采样结束)第一个SH脉冲的下降沿到其前一个SH脉冲的下降沿之间的时间。在模式二中,每个SH信号下降沿之间实际都在进行光信号的采集工作,只是其他这些光电转换后的信号并没有被转移到移位寄存器中得到输出。CCD器件通过ICG的信号来判断采集到的光信号是否有效。当ICG信号变为低电平时,CCD内部图2CCD控制模块接口的积分清除门将处于开启状态,如果在此期间有SH脉冲信号,光敏区域采集到的光电信号将被转移到移位寄存器,并在ICG重新恢复到高电平之后移位输出。CCD只有在满足符合要求的驱动时序下,才能得到良好的工作效果以及可靠的信号输出。因此,针对CCD的驱动模块的设计是整个系统是否能获得有效图像数据的前提。在FPGA上针对CCD的驱动要求,要设计一个负责用于CCD驱动的模块,其需要有输出到CCD的驱动信号,以及系统时钟的输入、参数控制信号的输入(调节电子快门)。该模块的接口定义和驱动时序仿真图分别如图2以及图3所示。

1.2ARM总线接口设计ARM总线接口用于FPGA与ARM之间进行数据的桥接,通过该接口将数据传输给ARM控制器做进一步处理同时接收ARM发来的对应指令并处理。其作为连接这个系统的前端与后端,是本系统在设计上的一个难点。该接口采用3位地址总线,数据总线采用16位数据线连接,即每次读写操作都可直接操作16位的数据。同时,总线还包括片选信号CS、读信号RD、写信号WR[5]。在STM32端通过其片上提供的静态存储器控制器(FSMC)与FPGA相连。

本系统采用用于NOR闪存的控制器时序,工作模式为异步、总线工作方式为非复用,所有的控制器输出信号由STM32内部时钟HCLK控制并在其上升沿变化[6]。具体采用FSMC提供的模式A作为实际工作方式。FPGA端只需对对应的时序操作进行解析即可完成数据的读写操作。该模块对应的外部接口框图如图4所示。图4中,DB[0]用于连接前端CCD数字信号的输出,通过Read Clock控制将数据逐一送到Data Bus总线上,前端的数据输出模块实际是一个经过封装的双RAM读写控制器,其使用的数据存储器可以是外部SRAM或者是片上通过IP核例化生成的双口异步RAM模块。该模块开辟两个RAM缓存区,分别用于缓存一帧的像素数据,并通过乒乓操作的方式采集以及送出CCD没帧的像素数据。本设计中采用两个大小为4 096、宽度为12 Bits的双口异步RAM,写时钟通过前端采集控制,读时钟通过ARM的FSMC控制由FSMC模块解析后生成对应的读时钟信号。2系统的总体设计对各个分模块进行设计之后需要对整个采集系统进行整合,每个模块的功能是否健全,输入输出是否合理,以及工作时钟设置等参数是否设置正确对整个系统是否能正确运行至关重要。系统的结构框图已经在图1中给出,这里要注意的几点包括,各模块的运行时钟需采用PLL提供的全局时钟网络、有效数据的读取和缓存信号需要考虑到外部器件信号的延迟、存储器控制器的读写等。经过将各模块进行整合并通过Quartus综合,最后通过SingalTapII检验实际工作情况。3结束语本文着重介绍了如何从系统的角度设计一个基于FPGA和ARM的线阵CCD图像采集系统,并详细介绍了CCD驱动的模块设计以及ARM总线接口的模块设计,提供了一种在FPGA上构建采集系统的方法,解决了以往采集系统在硬件上过于庞大和复杂的问题,从而达到小型化和智能化仪器趋势的要求。系统的模块的划分具有良好的可替换性,只需稍加修改便能应用到不同类型的外部器件中。外挂的ARM处理器可以弥补所用低端FPGA在硬核处理器上的缺陷,同时满足通用功能方面的需求,随着嵌入式微处理器的发展以及对基于嵌入式系统研究的深入,将使得CCD图像采集系统不论从功能上还是性能上具有更广阔的发展空间和使用价值。参考文献:

[1]刘立波.基于DSP的激光三角测距传感器研究[D].上海:上海交通大学,2008.

[2]李兴广.基于FPGA的高速非接触式位移测量系统[J].制造业自动化,2011,12(23):2224.

[3]刘爽,赵凯生,龙再川,等.基于ARM和FPGA的嵌入式CCD采集系统[J].电子·激光,2007,18(11):12961298.

[4]刘艳,赵洪,于效宇,等.一种可调线阵CCD信号采集处理系统[J].光学技术应用,2009,32(2):294299.

[5]潘松.EDA技术与Verilog HDL[M].北京:清华大学出版社,2013.

[6]EDA先锋工作室.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2011.

(编辑:程爱婕)