低功耗DDR高速信号的封装布线方案设计及信号完整性分析

秦征 尚文亚 于大全

摘 要: 不同于印制电路板的制作工艺,芯片封装基板的走线更细,线间距更窄。狭小的布线空间使传输线效应更为明显,而且封装设计的好坏直接影响芯片是否可以正常工作,同时芯片成本的控制要求布线层尽量要最少。这些问题使得高速信号布线面临严峻的挑战。在国家科技重大专项的资助下,使用全波电磁场仿真工具进行建模分析,研究了布线中线宽、线间距和参考地对信号传输质量和信号间串扰的影响,并且基于一款低功耗DDR高速芯片的双层封装布线设计,在实际设计方案中对分析结果进行了仿真验证,最终得到了一种高质量、低成本封装基板高速布线方案,速率达到1 333 Mb/s。

关键词: DDR; 高速信号; 封装布线; 信号串扰影响; 电路设计

中图分类号: TN02?34 文献标识码: A 文章编号: 1004?373X(2015)19?0135?05

Abstract: Compared with manufacture technique of printed circuit board, thinner wirings and more narrow wire spacing on the chip package substrate are needed. The narrow wiring space makes the transmission line effect more obvious. The packaging design impacts chip performance directly. The least wiring layers are needed for cost control of chip, which make the wiring of high?speed signal be faced with crucial challenge. This work is supported by the “National Science and Technology Major Project”. Modeling analysis is conducted with the full?wave electromagnetic field simulation tools to research the influences of wires′central line width, wire spacing and reference ground on signal transmission quality and signal crosstalk. Based on the double?layer packaging wiring design of a high?speed LPDDR chip, the analysis results were verified by simulation in actual design scheme. A high?speed wiring scheme of packaging substrate with high quality and low cost was obtained, whose rate reaches 1 333 Mb/s.

Keywords: DDR; high?speed signal; packaging wiring; signal crosstalk influence; circuit design

随着半导体技术的进步,芯片的特征尺寸不断缩小,伴随着光刻技术接近极限,互联损耗和延迟的增加以及新的失效机理的出现,使得芯片封装物理布线的难度逐渐增加。相较于印制电路板(PCB),芯片封装基板的走线更细,线间距更窄,传输线的各种效应更为明显,封装基板的布线优劣将直接影响芯片的最终性能[1]。本文通过基于第三代低功耗双倍速率(LPDDR3)高速信号的布线研究及优化,实现了一种低成本双层封装基板高密度、高速布线方案,同时对高速信号的串扰进行分析研究,为LPDDR3高密度布线提供了设计经验。

1 封装基板传输线电性能研究

对于消费类电子产品,成本控制是设计需要考虑的重要因素。为了最大程度地降低成本,本文选用两层金属层的布线方案,但是这样增加了走线密度,为高速信号的布线增加了极大困难。对于高速信号,不仅要求要把信号线布通,更需要保证高速信号的传输质量,因此需要在传输线理论的指导下,参考准确的频域和时域仿真结果对高速信号进行布线设计[2?3]。

1.1 插入损耗与反射损耗

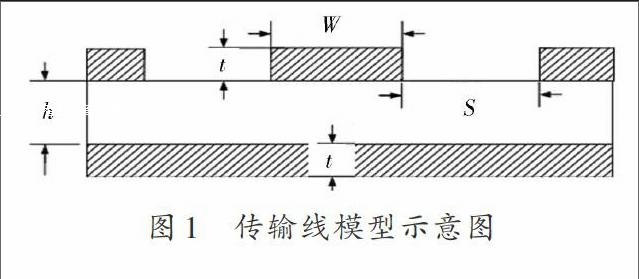

为了研究高速信号的插入损耗、反射损耗、相互耦合和回流路径所分布的走线层,本文根据封装基板结构建立了传输线模型,如图1和图2所示。

图1展示了微带线模型及参数含义,图2展示了建立的传输线模型,模型中从左至右分别为传输线1至传输线4。为了研究传输线的插入损耗和反射损耗,建立了3个类似图2的模型,每个模型具有不同的线宽或线间距。表1中给出了封装基板的结构参数,表2中列出了介质材料参数。

需要说明的是三个模型的线宽分别为25 μm,25 μm和40 μm,线间距分别为25 μm,45 μm和24 μm,这样的设计是由于布线空间和加工工艺的限制。仿真结果如图3,图4所示。由于传输线模型完全对称,所以只选取传输线1和传输线2 的传输和反射损耗进行对比说明。如图3,图4所示,当线宽和线间距相同时,越靠近外侧也就是同层地平面的线条插入损耗越大,反射损耗越小,传输性能越好;当线宽相同时,线间距越大,插入损耗越小,反射损耗越大,传输性能越差;当线间距相同时,线条越宽,插入损耗越大,反射损耗越小,传输性能越好。因此,从传输性能的角度看,增加线间距会影响传输质量,加宽线条则会提高传输性能,同时这两种方案都会增加布线空间。endprint

1.2 线间电场耦合

线条间电场相互耦合的仿真结果如图5所示。从图5(a)和图5(b)可以看出,当线宽相同时(25 μm),线间距越大,线条上边缘位置的电场越小,也就是相互之间的耦合越小。从图5(a)和图5(c)可以看出,当线间距相同时(25 μm),线宽越大,耦合产生的电场越小。而由于最外侧的线条靠近地平面,所以最外侧耦合最严重。

1.3 回流路径与参考地

为了最高效的给传输线提供回流路径,建立了模型考察回流路径的分布情况,如图6所示。从图6中可以看出,对于本文所采用的双层布线工艺来说,虽然相邻地平面也有返回电流流过,但是最重要的回流路径分布在布线层的同层地平面。根据这一结论,可以在布线设计中将参考地平面设计在同层,而相邻的金属层则不需要有完整的参考地平面,这样就极大地节省了布线空间,提高了布线密度,也正是基于这一点,双层布线方案才得以实现。

通过对线条传输、反射损耗和相互耦合的研究,发现对于这些因素的优化方向并不完全一致,优化传输和反射损耗时希望用宽线条紧密排列,这样会加重他们之间的耦合,而增加线间距减小耦合时又会降低信号的传输质量;因此在进行高速布线时要综合考虑这些因素,寻找一个最优的平衡点。而对于屏蔽线的设计,考虑布线空间有限,把每两条信号线进行隔离作为最优方案。

2 DDR3布线方案

2.1 DDR3拓扑结构及封装版图设计

DDR3的通用信号传输模式如图7所示,多个DDR存储器可以连接在相同的内存控制端同时工作。在本文中,使用的是只有一个DDR存储器的芯片。在进行数据读取时,信号由DDR内存发送,在进行数据写入时,信号由存储控制端发送,而时钟、地址和控制信号始终由存储控制端发送DDR内存接收,数据信号在时钟的上升和下降边沿均进行采样,因此实现双倍速率[4?5]。信号分为4组(Byte)同步传输,每组包括8个信号(DQ),一对差分时钟信号(DQS和DQSN)和一个数据掩码信号(DQM),同一组数据线要走在一起,以此减小时序问题,差分时钟信号要紧耦合设计。

根据布线要求,布线方案一如图8所示[6],图中仅显示了布线区域。图8左侧所示是第一层信号线分布(包括所有DDR3的控制和功能信号线),右侧所示为第二层时钟信号分布。基于本文前部分的研究结果,下层金属的参考地作用小于上层地平面,因此将下层金属同样设计为走线层;这样多出来的布线空间刚好可以对信号线进行隔离,同时下层布线空间相对宽松,可以完全满足差分时钟信号的紧耦合设计。封装基板的参数仍如表1所示,这里采用25 μm线宽和25 μm线间距。

高速信号的串扰是设计中需要重点考虑的因素[7],虽然方案一中对每组信号进行了地隔离,但是为了进一步减小串扰,本文基于方案一进行了优化。

方案二中,信号线间的隔离地被移除,同时信号线间的距离增大为45 μm。

方案三的布线方式与方案二相似,不同之处是线宽增大为40 μm,线间距缩小为25 μm,因此图9中并未展示。

方案四中增加了隔离地的数量,由方案一中的每组信号进行隔离变为每两根信号线进行隔离。理想情况是对每一条信号线进行隔离,但是对于高密度布线这种方案几乎是不可实现的,根据前面的研究结果,对每两条信号线进行隔离同样可以达到比较好的效果,因此选用这种布线方式。

2.2 插入损耗与反射损耗验证

对四个布线方案在全波电磁场仿真软件中提取[S]参数进行分析[8?9]。图9和图10展示了四个方案中DQ线条的反射损耗和插入损耗。

可以看到方案四的反射损耗最小插入损耗最大,传输性能最好;方案二的反射损耗最大插入损耗最小,传输性能最差;方案一和方案三的反射和插入损耗较为接近,方案三略好于方案一。这说明在实际布线中,隔离地的效果非常明显,而当没有隔离地时,增大线间距会使信号传输变差信号反射更严重,增大线宽虽然可以使信号插入损耗变好,但是效果并不明显。仿真结果与前文研究结论的趋势一致,只是由于实际布线中几个方案的线长不完全一致,相邻线条和金属层也有微小的差异,使得实际方案中有些影响因素变得不太明显。

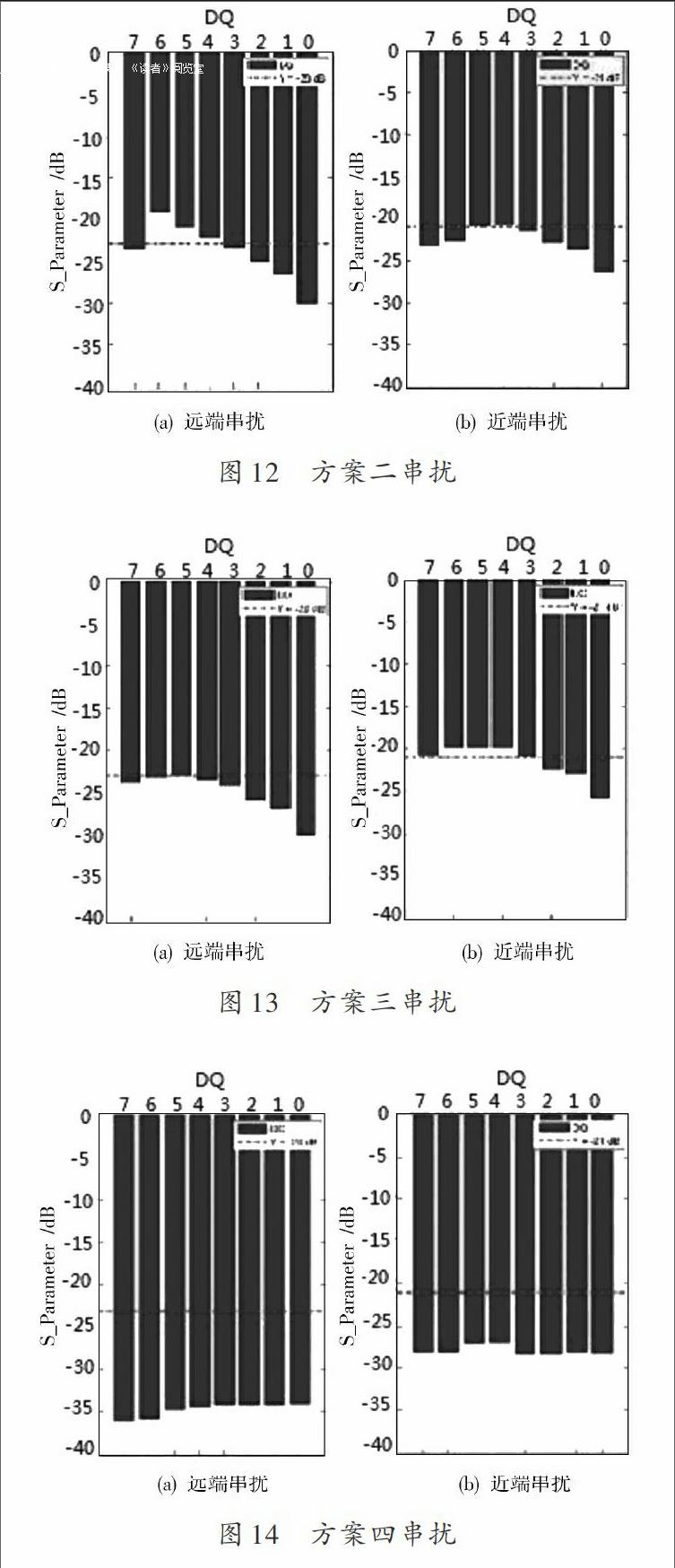

2.3 信号间串扰分析

信号线间串扰的大小并不能被反射损耗和插入损耗反映,因此对[S]参数进行数学处理,得到四个布线方案的串扰结果[10]。这里只通过一组数据线(8条数据线条)进行对比说明,如图11~图14所示。通过图11和图12的对比可以看到,由于布线空间的限制,线间距由1倍线宽增加到近似2倍线宽并不能有效改善串扰问题。

对比图11和图12,在不添加隔离地也不增加线间距的情况下,增加线宽可以明显减小远端串扰。如图12所示,当对每两条信号线进行隔离时,信号间串扰被有效降低,而且由于每条信号线所处的环境相似(分别相邻一条信号线和一条隔离地线),同组信号线的串扰大小较为平均,这样保证了同组信号具有相似的信号传输质量。

对每两条信号线进行地线隔离仍然需要占用比较多的布线空间,对于越来越高的布线密度来说也是一个严峻的考验。如图11所示,方案一中每组信号线靠近两侧的线条有相邻的地平面,因此DQ0和DQ7的串扰很小,这说明即使线条只有一侧有相邻的参考地,其串扰也能有很大程度的改善,对于布线空间不足的情况,可以对串扰较严重的区域或者信号线进行有针对性的隔离,以此将信号串扰控制在比较低的水平。

2.4 时域分析

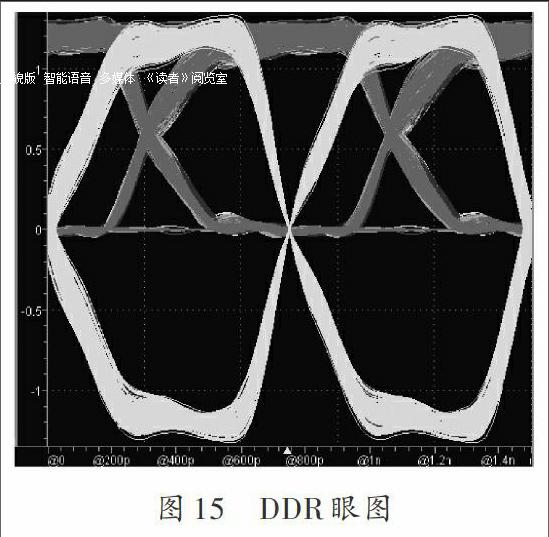

经过串扰仿真和优化后,确定方案四为最终方案,然后对方案四进行时域分析,图15为Byte0的眼图结果。

进行眼图分析时使用的是随机码型,从仿真结果可以看出,DQ信号线和DQS时钟信号的眼宽眼高良好,DQ和DQS的时序也良好,保证了足够的建立时间和保持时间,说明此种封装布线方案可以使高速信号高质量传输。endprint

3 结 语

通过本文研究得出,在实际的芯片封装高速信号布线中,较为有效地减小反射增大传输的方式是在空间允许情况下加宽线条,同时这对减小信号间串扰也起到很大作用。虽然理论上增加线间距可以减小串扰,但是在实际布线中由于空间限制,效果并不明显。减小串扰的最好方式是对信号线进行地隔离,使其有较近的回流路径,对于实际封装基板结构来说,信号的回流路径主要分布在同层地平面而不是相邻布线层,因此合理设计同层地平面成为减小串扰的重要方式,同时对相邻地平面的限制可以适当降低,为其他线条提供更宽裕的布线空间。根据研究结果,本文成功设计了一款低成本双层布线结构的芯片封装,可以保证高质量传输高速LPDDR3信号。

参考文献

[1] FANG Jiawei, CHANG Yaowen. Area?I/O flip?chip routing for chip?package co?design considering signal skews [J]. IEEE Transactions on Computer?Aided Design of Integrated Circuits and Systems, 2010, 29(5): 711?721.

[2] HALL S H, HECK H I. Advanced signal integrity for high?speed digital designs [M]. Hoboken: John Wiley & Sons, 2009.

[3] BOGATIN E. Signal integrity simplified [M]. New Jersey: Prentice Hall PTR, 2003.

[4] ZHOU Runjing, HAO Yuanyuan, HU Jinsong. Quick system?level DDR3 signal integrity simulation research [J]. Journal of Electronic Science and Technology, 2013, 11(3): 9?14.

[5] 李晋文,胡军,曹跃胜,等.DDR3时序分析与设计[J].计算机科学,2012,39(4):293?295.

[6] 周润景,苏良碧.Cadence高速电路板设计与仿真[M].4版.北京:电子工业出版社,2011.

[7] CHANG J. Design considerations for the DDR3 memory sub?system [R]. Korea: Samsung Semiconductor, 2004.

[8] YOUNG B. Digital signal integrity: modeling and simulation with interconnects and package [M]. New Jersey: Prentice Hall, 2001.

[9] RONG Aosheng, CANGELLARIS A C. Interconnect transient simulation in the presence of layout and routing uncertainty [C]// 2011 IEEE 20th Conference on Electrical Performance of Electronic Packaging and Systems. San Jose: IEEE, 2011: 157?160.

[10] LEE K, JUNG H K, CHI H J, et al. Serpentine microstrip lines with zero far?end crosstalk for parallel high?speed DRAM interfaces [J]. IEEE Transactions on Advanced Packaging, 2010, 33(2): 552? 558.endprint