基于FPGA的DDS设计与实现

靳成一+肖蕾

摘 要

DDS在电信和电子仪器方面的应用已经非常广泛,是完成设备数字化的重要技术。笔者设计、利用ISE10.0软件实现三相矩形波信号、正弦波信号以及调频调相信号的波形仿真,同时用Xilinx的FPGA核心板SPARTAN3AN,与性能很好的MCU—ATMEGA128相结合,进行DDS的设计和实现。

【关键词】FPGADDS设计 实现

由于直接数字频率合成技术(简称DDS)有高分辨率、低功耗、低成本、全数字化接口、快速转换时间以及容易跟微处理器结合等诸多优势,最近这些年的发展十分迅速。尽管现在不少的芯片制造企业研发出专用DDS芯片,但在一些特殊的场合,其输出的波形带宽、种类以及精度等均不能满足设计需求。故而,把DDS和高性能数字器件有机结合就成为现在的热点课题。

1 DDS的原理

DDS主要是運用正弦信号的相位和时间成线性关系这一特征,借助查表的方法获取信号的瞬时值,以达到频率合成。相位累加器是通过N位加法器和累加寄存器级联而成。每当进行一时钟脉冲Fs,加法器都会把频率控制字K和累加寄存器所输出的累加相位数加到一起,把所得到的结果送到累加寄存器的数据输入端。累加寄存器会把上一时钟脉冲所得到的相位数反馈至加法器的输入端,从而使加法器在下一时钟脉冲继续跟频率控制字K进行相加。把相位累加器所输出的数据当作波形存储器的相位取样的地址,如此就能将存于存储器中的波形抽样值通过表查出,以实现从相位至幅值的转换。该存储器的输出数据先送至D/A转换器中,而后由D/A转换器把用数字量表示的波形幅值转换为合成频率的模拟量形式信号。

2 基于FPGA的DDS设计

2.1 系统整体设计

运用Xilinx的XC3S400FPGA,尽量达到设计的数字化与集成化。在实现的时候,运用VHDL语言将DDS进行封装,以有效达到资源的复用和及灵活配置。加之单片机的控制、液晶显示和数据的转换,能够比较理想的达到设计要求。系统的框图如图1中所示。

2.2 DDS核心设计

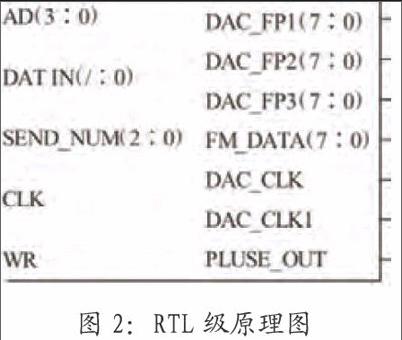

DDS的核心就在FPGA电路方面的设计。在FPGA电路实现以后,就可以在FPGA中生成波形数字信号。在设计过程里用VHDL语言,可构建一标准正弦波产生和FM调制功能的DDS模块,同时还构建起一矩形波产生模块。这一部分设计在ISE综合以后的RTL级原理见图2中所示。DDS其核心就是累加器和查表两个模块。

2.3 对累加器进行设计

DDS核心是相位累加器,输出正弦波的频率是由DDS与参考时钟等所决定。即DDS输出的信号频率=(fclk×Kf)/2N,其中,累加器位数由N表示,累加时钟频率用fclk表示,控制字用Kf表示,因为耗时随着位数N的变化而变化,所以,保证输出频率前提下,可以利用参考频率的降低来提高其分辨率,本文N=32。

3 基于FPGA的DDS实现

3.1 设计实现在ISE中的DDS模块

本设计利用的是ISE10.0软件,其中各个小模块要利用VHDL语言进行设计,结合DDS的原理,连接软件中的各个模块,最后实现在FPGA中DDS模块的设计。

3.2 实现MODESIM中的仿真

在MODESIM中,对正弦波、方波和调频波仿真,然后再检验仿真生成的波形。为了检验是否能够符合设计要求,分别对各个波形进行如下测试,一是相位是0°、225°、315°,正弦波频率是1KHz;载波频率是10KHz,FM调制信号频率是1KHz;占空比是0.5,方波频率是50MHz等等。结果是都能满足其要求。

4 基于FPGA的DDS硬件实现

4.1 硬件设计的实现

FPGA被作为是DDS的模块载体,利用的核心板是SPARTAN3AN,速度高,稳定性强。在本系统中,MCU利用的是ATMEGA128单片机,此单片机是ATMEL公司开发的。而系统的主控芯片完成参数输入是借助于4*4的薄膜按键,操作状态和数据由OCMJ4x8C液晶显示器可以显示出来,其显示器与DDS模块通信,能够对输出的波形进行控制。

4.2 进行数据测试和相关分析

表1汇总了对三相正弦波信号频率进行测试的结果,其中,测试数据大多间隔1分钟。多次测量与分析发现频率的精度要高于0.1%,而稳定度要高于10至6,同时输出信号的峰峰值要大于等于20V,可以任意调整三相正弦信号的相位。另外,测试并且分析矩形波信号与调频波信号,都能符合设计指标。

5 结语

综上,利用FPGA器件,本设计采用了DDS技术进而研制了全数字波形信号发生器。通过仿真与实测说明,频率小则切换速度快,而且频率也容易得到控制,设计电路也较简单。因此, 本系统可据其实际,输出多种波形图,功能多样,有调频、调相与调幅等,实用性良好。

参考文献

[1]张厥胜,曹丽娜.锁相与频率合成技术[M].成都:电子科技大学出版社,1995:140-147.

[2]姜萍,王建新,吉训生.FPGA实现的直接数字频率合成器[J].电子技术应用,2002,28(05):43-44.

[3]刘晨,王森章.直接数字频率合成器的设计及FPGA实现[J].微电子与计算机,2004,21(05):63-65.

[4]宋阳,孙肖子,仁爱锋.基于DDS和FPGA的虚拟智能信号源的研究[J].数据采集与处理,2001,16(专辑):124-126.