基于S5PV210的LCD转VGA技术研究

冯莉

摘 要 以VGA接口时序为标准,采用ARM芯片S5PV210为CPU,通过D/A 芯片 SDA7123的信号转换,实现了嵌入式系统领域LVDS转VGA的方案设计。系统的实现,一方面通过配置S5PV210芯片的LCD控制器,使得LVDS接口产生数字信号,另一方面通过 D/A 芯片SDA7123将数字信号转化为模拟信号,实现了VGA接口终端的正常视频显示。经验证,该方案对于800×600、1024×768等不同分辨率的视频信号,显示效果良好,并具有占用系统资源少,效率高,可靠性好的优点,适合在嵌入式应用领域广泛采用。

关键词 VGA;S5PV210;时序;视频D/A;LCD控制器;SDA7123

中图分类号 TP3 文献标识码 A 文章编号 1674-6708(2017)188-0078-04

目前许多嵌入式微处理器都集成了LCD控制器,如Samsung公司的S5PV210、S3C6410及Atmel公司的ATSAMA5D3系列处理器等。虽然可以方便的接大屏幕的LCD显示屏,但LCD显示屏价格昂贵。而PC端的液晶显示器,在日常生活中普遍存在,如果能够合理利用此资源来作为显示终端,不仅可以合理利用现有资源、节约系统成本而且体积小巧,便于携带。普通计算机的液晶显示器大都采用VGA接口作为标准信号输入接口,因此,本方案采用LVDS转VGA的方案设计来满足此要求。本方案通过分析VGA显示时序和LCD显示时序之间的关系,找到了问题的突破口,同时验证了方案的可行性。

1 VGA 接口

VGA(Video Graphics Array)视频图形阵列是IBM于1987年提出的一个使用模拟信号的显示标准。VGA接口共有15针,分成3排,每排5个孔,如图1所示。

VGA接口信号为模拟信号,它传输的主要信号分为红、绿、蓝模拟信号以及行同步信号和场同步信号。其引脚定义如表 1所示。

2 VGA时序与LCD时序分析

VGA的时序分为行时序和场时序。行时序如图2所示。

主要包括行总宽度、行消隐后肩(HBPD+1)、行消隐前肩(HFPD+1)、行同步脉冲(HSPW+1)、行显示时序段(HOZVAL+1),它们之间的关系为:

行总宽度 = (HBVD+1) + (HFPD+1) + (HSPW+1) + (HOZVAL+1)

行时序各部分的作用如下:

HBPD:确定行同步信号和行数据传输前的一段延时,描述行数据传输前延迟时间内VCLK脉冲个数;

HFPD:确定行数据传输完成后到下一行同步信号到来的一段延迟时间,描述行数据传输后延迟时间内VCLK脉冲个数;

HSPW:确定行同步时钟脉冲宽度,描述行同步脉冲宽度时间内VCLK脉冲个数;

HOZVAL:确定显示的水平方向尺寸。

场时序如图3所示。

主要包括场总宽度、场消隐后肩(VBPD+1)、场消隐前肩(VFPD+1)、场同步脉冲(VSPW+1)、场显示时序段(LIINEVAL+1),它们之间的关系为:

场总宽度 = (VBVD+1) + (VFPD+1) + (VSPW+1) + (LIINEVAL+1)

列时序各部分的作用如下:

VBPD:确定帧同步信号和帧数据传输前的一段延时,是帧数据传输前延迟时间和行同步时钟间隔宽度的比值;

VFPD:确定帧数据传输完成后到下一帧同步信号到来的一段延时,是帧数据传输后延迟时间和行同步时钟间隔宽度的比值;

VSPW:确定帧同步时钟脉冲宽度,是帧同步信号时钟宽度和行同步时钟间隔宽度的比值;

LINEVAL:确定显示的垂直方向尺寸。

典型的LCD时序图如图4所示,通过与VGA时序进行比较,可以发现LCD掃描时序和VGA时序很相似,这就为通过LCD控制器产生VGA所需时序信号提供了可能性,同时也为LVDS转VGA技术提供了理论依据。

要实现这种可能性,需要解决的问题主要有:

由于VGA接口的同步信号都是高电平有效而S5PV210的LCD接口同步信号是低电平有效,因此要解决两者的电平转换问题。

由于VGA接口的红绿蓝通道都为模拟量,而S5PV210的LCD控制器输出为RGB数字信号,为了解决信号不匹配的问题,必须通过D/A转换,将数字信号转换成模拟信号。

针对转换需求,本设计采用DS90CF364A芯片和D/A芯片SDA7123来解决此问题。

3 DS90CF364A和SDA7123芯片简介

DS90CF364A接收器可将4路LVDS数据流转换成并行的28位CMOS/TTL数据(24位RGB和4位Hsync、Vsync、DE及CNTL)。另外,DS90CF364A也可实现将3路LVDS数据流转换成并行的21位CMOS/TTL数据(18位RGB和3位Hsync、Vsync及DE)。这两种接收器的输出都采用下降沿选通。一个上升沿或下降沿选通发送器(DS90C383A/DS90C363A)可以和一个下降沿选通接收器在无任何传输逻辑的情况下互操作。

相比上一代产品,DS90CF364A的输出提供了一个更宽的数据有效时间,其结构框图如图5所示。

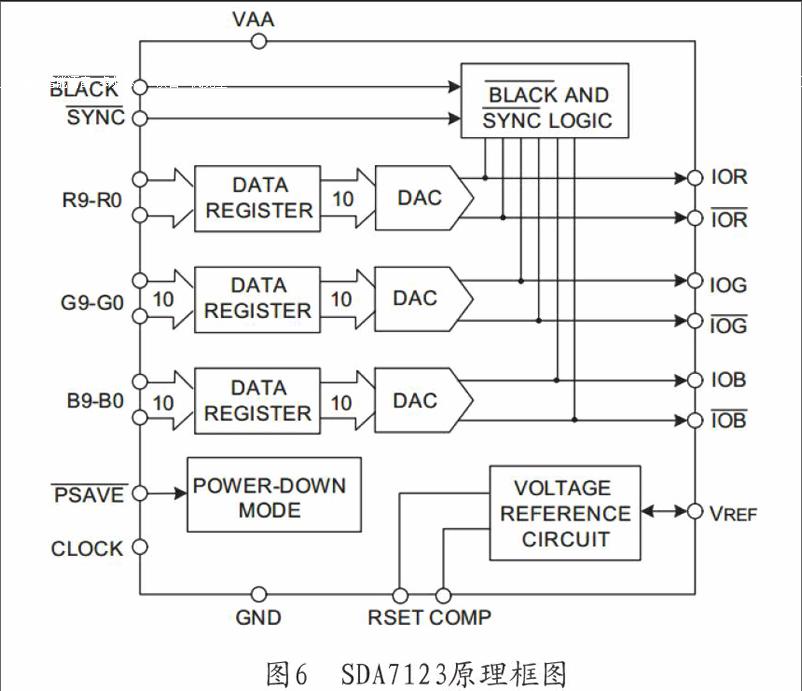

SDA7123是三路10位视频D/A转换器,分别完成R(红)、G(绿)、B(蓝)信号转换,电流型输出,绿通道可带同步信号输出。它的数据更新频率MSPS为140MHZ,SDA7123内带1.23V基准,工作温度范围宽(-40℃~+85℃)。适用于数字视频系统、图像处理、仪器、高精度显示器、视频信号重建等系统中,可与ADV7123替换使用。

其原理框图如图6所示。

SDA7123有三路独立的10位输入端口,可以在单电源5V下工作,也可以在单电源3.3V下工作。此外,SDA7123还有附加的两个视频控制信号:復合(同步信号)及(黑电平)。

4 LVDS转VGA接口电路设计

为了实现LVDS到VGA的转换,整体的硬件接口电路设计方法如下:

通过DS90CF364A芯片实现3路LVDS数据流到并行21位CMOS/TTL数据的转换;

DS90CF364A芯片转换后的21位CMOS/TTL数据中有18位属于RGB数据,将此18位数据作为SDA7123芯片的输入,最终完成LVDS到VGA接口的D/A转换设计。

该转换模块的结构框图如图7所示。

5 S5PV210芯片LCD相应控制寄存器设置

VGA输出支持多种分辨率显示模式,不同的分辨率显示模式对应的时序参数是不同的。因此,首先需要选定一个输出分辨率;其次就是配置相应的LCD控制器,以产生对应的时序参数。本方案采用PC作为显示输出端,多数厂商的PC显示器默认都支持分辨率VESA标准,因此本方案可以根据此标准来设置相应的LCD控制器参数,使得产生的VGA输出可以在大多数品牌厂商生产的PC端正常显示。

由于分辨率800×600、刷新频率为60Hz的VGA显示输出在一些品牌PC端并不能得到很好的支持,因此本方案选择分辨率1024×768、刷新频率为75Hz、16位彩色的VGA显示模式作为案例,来详细分析LCD相应控制寄存器的设置步骤。根据VESA标准,可以获得1024×768@75Hz下,行时序和场时序各部分的取值范围,其取值范围如表2所示。

下面根据表2的取值范围,来设置LCD相应的控制寄存器。首先声明,本案例的Src_clk (Frequency of Clock source)值为166 750 000Hz,因此,以下各个控制寄存器的取值都是在此基础上进行设置的。

VIDCON0寄存器。

CLKVAL_F:确定VCLK和CLKVAL[7:0]之间的比率。当CLKVAL>=1时,VCLK=HCLK/(CLKVAL+1)。

本方案的HCLK=166.75MHz,VCLK=Pixel Clock=78.75MHz,因此CLKVAL需设置为1。

L1_DATA16:选择间接i80接口(LDI1)数据输出格式模式,本设计采用的是16bpp模式,因此设置L1_DATA16=000.

L0_DATA16:选择间接i80接口(LDI0)数据输出格式模式,设置L0_DATA16=000,选择16位模式。

VIDTCON0寄存器。

VBPD:参考表2的数据可知,VBPD=(V Back Porch)/(Hor Total Time)=0.466ms/16.660us≈28;

VFPD:参考表2的数据可知,VBPD=(V Front Porch)/(Hor Total Time)=0.017ms/16.660us≈1;

VSPW:参考表2的数据可知,VSPW=(Ver Sync Time)/(Hor Total Time)=0.05ms/16.660us≈3;

VIDTCON1寄存器。

HBPD:由于VCLK=Pixel Clock=78.75MHz=12.6984ns,因此,参考表2的数据可知,HBPD=(H Back Porch)/(Pixel Clock)=2.235us/12.6984ns≈176;

HFPD:与上面类似,HFPD=(H Front Porch)/(Pixel Clock)=0.203us/12.6984ns≈16;

HSPW:与上面类似,HSPW=(Hor Sync Time)/(Pixel Clock)=1.219us/12.6984ns≈96;

VIDTCON2寄存器。

LINEVAL:由于本方案采用的是1024×768的分辨率,因此,LINEVAL=(Horizontal display size)-1=1023;

HOZVAL:HOZVAL=(Vertical display size)-1=767。

WINCON0寄存器。

BPPMODE_F:本方案采用的是16bpp(R:5-G:6-B:5)显示模式,因此,BPPMODE=5。

通过以上设计,就可以实现LVDS转VGA的信号输出。本方案的硬件电路采用透传模式,因此,只需设置好LCD控制器的相应寄存器,即可通过SDA7123的D/A转换,实现将视频或图片信息输出到VGA显示屏上。

6 测试

通过本方案设计的硬件电路,将S5PV210的LVDS接口和显示器的VGA接口连接起来,配置好相应的LCD控制寄存器,即可实现正常的视频或图片输出。显示图像如图8所示。

7 结论

本文提出了一种采用S5PV210的LCD控制器来实现VGA显示的方法。通过分析比较LCD接口时序与VGA接口时序的相同点,论证了LVDS转VGA接口的可行性。本设计通过配置LCD控制寄存器产生LVDS数字信号,然后通过DS90CF364A芯片将LVDS数字信号转换成TTL信号,最终通过视频D/A芯片SDA7123将TTL信号转换成VGA接口所需的模拟信号。实验结果表明,图像通过LVDS-VGA转换电路,在VGA接口的显示屏上,显示图像良好,可以满足广大普通用户的需求。该设计方案不仅成本低廉而且设置简单,适合有此需求的工程广泛采用。

参考文献

[1]韦东山.嵌入式Linux应用开发完全手册[M].北京:人民邮电出版社,2009:197-210.

[2]宋宝华.Linux设备驱动开发详解[M].2版.北京:人民邮电出版社,2014:440-443.

[3]王国裕,尹伟,张红升.嵌入式系统VGA显示驱动实现[J].电子世界,2014(10):454-455.

[4]方鹏,张红雨.基于ARM处理器S3C2440的VGA显示技术[J].电子设计工程,2011,19(11):174-176.