一种高灵活性HEVC帧内编码器前端设计

陆彦珩,王利鸣,曾晓洋,范益波

(复旦大学 微电子学院,上海 201203)

一种高灵活性HEVC帧内编码器前端设计

陆彦珩,王利鸣,曾晓洋,范益波

(复旦大学 微电子学院,上海 201203)

本文基于一种两级流水的高灵活性HEVC帧内编码器架构,完成了其前端设计,主要完成块大小划分和码率控制2个功能.针对这2个功能的算法优化,提出了一种基于梯度的帧内编码器块大小判决快速算法和一种低复杂度的码率控制算法,并最终用软硬件协同的方式将这两种算法在硬件中实现.

HEVC; 帧内编码器; 块大小划分; 码率控制

随着网络视频、视频会议等典型视频应用服务在我们日常生活中变得越发重要,视频压缩编解码技术也越来越受到人们的关注.针对更大的视频序列容量、更好的视频质量以及大分辨率视频序列,2013年国际电信组织(International Telecommunication Union, ITU)和运动图像专家组(Moving Picture Experts Group, MPEG)联合成立的JCT- VC(Joint Collaborative Team- Video Coding)组织提出的新一代视频编解码标准(High Efficiency Video Coding, HEVC),与上一代视频编码标准H.264/AVC相比,HEVC期望在相同视觉效果的前提下,码流比特率减少50%.与H.264相比,HEVC引入了多达5种可选宏块大小及35种帧内预测可选模式,大幅提高了编码效率,但与此同时也付出了4倍左右的计算复杂度代价[1].因此,低成本高性能的HEVC帧内编码器成为了当前的研究热点之一.

在HEVC正式发布之后的3年里,学术界和工业界提出了多个HEVC编码器设计方案.台湾的一个研究团队给出了一个强调性能的支持8K×4K视频的HEVC编码器设计方案[2],而日本电报电话公司抢先完成了世界上第一个单芯片422格式HEVC编码器的硬件实现并投入实用[3].中国大陆方面,清华大学与华为公司的联合研究团队给出了一个最高支持1080p@44fps实时编码要求的HEVC帧内编码器设计方案[4].这些既有的编码器设计方案往往针对特定的分辨率实现,且不具备根据视频图像特性改变编码器编码方案的能力.针对这一问题,本文给出了一种高灵活性HEVC帧内编码架构,编码器前端内嵌一个简易处理器,可根据视频特性及时改变编码策略.

编码器前端主要完成块大小划分和码率控制功能,通过软硬件协同的方式实现.由于HEVC标准引入了多达5种可选宏块大小,宏块划分部分成为了优化编码器计算复杂度的重要切入点.本文给出了一种基于梯度的块大小划分快速算法,以较小的性能代价换取巨大的计算量削减.码率控制算法较为灵活,适宜软件实现,考虑到硬件设计中采用的任务驱动型处理器(Event Driven Processor, EDP)性能较弱,本文给出了一种低复杂度的码率控制算法,以较小的计算量获得了满足要求的码率控制效果.

1 HEVC帧内编码器

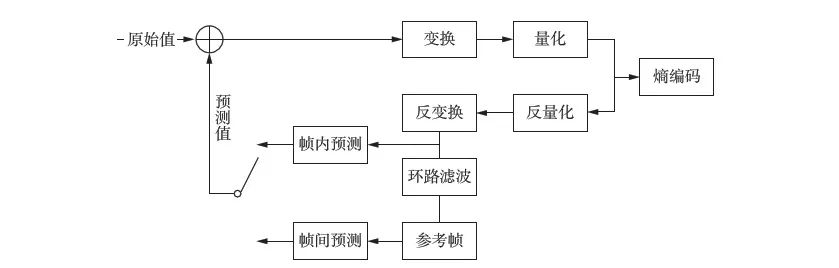

与H.264相似,HEVC也采用了基于块的混合编码架构,其基本架构如图1(见第90页)所示[1].输入的视频码流首先通过帧间预测或帧内预测得到当前图像的预测值,将原始值与预测值相减得到残差值,从而通过去除视频中空间冗余或时间冗余的方式大大压缩信息熵的大小.继而,HEVC采用变换和量化技术进一步压缩预测编码得到的残差信息.变换编码从频域的角度减小了残差值的空间冗余,达到压缩编码的目的.最后,HEVC采用熵编码对量化后的变换系数进行编码,得到最终的视频码流.

由于解码器无法获得视频原始图像信息,为保证编码端和解码端数据一致,编码器还需要对得到的残差系数进行反变换和反量化得到与解码端一致的重建图像.为了使得参考帧尽可能与原始值相似,HEVC还在帧间预测之前引入了环路滤波单元对重建图像进行处理,尽可能减小参考帧的失真.

帧内预测是通过邻近块参考像素值预测当前块像素值的预测方法.视频图像的邻近像素点之间往往存在千丝万缕的联系,帧内预测利用空间上的相关性预测当前块的像素值,从而达到消除图像中空间冗余的目的,大大提高了视频压缩比.只采用帧内预测方式进行编码的编码器称作帧内编码器.

图1 HEVC编码架构Fig.1 HEVC encoding architecture

由于帧内预测中每一个最大编码单元(Largest Coding Unit, LCU)都需要其左侧和上方LCU的重建像素值作为当前LCU的参考像素值,因而后一个LCU的帧内预测过程只能在前一个LCU完成整个编码过程后才能进行,大大降低了硬件编码器的吞吐率.为了解决这一问题,文献中提出了一个两级流水的高吞吐率HEVC帧内编码器架构: 第一级流水线使用原始像素值完成帧内预测模式判决和块大小划分,将获得的块大小划分方案及最优模式作为中间数据交给第二个流水级,继而第二个流水级使用中间数据重新依据原始像素和重建像素进行完整的帧内预测变换量化等过程,从而大大加快编码器的编码速度[5].

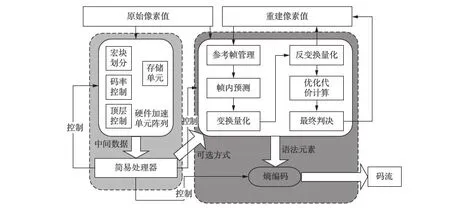

经过研究,我们进一步发展了上一段中介绍的文献[5]中的思想,在第一级流水线中引入一个简单的EDP,完成块大小划分(Part)、码率控制(Rate Control, RC)等编码任务,同时作为整个编码器的顶层控制(Ctrl).本文给出一个高灵活性HEVC帧内编码器架构如图2所示,简易处理器的引入大大提高了整个编码器设计的灵活性,可以针对待编码视频的图像特性选择合适的编码方式,从而提高整体编码效果.

图2 高灵活性HEVC帧内编码器架构Fig.2 Flexible HEVC intra encoder architecture

由于简易处理器性能有限,完成部分计算量较大的任务时需要引入硬件加速单元加快计算速度,通过软硬件协同的方式完成相应任务.本文接下来将基于这一帧内编码器架构,重点介绍编码器前端第一级流水线中块大小划分和码率控制两部分的算法及其实现.

2 帧内编码器块大小划分快速算法及实现

2.1块大小划分简介

帧内编码主要有帧内预测、变换量化和熵编码3个过程.输入的视频图像首先被划分为若干个LCU,每个LCU选择合适的块大小划分方案和预测模式进行预测编码,预测后得到的预测图像与原始图像相减得到残差图像,经过变换编码和熵编码后得到最终的码流.整个帧内编码流程固定,真正影响编码效果的是块大小划分方案与预测模式的选择.本文重点关注其中的块大小划分部分.

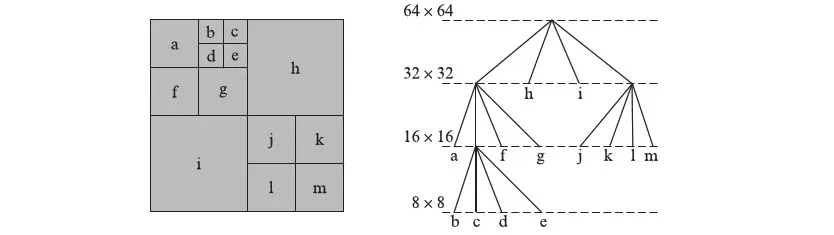

HEVC编码采用四叉树编码结构,基于编码单元(Coding Unit, CU)进行编码过程,基于预测单元(Prediction Unit, PU)进行预测过程,基于变换单元(Transformation Unit, TU)进行变换过程[6].编码时整个图像被分解为不同大小的编码树单元(Coding Tree Unit, CTU),采用YUV420格式时,每个CTU包括1个亮度宏块和2个色度宏块,亮度CTU大小可以为16×16、32×32或者64×64,色度宏块是亮度宏块大小的1/4.

一般而言,CTU直接作为LCU,但也可以作为LCU划分的根节点.CU块大小可以为64×64、32×32、16×16或者8×8,一个LCU划分四叉树的实例如图3所示,划分完成的CU按照如图3所示Z扫描方式依次进行编码.

图中a~m即为编码器编码时的顺序.图3 LCU划分实例及Z扫描方式Fig.3 LCU partition example and Z scan method

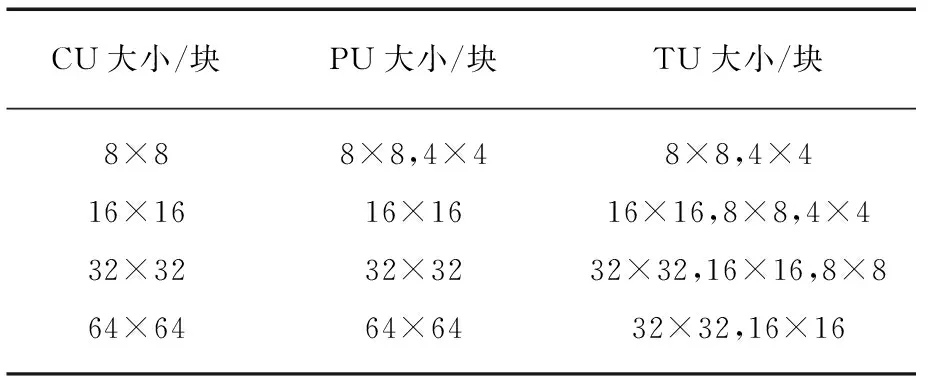

表1 不同CU大小下相对应的PU和TU大小范围

预测单元PU和变换单元TU均以CU作为四叉树根节点,彼此间互相独立.表1给出了不同CU情况下,PU和TU可选的块大小范围.PU作为预测单元,与帧内预测中的模式直接相关,其大小有4×4到64×64 5种.在帧内预测情况下,当CU块大小为16×16、32×32及64×64时,PU大小与CU大小一致;当CU大小为8×8时,PU可以为8×8,也可以为4×4[7].TU大小可以在CU大小基础上划分至多两级,考虑到大小为64×64的DCT变换计算量较大,TU大小被限定在4×4、8×8、16×16、32×32 4种.

由于HEVC标准中允许的块大小类型较多,如何在排列组合产生的众多块大小划分方式中挑选编码效果最好的划分方式成为了帧内编码算法中一个重要的课题.在官方给出的HEVC编码标准参考软件HM10.0中,帧内编码算法中的块大小划分过程通过迭代完成.对一个8×8块,首先计算出其优化结果,接着计算出其内部4×4块的优化结果,最后将4个4×4块的结果之和与该8×8块进行比较,将优化效果更好的结果作为当前8×8块的最终块大小划分结果.依次类推,可以得到16×16、32×32、64×64块的块大小划分结果,最终得到当前LCU的最优块大小划分方案.这样的算法固然可以获得最为精确的块大小划分结果,但运算量极大,不适合硬件实现.实际应用中,我们可以通过引入块大小划分快速算法的方式加快编码器的编码速度.

2.2帧内编码器块大小划分快速算法

梯度算法是一种较为常见的图像处理算法,主要用于检测图像局部显著性变化.梯度是一个代表图像灰度变化最快方向和数量的向量,表征当前像素点附近像素值变化的大致方向及剧烈程度.梯度值越大,则像素值变化越剧烈,当前图像纹理复杂度越高.

基于梯度算法思想,浙江大学的研究小组提出了一种帧内预测模式判决快速算法[8].他们通过sobel算子计算之后获得当前像素点在垂直水平方向上的梯度值Gx和Gy,将两者相除后进行arctan计算,从而获得当前像素点的梯度方向.使用这一梯度方向,即可以大致判断当前像素点附近图像变化情况,为选择最优角度模式提供帮助.

本文中提出的块大小划分快速算法基于类似思想实现,既然梯度算法可以通过检测图像局部显著性变化尝试判断帧内预测最优角度模式,那么也可以尝试着进行块大小划分判决.使用梯度算法判断块大小划分结果,不但可以大大加快块大小的划分速度,还可以借用帧内预测模式判决快速算法的中间结果,从而减少编码器整体的计算复杂度.

本文提出的块大小划分快速算法主要分为以下3步:

首先,在原始视频流中,把一帧图像划分为若干HEVC标准的LCU,将LCU内部可进行操作像素点的像素值按照sobel算子依据式(1)和式(2)分别进行X方向和Y方向上的梯度计算,得到当前像素点周边像素值的变化情况:

Gxi,j=Pi-1,j-1+2×Pi-1,j+Pi-1,j+1-Pi+1,j-1-2×Pi+1,j-Pi+1,j+1,

(1)

Gyi,j=Pi-1,j-1+2×Pi,j-1+Pi+1,j-1-Pi-1,j+1-2×Pi,j+1-Pi+1,j+1,

(2)

式中Pi,j代指不同像素点的数值.以当前PU左上角像素点为原点,视频图像水平向右方向为X轴正方向,垂直向下方向为Y轴正方向构建平面直角坐标系,则该坐标系中坐标为(i,j)点的像素值记作Pi,j.

接着,对某一个PU,将其中所有像素点的梯度值相加得到当前PU图像纹理的复杂程度,记作纹理复杂度K,其计算公式如式(3)所示:

K=∑(|Gx|+|Gy|).

(3)

纹理复杂度越大,则意味着当前PU内部变化较大,使用小块预测往往效果出众,而纹理复杂度越小,则意味着当前PU内部像素值变化较小,可选择使用大块进行预测.最后,依据纹理复杂度信息,得出最有可能的块大小划分方法.这里的判断可以根据经验阈值完成,下面给出一种基于经验阈值,从大块到小块依次判断的划分方法.

表2 一个可行的经验阈值方案

以64×64块为例,如果64×64块中每一个32×32子块的图像复杂度均小于某一阈值,则可认为这个64×64块内4个32×32块的图像复杂度均较低,不需要进行划分,此时选用64×64作为最有可能的块大小划分;若不满足,则将64×64块划分为4个32×32子块,并对4个32×32子块依次进行图像复杂度分析.依次类推,可以完成32×32、16×16、8×8块的划分选择,并最后得到最有可能的块大小划分方案.这里的经验阈值与图像特性相关,经过若干次的实验尝试,得到一个性能较好的经验阈值方案如表2所示.

综上所述,通过引入梯度计算,我们可以快速获得当前PU图像的纹理复杂度,将获得的纹理复杂度值与经验阈值进行比较,从而获得当前PU的块大小划分结果,完成当前块的块大小划分任务.

在实际编码器硬件设计中,纹理复杂度计算部分与帧内预测模式判决快速算法计算过程类似,可由硬件加速单元完成并作为中间数据提交给内嵌简易处理器.本文中提出的块大小划分快速算法主体部分以软件代码的形式在简易处理器中执行,这也就意味着,上文中的经验阈值可以根据图像特性快速进行更新,力图获得更好的编码效果,这也是高灵活性帧内编码器的一个重要优点.

使用本文算法和HM10.0分别对Cactus视频进行编码,得到其左上部分的CU块大小划分结果(图4).可以看出两者得出的块大小划分方案较为一致,只是在划分较为复杂的图像块时本文算法折中选择了中间大小的块(16×16块),保证即便未能选取最优块大小划分方案,也不至于出现过大的编码性能损失.

图4 CU块划分效果对比Fig.4 Comparison of the effects of CU partition

2.3编码性能测试及分析

为了验证本文中提出的块大小划分快速算法的编码性能,我们在官方给出的HM参考程序基础上实现了该算法,使用的参考程序版本为HM10.0.

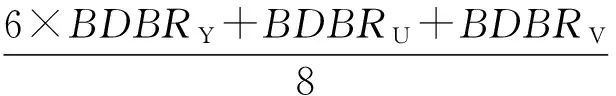

本文测试了HEVC官方给出的4种不同分辨率下的15个测试序列,每一组序列在22,27,32,37共4种QP取值情况下各编码30帧.在这里,我们以参考软件HM编码结果为基准,通过拟合获得在同等编码质量情况(Peak Signal to Noise Ratio, PSNR)下,编码后码率大小的增大幅度,记作联合比特率(Bjontegaard Delta Bie Rate, BDBR),作为编码性能的比较标准.考虑到亮度色度分量权重不一,我们引出如式(4)所示的BDBR作为度量Y、U、V 3个分量总体性能损失的标准[9]:

(4)

表3 本文算法的编码性能

算法编码性能测试结果如表3所示,由于编码时间直接相关于测试服务器性能,编码器计算量的下降可以通过编码时间的百分比减少体现.

由实验结果可以看出本文提出的块大小划分快速算法可以大大提高HEVC帧内编码器的编码速度,平均可以减少56.56%的编码时间,针对Kimono视频时甚至可以将编码时间削减67.24%,相当于将编码速度提升了3倍.本算法针对不同视频流编码速度梯度效果相差较大,这与块大小划分方案有关.如果最终获得的块大小划分方案中大块较多,编码速度相对较快,反之若小块较多,编码速度相对较慢,速度提升也就较小.

与此同时,由于快速算法往往不能锁定最优的块大小划分方案,因而它的引入不可避免地造成了一些编码性能的损失,15个码流平均BDBRYUV为11.54%.特别是对小尺寸视频,编码性能损失尤其巨大.这是因为小尺寸视频中小块特别是8×8和4×4块数量较多,而本文提出的算法面对较小的PU块时判断效果较差,往往不能给出正确的判决结果,导致小尺寸视频编码性能损失较大,这也是本文提出的快速算法未来可以进一步提高的地方.

3 码率控制算法及实现

3.1码率控制简介

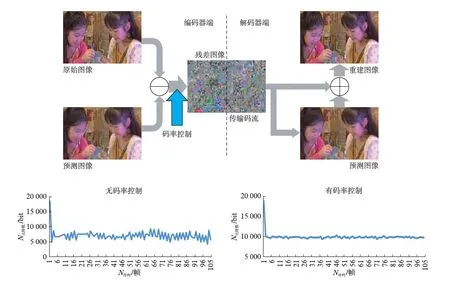

视频编码的目的是为了在有限的信道带宽中传输尽可能多的信息,而码率控制就是用于实现对编码后视频码流大小的调整控制,使之符合视频传输需求.图5给出了一个码率控制的实例,没有经过码率控制的编码结果每一帧的帧率浮动变化剧烈,而经过码率控制之后视频码流明显平顺,适宜无线传输.

图5 码率控制简介Fig.5 Introduction of the rate control

在HEVC视频编码标准中,对编码后码流大小起决定性作用的参数是量化参数(Quantization Parameter, QP).对同一幅图像,QP越大就意味着量化中截取的有效信息越少,此时经过编码之后的码流也会相应减少,解码后的图像质量相应变差.因此,通过改变编码时的量化参数QP值,我们就可以对码流大小进行一定的控制.

3.2低复杂度码率控制算法

本次设计的帧内编码器面向视频监控领域,需要实时传输数据,因而希望码率相对平缓,每一帧编码后码流的比特数都在目标比特数附近.由于本次设计中使用的简易处理器性能有限,当前流行的基于R-λ模型的码率控制算法运算量较大无法实现[10],因此本文中提出了一种低复杂度的码率控制方案.该算法分为帧级和宏块级两部分,帧级算法将码率大致控制在目标码率附近,继而通过宏块级码率控制算法进一步精确控制码率.

帧级码率控制通过比较前一帧编码码率结果及目标码率完成.由于第一帧没有可供参考的数据,其帧级QP直接取常用QP的中间值32.继而假定前一帧的码率为B0,目标码率为B,若满足:

|1-B0/B| (5) 则可认为帧级QP较为合理,不需要进行调整.式(5)中c为经验常数,一般可取0.1. 如果式(5)不满足,则需要对帧级QP进行调整.若此时不处于视频序列的前5帧,则考虑前后帧画面清晰度不宜出现较大幅度的变化,若前一帧比特数过大,则后一帧帧级QP增加1,反之,帧级QP减少1.如果当前帧处在视频序列的前5帧,则可认为此时尚未找到合适的QP值,此时最多可在前一帧帧级QP的基础上按B0与B的商进行上下幅度为5的调整,以求迅速找到合适的帧级QP. LCU级码率控制的算法思想与帧级类似.假定前一帧存在N个LCU,每一个LCU编码完成后的比特数存在放在数组B0[N]中,当前帧已经编码完的码流大小为B1[N]. 首先,对前一帧码流大小数组按式(6)进行修正获得当前理想的码流大小B2[n]: B2[n]=B0[n]×B/B0. (6) 接着,将对应的B1[n]与B2[n]作差,如果差值大于c1,则将LCU级QP在帧级QP基础上作幅度为1的浮动,若差值大于c2,则可作幅度为2的浮动.一般情况下,c1在100附近,c2取值在300上下,具体取值根据视频特性决定.考虑到同一帧内图像清晰度变化不能过于明显,LCU级QP控制在当前帧帧级QP上下大小为2的幅度之内. 最后,由于编码器限制QP范围必须限定在[10,51]范围内,如果超出范围需要将QP重新设定在允许范围的边界上.需要注意的是,由于第一帧没有可参考的比特数信息,故第一帧不进行LCU级码率控制,由于帧内编码器硬件中LCU级码率控制处于流水线第一级,因此每一帧前5个LCU进行QP计算时第一个LCU还未编码完成,因此每一帧前5个LCU也不进行QP计算. 与块大小划分部分类似,我们同样采用软硬件协同的方式实现码率控制算法.硬件部分较为简单,主要用于统计编码码流大小并将中间数据打包送给EDP.算法主体部分通过EDP软件实现,算法中的经验参数c、c1、c2可以根据待编码视频的特性及编码结果,通过重新导入程序的方式进行更改,从而获得更好的码率控制效果. 3.3实验结果及性能分析 图6 码率控制算法性能测试结果Fig.6 Experiment result of the rate control algorithm 本文给出的码率控制算法通过软件实现后进行了性能测试,测试序列为官方给出的Kinomo视频片段,图像分辨率为1080p(1920×1080),每帧图像编码后码流的目标比特数为60000bit,这里使用的阈值参数c取0.1,c1取100,c2取300.使用帧内编码器对测试序列编码100帧获得的算法性能测试结果如图6所示. 由于未对第一帧作过多限制,第一帧视频比特数明显大于目标比特数,但通过码率控制算法,编码后视频每一帧的比特数很快被限制在了目标比特数附近,并长期稳定地保持了下去.虽然每一帧码流的比特数略有波动,但总体起伏较小,与目标比特数的差最大不超过百分之一,满足编码器实际需求. 本文给出了一个高灵活性HEVC帧内编码器前端设计,完成码率控制和块大小判决两个功能.提出了一种基于梯度的块大小划分快速算法和一种低复杂度的码率控制算法,使用软硬件协同的方式实现了这两种算法并给出了测试结果和性能分析. [1] BROSS B, HAN W J, SULLIVAN G J,etal. High efficiency video coding(HEVC) text specification draft 10 (JCTVC- L1003)[C]∥JCT- VC Meeting (Joint Collaborative Team of ISO/IEC MPEG & ITU- T VCEG). Geneva, Switzerland: JCTVC Press,2013. [2] TSAI S F, LI C T, CHEN H H,etal. A 1062Mpixels/s 8192×4320p high efficiency video coding(H.265) encoder chip[C]∥Symposium on VLSI Circuits. Kyoto, Japan: IEEE Press, 2013: C188- C189. [3] ONISHI T, SANO T, NISHIDA Y,etal. Single- chip 4K 60fps 4∶2∶2 HEVC video encoder LSI with 8K scalability[C]∥Symposium on VLSI Circuits. Kyoto, Japan: IEEE Press, 2015: C54- C55. [4] ZHU J, LIU Z, WANG D,etal. HDTV1080p HEVC Intra encoder with source texture based CU/PU mode pre- decision[C]∥2014 19th Asia and South Pacific Design Automation Conference (ASP- DAC). Suntec, Singapore: IEEE Press, 2014: 367- 372. [5] LIU C, SHEN W, MA T,etal. A highly pipelined VLSI architecture for all modes and block sizes intra prediction in HEVC encoder[C]∥2013 IEEE 10th International Conference on ASIC(ASICON). Shenzhen, Guangdong, China: IEEE Press, 2013: 1- 4. [6] KIM I K, MIN J, LEE T,etal. Block partitioning structure in the HEVC standard[J].IEEETransactionsonCircuitsandSystemsforVideoTechnology, 2012,22(12): 1697- 1706. [7] SULLIVAN G J, OHM J, HAN W J,etal. Overview of the high efficiency video coding (HEVC) standard[J].IEEETransactionsonCircuitsandSystemsforVideoTechnology, 2012,22(12): 1649- 1668. [8] JIANG W, MA H, CHEN Y. Gradient based fast mode decision algorithm for intra prediction in HEVC[C]∥2012 2nd International Conference on Consumer Electronics, Communications and Networks (CECNet). Yichang, Hubei, China: IEEE Press, 2012: 1836- 1840. [9] BJONTEGAARD G. Calcuation of average PSNR differences between RD- curves[C]∥Doc. VCEG- M33 ITU- T Q6/16. Austin, TX, USA: ITU- T VCEG Press, 2001. [10] LI B, LI H, LI L,etal. Rate control by R- lambda model for HEVC[C]∥ITU- T SG16 Contribution, JCTVC- K0103. Shanghai, China: [S.L.]. 2012,: 1- 13. Abstract: A flexible HEVC intra encoder frontend design is proposed based on a two- level pipeline encoder architecture. A gradient- based fast CU partition algorithm and a low complexity rate control algorithm are also proposed for HEVC intra encoder in this paper. The two algorithms are implemented in our hardwired encoder design by hardware and software cooperation. Keywords: HEVC; intra encoder; block size partition; rate control DesignofAFlexibleHEVCIntraEncoderFrontend LU Yanheng, WANG Liming, ZENG Xiaoyang, FAN Yibo (DepartmentofMicroelectronic,FudanUniversity,Shanghai201203,China) TP36;TN37;TP33 A 0427- 7104(2017)01- 0089- 08 2016- 05- 22 国家自然科学基金(61306023) 陆彦珩(1992—),男,硕士研究生;范益波,男,副教授,通信联系人,E- mail: fanyibo@fudan.edu.cn.

4 结 语