3D立体封装(芯片)的结构技术

李振华+杨宁+刘小刚

摘要:芯片立体封装技术日渐成熟,主要应用于电子产品中。本文对集成电路的3D立体封装的结构类型进行了介绍,着重介绍了3D层叠封装的结构,多层基板芯片封装技术,MCM-3D封装结构技术,并且对3D立体封装芯片的结构技术有了概览性的认识和把握,对进一步掌握芯片的封装技术的实践打下了理论基础。

关键词:3D立体封装;集成电路;层叠封装;多层基板封装

前言

IC封装业作为支持电子信息产业发展的关键技术之一[1]。其主流技术正在向高速、多功能、低功耗、窄间距、小型化、轻量化和低成本的方向发展。3D封装技术正处于发展阶段,未来使3D封装技术尽快地取得工艺上重大的突破,并得以更为广泛的应用。

1.3D立体封装(芯片)的的结构类型

集成电路的3D立体封装主要有三种类型:埋置型,有源基板型,和叠层型封装[2]。

埋置型3D芯片封装是一种将在各类基板内或者多层布线介质层中埋置元器件,最上层再贴装SMC/SMD来实现立体封装。

二是硅圆片规模集成(WSI)的活性基底后,再实施多层布线,最上面的一层,然后安装SMC/SMD,然后构成一个三维封装,称为有源基板型3D。

叠层型3D封装是一种金字塔型叠层封装,即用大小不同的芯片,上层的芯片的面积要小于下层,这样下层芯片表面就有足够的面积和空间可以用来进行引线键合。

2.3D层叠封装的结构

叠层3D软件是应用最广泛的一种,它的基本结构是一个裸芯片或封装堆叠起来的,不可能有中间夹层或夹层,夹层可多层PCB板(包括或不包括被动元件),每层可连接线焊接,倒装芯片,它也是通过孔直接互连(TSV)。三维叠层封装是近年来迅速发展起来的一种集成封装技术[3-4]。

常见的芯片叠层封装多是把两个或两个以上的芯片在Z方向上堆叠,传统的引线键合方法用于互连和封装。使用相同尺寸的芯片,通过在上下层芯片之间加入一层芯片(spacer)以便于下层芯片的引线键合,垫片通常是一块面积比上下层芯片小的普通硅片。多芯片叠层封装的垂直互连问题,主要有以下几种方法:

尽管芯片叠层封装可在超薄的空间内集成更多的功能,甚至是某个系统功能(SoC),但是在一些集成电路中内由于良品率的影响和缺乏已知合格芯片KGD,在封装芯片的过程中,必须进行三维结构下的预测试。为此,业界在一个单一的解决方案中引入了一组预测试包,即堆叠包。堆叠的包可分为两种形式:内封装(PIP)和外封装(POP)。

封装内封装它堆叠在基本组件包的顶部,然后对内部堆叠模块进行完全测试,形成CSP解决方案。PIP封装技术是一种小型存储卡的集成封装技术。该技术集成了pcb基板组装和半导体封装的过程。此包具有较低的配置文件,可以堆叠在功能包中,引线框架和基板类型包都可以在POP包中實现[5]。该基板封装封装密度高,封装形状更薄,工艺灵活性更高,同时可靠性更高。PoP封装技术的出现,更加丰富了3D叠层封装的形式。

3.多层基板芯片封装技术

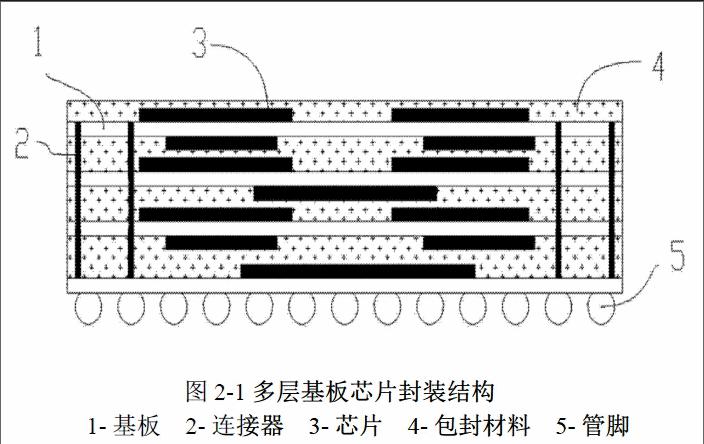

多层基板芯片封装是一种集成电路的3D封装结构,其包括多层基板,所述多层基板堆叠并通过连接器或金属针脚电性连接,所述基板上设置有一个或多个芯片和导体线路[6]。本实用新型通过多层基板堆叠结构,并通过连接器或金属针脚连接,使得3D封装结构满足高密度、高性能、低成本的要求,并克服了现有技术中存在的互连金线长、空间利用率小、工艺要求高或成本高的缺点,具有良好的社会和经济效益。本实用新型可广泛应用于各种集成电路的封装。

1.一种集成电路的3D封装结构,其特征在于:其包括多层基板,所述多层基板堆叠并通过连接器或金属针脚电性连接,所述基板上设置有一个或多个芯片和导体线路。

2.这是一种集成电路的3D封装结构,其特征在于:所述基板的上表面和下表面均设置有一个或多个芯片。

3.这种集成电路的3D封装结构,其特征在于:所述多层基板堆叠后,位于最下层的基板的下表面具有多个工I0管脚。

4.这种集成电路的3D封装结构,其特征在于:其整个结构采用塑封包封材料填充并包封,所述工I0管脚从塑封包封材料扇出。

5.要求3或4所述的一种集成电路的3D封装结构,其特征在于:所述工0管脚为BGA封装工I0管脚或LGA封装工I0管脚。

6.根据权利要求1至4任一项所述的一种集成电路的3D封装结构,其特征在于:其特征在于多层基板通过多个金属插脚堆叠并电连接[7-8]。

图2-1多层基板芯片封装结构

1-基板 2-连接器 3-芯片 4-包封材料 5-管脚

4.MCM-3D封装结构技术

该一种集成电路MCM-3D封装结构,其特征在于框架的框架载体的一个位置上依次堆叠放置第一芯片以及第二芯片,在框架载体的另一个位置上放置第三芯片。该集成电路MCM-3D封装结构用于直流转直流集成电路能满足电子产品市场对于高电压、大电流、体积小、效率高的优点。从电路设计方面的优越性从先天上提高了电路的输出电流等性能参数。采用Mos管外置的方式,摆脱内置元器件先天的缺陷,可以采用更大功率的MOS管。

从封装设计方面,采用先进的MCM-3D封装,在圆片磨片工序,使用超薄减薄技术减薄芯片,将芯片厚度减薄到200um以下,一方面有利于封装的需要,另一方面也提高了元器件的散热性能。在装片工序,使用装片膜在芯片上叠装芯片(3D),大大提高了装片的效率。装片完成后,相比较平面多芯片封装,3D封装因芯片间的距离较短,可以节省键合材料,节省成本,同时因键合丝的距离更短,整个封装体的内阻等更小,输出电流增大、输出功率增大,提高了产品的使用性能。

5.结论

3D封装技术改善了电子系统的许多方面,比如能耗,重量,尺寸等。具有高性能的封装的集成电路也广泛应用于航空航天、军事及民用电子等诸多领域。采用3D封装技术制作的高性能大容量的存储器组件是3D封装技术的主要应用领域之一。有诸多相关的专业研究介绍了3D层叠封装的结构,多层基板芯片封装技术,MCM-3D封装结构技术等。因此,对3D立体封装芯片的结构技术有了整体性的认识和把握,为理论和实践学习相结合打下了基础。

参考文献

[1]杨建生,YANGJian-sheng.BGA多芯片组件及三维立体封装(3D)技术[J].电子与封装,2003,3(1):34-38.

[2]吴燕红,徐高卫,罗乐.三维多芯片封装模块和制作方法[C]//2008.

[3]吴燕红,徐高卫,罗乐.三维多芯片封装模块和制作方法[J].2008.

[4]徐高卫,吴燕红,周健,等.基于埋置式基板的3D-MCM封装结构的研制[J].半导体学报,2008,29(9):1837-1842.

[5]刘瑶风.大容量立体封装存储芯片的应用[J].科技广场,2016(7):63-68.endprint