同位控制猝发总线设计与实现

黄志钢,张芝威

(沈阳理工大学 自动化与电气工程学院,沈阳 110159)

同位控制猝发总线设计与实现

黄志钢,张芝威

(沈阳理工大学 自动化与电气工程学院,沈阳 110159)

提出了一种同位控制猝发总线( LCBBus,Local Control Burst Bus),通过对目前已有的处理器与存储器之间总线信号的研究,设法使读写控制信号与数据信号同地点发出,同方向传输,同地点接收,大幅度缩短数据信号与控制信号的传输路径差以及时间差,提高猝发传送主频。在FPGA上用Verilog语言编写完成了该总线的逻辑设计,并且通过Modelsim SE对其进行了总线读写操作的仿真,证明了可行性。

同位控制猝发总线;FPGA;Verilog;Modelsim SE;猝发

通过对经典总线信号的研究,可知总线信号由:数据信号、控制信号和地址信号三大部分组成[1-2],且经典猝发总线的写操作时,写控制信号和数据信号同在CPU(中央处理器)处产生,同在Mem(存储器)处接收[3],即同源同方向同路径传输,而经典猝发总线的读操作时,读控制信号在CPU处产生,存储器获得控制信号后,发出数据信号,其控制信号和数据信号处于异位。因此数据传输比控制信号传输延迟一个时钟周期,影响传送主频。

为提高猝发传送主频,从控制信号与数据信号传输地点和方向入手,在不考虑CPU内部和存储器内部的传输时间;也不考虑猝发操作时,首地址设定所需的时间条件下,仅研究总线传输动作及其所需时间。并提出同位控制猝发总线(LCBB,Local Control Burst Bus),使得猝发传输时,控制信号和数据信号同源同方向同路径传输,通过运用Verilog语言对所设计的总线进行逻辑编写,并且通过Modelsim SE对其进行了总线读写操作的仿真。

1 经典猝发总线分析

经典猝发总线的写操作:写控制信号和数据信号同在CPU处产生,同在存储器处接收,即同源同方向同路径传输。写信号(WR)上升沿驱使存储器锁存数据总线(DB)上的数据到数据锁存器,写正确的条件是,写信号上升沿处,数据总线上的数据是有效的。记数据传输时间是TLD,写信号传输时间是TLWR,它们之间由于路径差产生的时间差是ΔT=|TLD-TLWR|。为确保写正确,要求写信号上升沿必须处在数据稳定区内,并留有大于正负ΔT的裕度。若忽略存储器将数据锁存存储器单元的需要时间,从总线角度看,允许的最大写主频为1/(2ΔT)。

经典猝发总线的读操作:读控制信号(RD)在CPU处产生,存储器获得读控制信号为低电平后,发出数据信号,CPU在数据信号稳定后锁存数据信号并撤销读控制信号。控制信号和数据信号处于异位。读正确的条件是,CPU锁存时,数据总线上的数据是有效的。控制源信号经TL时间传送到存储器中,存储器产生数据源,再经过TL时间送到CPU。为确保读正确,要求读控制信号必须处在数据稳定区内。从总线角度看,允许的最大读主频为1/(2TL)[4],图1为经典猝发总线的时序写、读图。

由此可见,多核处理器中,各核到各存储器的总线长度不尽相同[5],如果全系统使用同一个时钟,同一个延时,那么只能按照最坏的情况设定较低的系统主频。

2 同位控制猝发总线设计

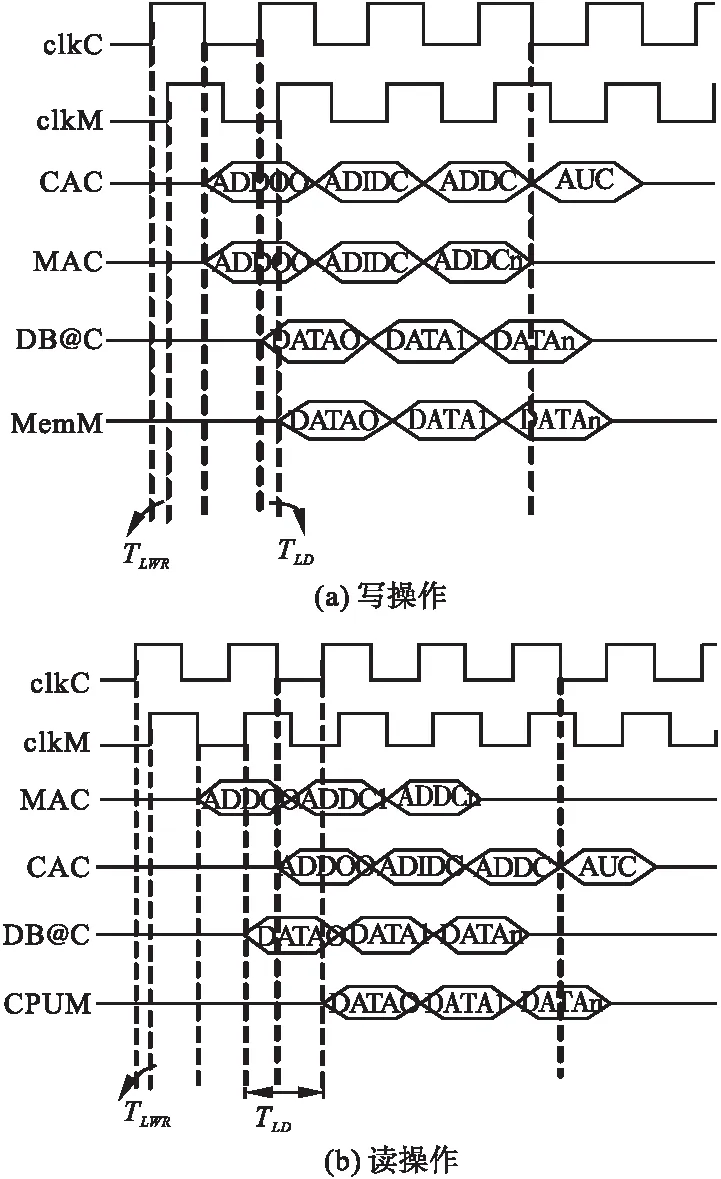

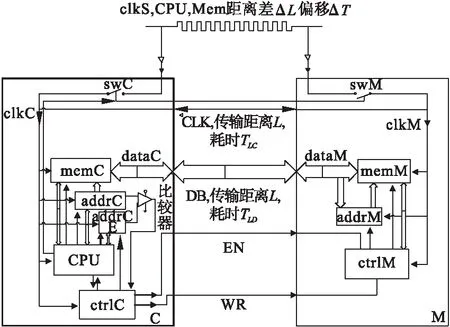

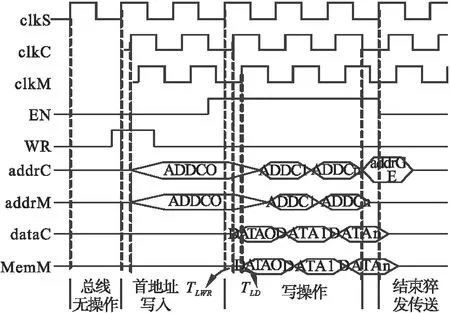

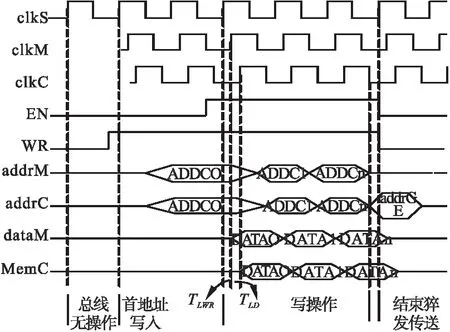

在同位控制猝发总线中,动态信号在每个时钟都发生变化;静态信号在一次猝发传送过程中不变化。为了提高猝发传送速度,使存储器操作时的控制信号和数据信号同位,写操作时控制和数据信号从CPU发出,读操作时控制和数据信号从存储器发出,称这种总线为同位控制猝发总线,如图2所示,其总线时序如图3和图4所示。

图1 经典猝发总线时序写、读图

图2 同位控制猝发总线信号原理图

图2中:clkS,系统时钟;clkC/clkM,处理器/存储器时钟,根据swC/swM不同,对应的选择CPU还是存储器时钟;swC/swM,处理器/存储器时钟选择开关;EN、WR,单向使能线、静态信号,有四个状态分别是:“00”,“01”,“10”,“11”;DB,数据总线,双向动态信号,传输地址和数据;memC,CPU的储器;memM,存储器的存储器;addrC/addrM,处理器/存储器地址及计数器。

图3 同位控制猝发总线理想时序写操作图

图4 同位控制猝发总线理想时序读操作图

CPU要开始一块猝发传送,需要使addrC⟹CPU传送首地址,addrCE⟹CPU传送末地址,addrM⟹存储器接收首地址。EN,WR=00时,总线无操作;EN,WR=01时,首地址写,首地址⟹db,db⟹ addrM;EN,WR=10时,写操作swC,swM=up,down;clkS⟹ clkC ⟹clkM。每个CLK,MemM(addrM)⟹MemC(addrC);EN,WR=11时,读操作swC,swM=down,up;clkS⟹ clkM ⟹clkC。每个CLK,MemC(addrC) ⟹ MemM(addrM);EN=1时,每个CLK,addrC+1,addrM+1。如果addrC=addrCE,则EN,WR=00,结束本次猝发传送。使得控制信号与数据信号同地点发出,同方向传输,同地点接收。

3 实现与仿真

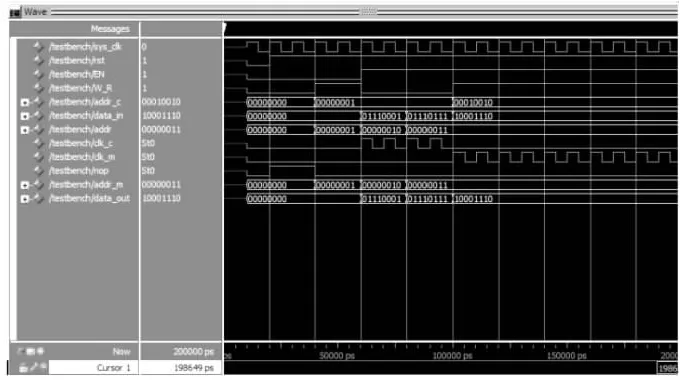

设计的总线通过改变读、写信号的位置,从而改变CPU间控制信号和数据传输方向。同理,对于多核处理器,随着核数挂在总线上的位置不同,存储器共用核的个数不同,传输信号、数据时间也会发生不同改变,但是由于控制信号和数据信号总是同方向的,所以对于内部传输而言,时间依然是ΔT。而总体的时间只与它们之间的路程差有关。由于本文时间仿真需要设计到板图阶段,才能得出相应的结论,小规模设计时,ΔT不明显,所以本文只对同位控制猝发总线的读写使用Modelsim SE进行逻辑功能仿真验证,仿真结果如图5所示。

图5 同位控制的仿真结果

4 结论

通过分析经典猝发总线的读写时序,其读操作时的读控制信号与数据信号处于异位而产生了传送时间差2TL,该时间差限制了猝发操作的最高频率。为此提出了同位控制猝发总线,使读控制信号与数据信号同地点发出,同方向传输,同地点接收,节省时间2TL。

经过Modelsim SE仿真,验证了同位控制猝发总线读写的逻辑可行性。通过改变猝发读、写信号的位置,从而缩短数据信号与控制信号到达目的地的时间,减少TL对该CPU的时钟频率的限制,既大幅度降低对时钟倾斜的敏感度,又大幅度提高猝发传送的主频。本文只对单核总线读写进行了仿真,并没有对多核进行仿真,但是在多核处理器为主导的今天,同位控制猝发总线发展前景十分明朗。

[1] 王明磊.基于PCI总线信号数字复接系统[D].长沙:国防科学技术大学,2004.

[2] 尚利.PIC结构[M].刘辉译.北京:电子工业出版社,2012.

[3] 黄志钢,盛肖炜.多核处理器结构与核间通信的CMC总线设计[J].沈阳理工大学学报,2012,31(6):70-75.

[4] Miguel Correia,Jorge Sousa,álvaro Combo,et al.Implementation of IEEE-1588 timing and synchronization for ATCA control and data acquisition systems[J].Fusion Engineering and Design,2012,87(12):2178-2181.

[5] 汪键,张磊,王少轩,等.多核处理器核间高速通讯架构的研究[J].电子与封装,2011,11(6):43-44.

(责任编辑:马金发)

TheDesignandImplementationoftheLocalControlBurstBus

HUANG Zhigang,ZHANG Zhiwei

(Shenyang Ligong University,Shenyang 110159,China)

A Local Control Burst Bus based on the research of the currently existing Bus signal between the processor and memory is proposed to reduce the Data signals and Control signals transmission′s path difference and time difference greatly by making a Read/Write Control signals and Data signals to send with same sites,to transmit with same direction and to receive with same sites.Finally,the burst transmission frequency is improved.Using Verilog language on FPGA completed the Bus logical design and through the Modelsim SE simulation of Reading and Writing operations on the Bus the feasibility is proved.

local control burst bus;FPGA;Verilog;Modelsim SE;burst

TP336

A

2016-11-16

黄志钢(1960—),男,副教授,研究方向:计算机控制系统,嵌入式系统。

1003-1251(2017)05-0011-03