基于FPGA的自顶向下乘法器电路设计

陈楚+吕石磊+孙道宗+刁寅亮

摘要:自顶向下电路设计方法是FPGA电路设计的重要内容,和传统的电子产品设计方法有很大区别,主要是通过EDA软件对电路设计文件进行相关处理,最终实现专用集成电路的设计。本文结合移位相加型乘法器实际例子介绍了两种电路设计输入方式,纯文本输入利用硬件描述语言对底层元件和顶层文件的电路功能进行描述;文本和原理图混合输入对电路的底层元件进行硬件描述语言描述,而顶层文件则采用原理图输入方式来实现。对两种输入方式的仿真波形进行分析,论证了设计方法的正确性,说明了两种输入方式的特点。

关键词:自顶向下;硬件描述语言;文本输入;原理图输入;乘法器

中图分类号:TN79 文献标识码:A 文章编号:1007-9416(2017)11-0165-02

FPGA全称是现场可编程门阵列(Field Programmable Gate Array),可以通过软件的方式实现数字逻辑电路设计[1],在传统数字电路系统设计内容的基础上,增加了一系列的知识点。FPGA的用途比较广泛,本文是利用FPGA进行乘法器电路设计,实现专用集成电路(ASIC)的功能。

在传统的电子产品设计过程当中,重点是设计电路的结构,涉及到原理图设计、布线、焊接、調试,整个过程需要付出很长的时间,一旦电路需要调整,必须重新进行一遍之前的步骤,增加了额外的成本和时间。

而采用可编程逻辑器件对电路进行设计,重点是关心电路的功能,采用硬件描述语言(HDL)描述或者输入原理图等方式来进行电路设计。通过EDA软件对设计好的文本或者原理图文件进行编译、综合、适配、再编译,生成对应的电路网表文件,最后通过下载电缆配置到可编程逻辑器件芯片,该芯片就具有了设计者预期的功能。如果设计好的电路系统通过现场测试后,发现功能错误或者不理想,只需要在普通电脑上运行EDA软件对设计文件进行修改[2],重新编译,生成新的网表文件,重新配置到可编程逻辑器件芯片,直至芯片功能满足设计要求。上述采用可编程逻辑器件进行电路设计的过程称为自顶向下的电路设计技术。

相对于传统的电子产品设计过程,自顶向下的电路设计思路通过修改设计文件就可以改变电路功能,因而具有设计周期短、节约成本、灵活性强、可靠性高等优点。

1 自顶向下电路设计方法分类

自顶向下电路设计主要有纯文本输入、文本和原理图混合输入两种方式。纯文本方式是指利用硬件描述语言(HDL)描述硬件电路的功能[3],即通过写代码的方式来描述芯片(ASIC)功能;而原理图输入方式是指设计完成电路原理图之后,利用EDA软件自带或用户自定义的元件库,按照电路原理图进行连接,侧重于电路结构的描述。在有的情况下,底层文件用硬件描述语言描述,由底层文件创建相应的底层元件,然后采用原理图输入方式进行顶层文件的设计,在顶层文件中调用已创建的底层元件,这种输入方式称为文本和原理图混合输入方式。

1.1 纯文本输入方式

目前官方标准的硬件描述语言有两大类,一类是VHDL语言,另外一类是Verilog HDL语言。本文采用VHDL语言来进行电路设计[4],实现纯文本输入;EDA软件采用Altera公司开发的QuartusII,利用该软件进行电路设计的输入。

自顶向下电路设计的技术思路是根据电子产品的说明书抽象出电路的功能,用自然语言描述,接着利用VHDL语言来描述电路的功能。在设计过程当中,需要把一个复杂的系统划分为多个简单模块,这些模块也可以继续划分为规模更小的模块。可见在自顶向下电路设计过程当中,顶层文件是由多个底层元件组合连接而成。

1.1.1 电路工作原理

本文以移位相加型6位乘法器为例子来说明自顶向下的电路设计思路[5]。两个6位的二进制数进行相乘可以采用移位相加的原理来实现,乘2由逻辑左移1位来实现,而乘4由逻辑左移2位来实现,以此类推,最后把所有逻辑左移的中间结果累加起来,获得相乘结果。由乘法器的移位相加原理可知,整个电路系统可以划分为4个子模块,即顶层文件由4个底层元件组成,分别是:右移移位寄存器、输入数据开关、逻辑左移电路、6位相加器。

具体的工作过程:参与乘法的其中一个数进入到右移移位寄存器,在输入数据开关模块利用右移移位寄存器的逐位输入对另外一个参与相乘的数进行控制输出;逻辑左移电路对锁存进来的数据进行逻辑左移,并把上一周期的高7位数据和当前低5位数据并置,输出12位相乘结果,同时截取高6位数据传送到6位加法器和另外一个6位输入数据相加;6位加法器完成数据逻辑左移中间结果的累加功能,输出7位数据。

1.1.2 输入步骤

(1)运行QuartusII软件,进入到VHDL文本输入界面。根据上述的原理分析,逐一输入4个模块的VHDL代码,逐一完成存盘、编译、仿真等步骤;

(2)利用VHDL语言的component例化语句,调用步骤(1)已完成设计的4个底层元件,利用端口映射port map语句实现底层元件在顶层文件的端口连接关系;调用4个底层元件及端口映射的顶层文件部分代码如下:

component accu is

port(clk,clr:in std_logic;

d:in std_logic_vector(6 downto 0);

q:out std_logic_vector(11 downto 0);

qqq:out std_logic_vector(5 downto 0));

end component;

component regshift is

port(clk,load:in std_logic;

din:in std_logic_vector(5 downto 0);endprint

qb:out std_logic );

end component;

component switchdata is

port(abin:in std_logic;

din:in std_logic_vector(5 downto 0);

dout:out std_logic_vector(5 downto 0));

end component;

component adder is

port( a,b:in std_logic_vector(5 downto 0);

s:out std_logic_vector(6 downto 0) );

end component;

……

u1:accu port map(clk=>clk,clr=>load,d=>net4,

q=>q,qqq=>net3);

u2:regshift port map(clk=>clk,load=>load,

din=>a,qb=>net1);

u3:switchdata port map(abin=>net1,din=>b,

dout=>net2);

u4:adder port map(a=>net3,b=>net2,s=>net4);

(3)對顶层文件进行存盘、编译、仿真等步骤,观察仿真波形是否达到设计要求。

1.1.3 仿真结果分析

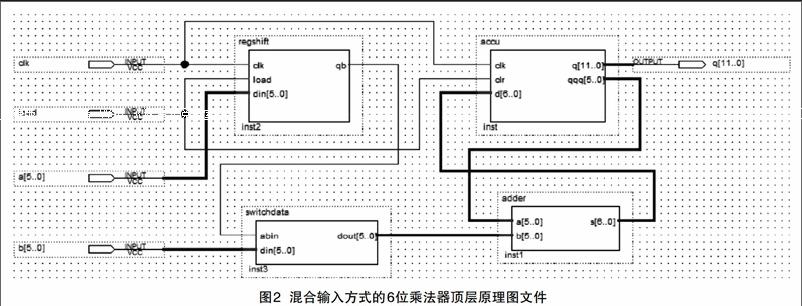

从顶层文件的仿真波形[6]可以看出,如图1所示两个相乘的6位二进制数分别为:1B和3D,得到最终的12位相乘结果是66F,同时也可以看出移位相加过程的中间累加结果随着时钟触发而跳变。仿真波形验证了底层元件和顶层文件VHDL代码描述是正确的。

1.2 文本和原理图混合输入方式

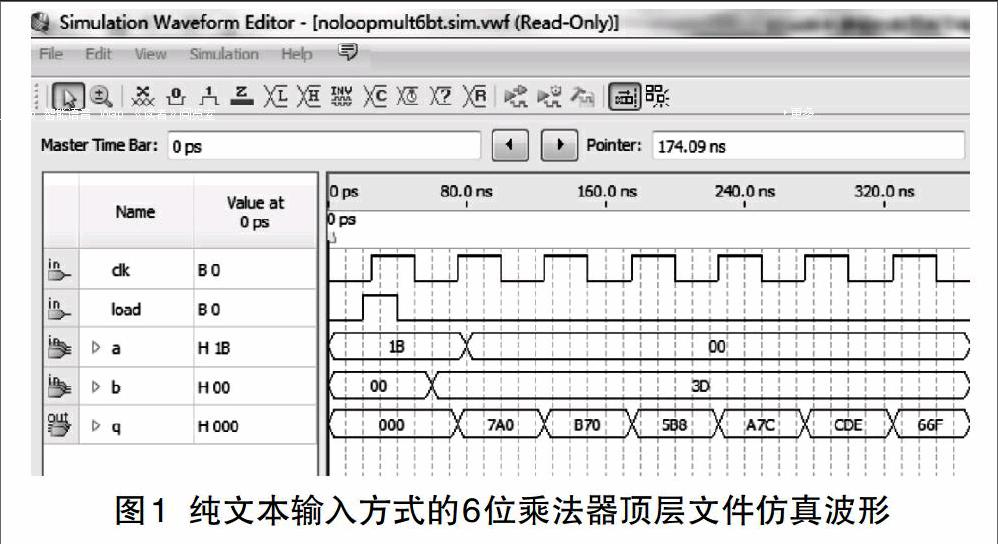

在实际的电路设计当中,经常会采用底层元件用纯文本描述,而顶层文件用原理图来描述的混合输入方式,移位相加型6位乘法器顶层文件原理图如图2所示,由移位寄存器模块(regshift)、选通模块(switchdata)、加法器模块(adder)、累加模块(accu)组成,实现整个电路系统的设计。

1.2.1 输入步骤

(1)在VHDL文本输入界面编辑各个子模块的底层文件,利用QuartusII软件生成底层元件;

(2)在原理图输入界面调用步骤(1)生成的底层元件,用连线的方式完成顶层文件的电路原理图设计;

(3)对顶层文件进行存盘、编译、仿真等步骤,观察仿真波形是否达到设计要求。

1.2.2 仿真结果分析

仿真波形和纯文本输入方式一致,验证了底层元件VHDL代码和顶层文件原理图混合输入方式是可行的。

1.3 纯文本输入和原理图输入的比较

(1)原理图输入方式直接用连线的方式在EDA软件的输入界面绘制电路原理图,这种方式的特点是直观、方便,适合小规模的简单电路系统设计;

(2)纯文本输入方式通过编写硬件描述语言代码来描述电路功能[7],具有对电路功能的抽象作用。由于硬件描述语言表达的丰富多样性,因而纯文本输入方式可以对大规模的复杂电路系统进行设计;

(3)文本和原理图混合输入结合了两种输入方式的优点。底层元件侧重于功能描述,采用文本输入;顶层文件侧重于结构描述,采用原理图描述。

2 设计过程的注意事项

(1)同一工程的所有文件必须要存放在同一工程目录(文件夹)下,工程名字必须是英文;对当前文件进行编译之前,要把当前文件设置为顶层文件;必须在文件打开的界面下,才能创建该文件所对应的元件,扩展名为bsf;

(2)采用文本输入方式时,存盘的文件名必须和代码的实体名一致,扩展名为vhd;使用component例化语句时,要注意端口映射语句里面的端口顺序和底层文件的端口定义顺序一致;

(3)采用原理图输入方式时,注意检查连线的交叉点问题;文件存盘的扩展名为bdf,注意调用自创建元件的路径和调用EDA软件自带元件库的路径。

3 结语

本文对6位乘法器的FPGA自顶向下电路设计方法进行了阐述,通过移位相加型乘法器重点介绍了纯文本输入方式、文本和原理图混合输入方式[8]的步骤。在实际的设计过程当中,结合EDA软件先对各个模块电路进行仿真,然后对顶层电路进行仿真,整个设计思路就会清晰,排查错误就会更方便。

参考文献

[1]李定川.FPGA技术在汽车电子中的应用[J].汽车电器,2009,8:1-4.

[2]周宁宁,刘胜.基于FPGA技术的CPU模型机的设计与实现[J].南京邮电学院学报,2003,23(1):77-80.

[3]刘强,方锦清,赵耿,李永.基于FPGA技术的混沌加密系统研究[J].物理学报,2012,61(13):78-83.

[4]潘松,黄继业.EDA技术实用教程(第五版)[M].科学出版社,2013.

[5]陈友荣,杨海波.基于FPGA技术视频采集系统的设计与实现[J].中国有线电视,2008,4:382-387.

[6]文璧,张洁,徐谦.基于无线射频与FPGA技术的数据采集系统[J].中国测试,2009,35(4):40-43.

[7]王春花,黄厚宽,马聪.一种基于FPGA技术的虚拟逻辑分析仪的研究与实现[J].自动化与仪器仪表,2000,3:39-42.

[8]王建军.用FPGA技术实现数字通信中的扰码和解扰[J].电子技术应用,1998,(5):48-49.endprint

Abstract:From top to bottom circuit design mean is the emphasis during FPGA circuit design. There is great difference between this mean and traditional electronic design. From top to bottom circuit design mean processes circuit design file by the EDA software in order to fulfill application specific integrated circuit design. In this paper it introduces two circuit design input means in the shift and accumulate type multiplier example. The pure text input mean describes the top level and bottom level circuit behavior by hardware description language. The composed mean of text input and schematic input describes the bottom level component by hardware description language, on the same time the top level file will be fulfilled by the schematic input. There is analysis of simulate waveform about two different input means, it proves these design means are right and concludes their characteristics.

Key Words:from top to bottom;hardware description language;text input;schematic input;multiplierendprint