基于VBE线性化与分段补偿技术的带隙基准电压源

王永泽

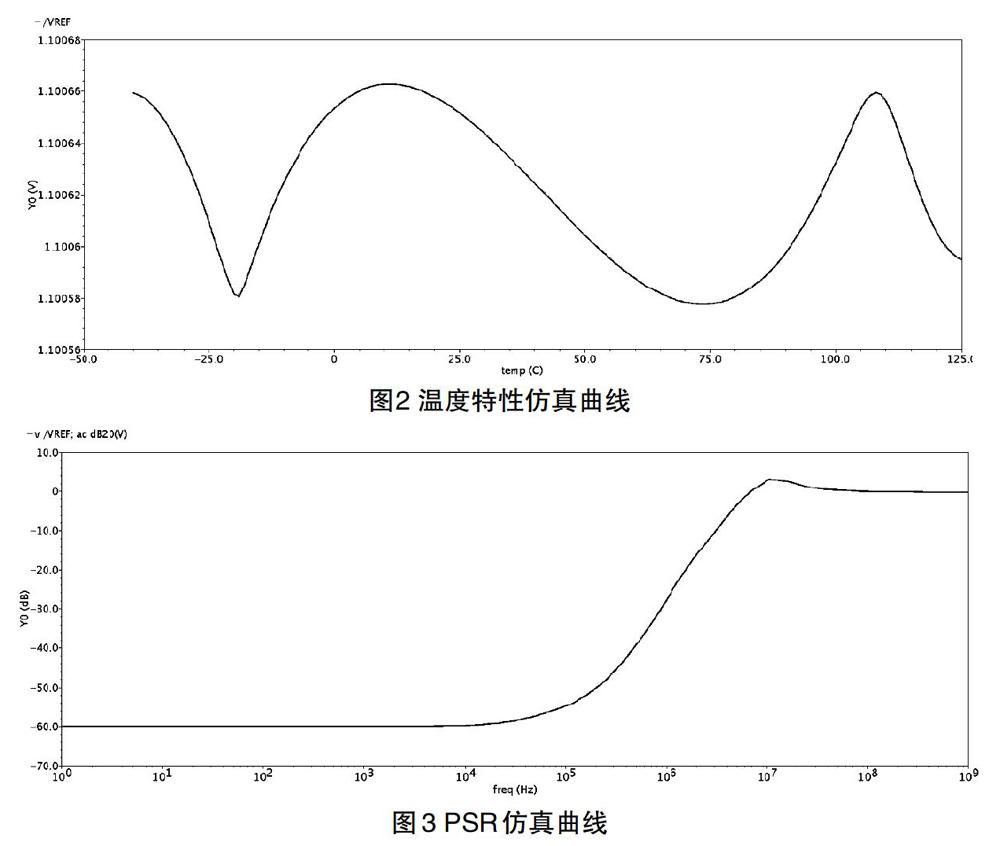

摘要:基于SMIC 0.18μm CMOS工艺,采用VBE线性化补偿技术与温度分段补偿技术设计了一种高精度的带隙基准电压源。仿真结果显示,所设计的带隙基准电压源在-40℃~125℃内获得了0.47ppm/℃的溫漂系数,在低频处获得了-60dB的电源抑制。

关键词:带隙基准;VBE线性化补偿;温度分段补偿;电源抑制

中图分类号:TN432 文献标识码:A 文章编号:1007-9416(2018)12-0054-02

0 引言

带隙基准电压源在电源电压与环境温度变化的情况下可以提供一个高精度的参考电压,因而被广泛应用于高性能的A/D转换电路、D/A转换电路、锁相环、滤波电路等重要模拟电路模块中。为得到高精度的带隙基准源,通常需要在一阶带隙基准电路的基础上进行温度补偿,目前带隙基准补偿方法有二阶温度补偿[1]、VBE线性化补偿[2]、分段线性补偿[3]等。基于此,本文结合了VBE线性化补偿与分段补偿技术,设计了一种高精度带隙基准电路。

1 电路设计

图1为本文设计的带隙基准电压源,主要包含VBE线性化补偿电路、分段补偿电路、启动电路三个部分。VBE线性化补偿思想是通过控制三极管集电极电流的温度系数,进而产生一个对基准电压进行补偿的非线性电压。分段补偿电路中,M11管漏极电流在R5上产生的电压在低温区域对基准电压进行补偿,M7管漏极电流在R4与R5上产生的电压在高温区域对基准电压进行补偿。启动电路用于保证电路顺利进入正常工作状态。

VBE线性化补偿电路由MOS管M1~M6、四端输入运放A1、双端输入运放A2、双极型晶体管Q1~Q3、电阻R1~R5组成。其中,M1管与M2管完全相同。Q3的发射结面积是Q2的N倍。在忽略四端输入运放A1引入的高阶项压差的情况下,节点C与节点D电压相等,则流经Q2集电极电流IQ2为。式中,k为玻尔兹曼常数,T为绝对温度,q为电子电荷量。运放A2强制节点B与节点C电压相等,M6漏极电流I6为I6=VEB2/R1。M5管与M6管完全相同,则流经Q1集电极的电流等于I6。PNP型双极型晶体管发射极-基极电压VEB的温度特性为[4]: (1)

式中,Vg0温度为0K时硅的带隙电压,Tr表示参考温度,VEB(Tr)为参考温度Tr时双极型晶体管发射极-基极电压,η为一个与温度无关但与工艺相关的常数,x为流过双极型晶体管的电流的温度系数(对于PTAT电流来说,x等于1)。

由于流经Q1、Q2集电极电流的温度特性系数不同,节点A与节点C间的电压差为: (2)

式中,C1与C2为与流过双极型晶体管的电流温度系数以及参考温度下双极型晶体管发射极-基极电压相关的常数。通过四端输入运放的作用,将此非线性电压差引入节点D与节点C之间,则:

(3)

式中,gm1、gm2分别为四端输入运放两个输入对的跨导值。

M2管漏极电流I2为:

(4)

MOS管M3与M2完全相同,MOS管M4与M17完全相同,MOS管M3与M4的漏极电流同时作用于电阻R3、R4与R5上,产生一个经过VBE线性化补偿的带隙电压。

分段补偿电路由MOS管M7~M19、放大器A3~A4、双极型晶体管Q4~Q5、电阻R6~R7组成。MOS管M18与M19完全相同,Q5的发射结面积是Q4的M倍。放大器A3~A4使节点E、F、G的电压相等,所以MOS管M17的漏极电流I17为,MOS管M18的漏极电流I18为。

MOS管M15与M17完全相同,MOS管M13与M18完全相同,MOS管M14的宽长比为MOS管M16的β1倍,MOS管M11的宽长比为MOS管M12的β2倍。所以,MOS管M11的漏极电流为:

(5)

电流I11在R5上产生的电压在在低温区对带隙基准输出进行补偿。

MOS管M8的宽长比为MOS管M18的β3倍,MOS管M10的宽长比为MOS管M16的β4倍,MOS管M7的宽长比为MOS管M9的β5倍。所以,MOS管M7的漏极电流I7为:

(6)

电流I7通过电阻R4、R5产生的电压在高温区域对带隙基准输出进行补偿。

综上分析,图1所示的带隙基准电压源的输出电压VBG为:

(7)

由式(1)~(6)可知,通过优化电阻R1~R7的阻值以及参数β1~β5的大小,可以获得低温漂的带隙基准电压。

2 仿真结果

采用SMIC 0.18 μm CMOS工艺,在1.8V电压下对本文所设计的带隙基准电压源电路进行仿真验证。图2为带隙基准电压源输出电压温度特性仿真曲线。仿真结果显示在-40℃~125℃温度范围内,带隙基准电压源输出电压的温漂系数为0.47ppm/℃。图3为本文所设计的带隙基准电压源电路的PSR仿真曲线。仿真结果显示,带隙基准电压源在低频处获得了-60dB的PSR。

3 结语

本文采用VBE线性化补偿与分段线性补偿技术设计了一种高精度带隙基准电压源电路。仿真结果显示带隙基准电压源获得非常好的性能特性,适用于高精度电路系统。

参考文献

[1]陈文韬,邓婉玲,黄君凯.一种高精度二阶温度补偿带隙基准电路设计[J].固体电子学研究与进展, 2014(5):470-475.

[2]张瑛,王剑,周洪敏.一种低温度系数的带隙基准电压源设计[J].计算机技术与发展,2016(2):150-153.

[3]周前能,罗毅,徐兰,等.一种高PSRR高阶温度补偿的带隙基准电压源[J].微电子学,2018(3):300-305.

[4]Rincon-Mora G A.集成基准源电路设计[M].科学出版社,2013:17-20.

A Bandgap Voltage Reference with VBE Linearized Compensation and Piecewise Compensation Technique

WANG Yong-ze

(College of optoelectronic engineering, Chongqing University of Posts and Telecommunications, Chongqing 400065)

Abstract:A high precision bandgap voltage reference (BGR) with VBE linearized compensation and piecewise compensation technique was designed in SMIC 0.18μm CMOS process. Simulation results showed that the temperature coefficient of the designed BGR was 0.47 ppm/℃ in the temperature range from -40℃ to 125℃. The PSR of the designed BGR was -60dB at low frequency.

Key words:bandgap voltage reference; VBE linearized compensation; piecewise compensation; power supply reject ratio