基于Verilog HDL语言的FPGA浮点数加减法运算的实现

谢文彬

(淮安生物工程高等职业学校,江苏淮安223200)

0 引言

浮点运算方式较定点运算有计数范围宽、有效精度高的特点,是目前大多数计算机系统采用的表达形式,也是数控系统中刀具补偿、插补计算常采用的运算方法。目前比较流行的方法是使用DSP数字信号处理芯片实现浮点运算。浮点表述结构复杂,完全使用DSP软件实现一定程度上会影响DSP的运算速度。

本文主要研究利用Verilog HDL语言进行FPGA浮点运算加减法方法的实现。Verilog HDL是基于C语言的硬件描述语言,对数字逻辑电路建模有着独特的优势。

1 浮点数加减法运算的实现过程

本文浮点数的运算介绍基于二进制单精度类型,由符号位、阶码位、尾码位组成(以上由IEEE 754[1]标准定义)。在符合IEEE 754标准的浮点数加减运算过程中,减法运算也可以转变成加法运算,只要处理好两数的符号即可。规格化浮点数加法可以分为符号判断、阶码比较、尾码对阶、求和或求差和规格化处理等步骤。其加减法运算步骤[2]如下:

(1)符号判断:判断是加法运算还是减法运算。

(2)阶码比较:求解两个浮点数阶码的差。

(3)尾码对阶:小阶向右移动阶差位,阶码增加阶差位。

(4)求和或求差:对阶完毕浮点数的尾码需要进行求和或求差。

(5)规格化处理。

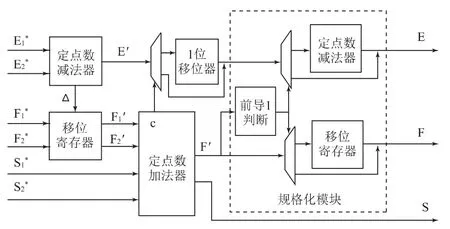

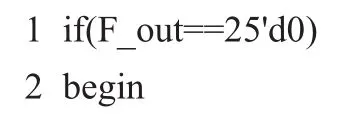

使用FPGA实现浮点数加减法运算的模块结构如图1所示。

图1 浮点数加减法基本算法模块结构

在规格化模块中要对结果进行前导1检测、初次规格化、尾数舍入和最终规格化得到最后结果,尾码应表示最多的有效数且用纯小数给出,同时尾码大于等于1/2小于1,即尾码最高位为1,尾码右移一位,阶码增一称为“右规”,尾码左移一位,阶码减一称为“左规”,规格化可增加有效数的位数,提高运算结果精度[3]。根据浮点数运算器逻辑可得到使用硬件描述语言设计运算模块的端口定义如表1所示。

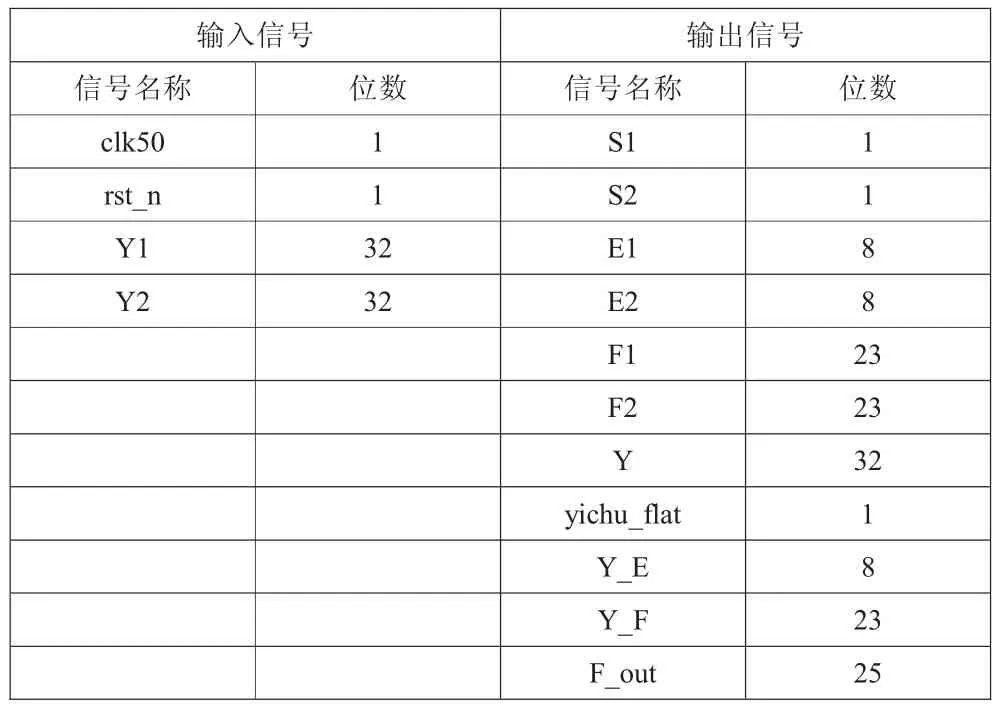

表1 浮点运算模块端口

在输入端口信号中,clk50为50MHz时钟信号;rst_n为模块复位信号,低电平有效;Y1为被加数或被减数;Y2为加数或减数。

在输出端口信号中,S1为Y1的符号位;S2为Y2的符号位;E1为Y1的阶码位;E2为Y2的阶码位;F1为Y1的尾码位;F2为Y2的尾码位;Y为最终输出结果信号;yichu_flat为阶码溢出标志信号;Y_E为Y的阶码信号;Y_F为Y的尾码位;F_out为规格化时的尾码位,其规格化后的低23位赋值给Y_F。

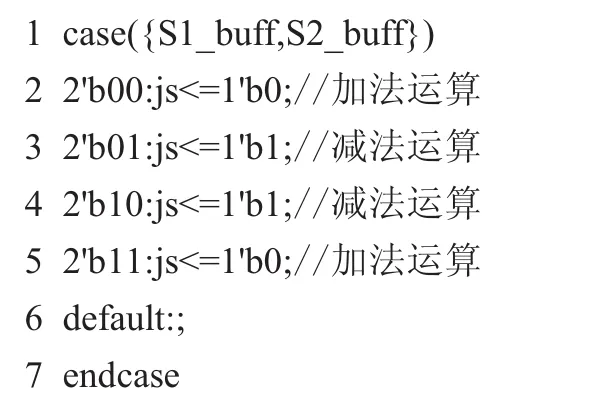

根据S1、S2的值判断两数的加减运算,如果S1、S2的值为“00”或“11”两数相加,否则两数相减。在相减过程中,如果S1、S2的值为“01”,则Y1为被减数,Y2为减数,否则Y2为被减数,Y1为减数;js为加减法运算判断信号,当js的值为“0”时表示两浮点数进行加法运算,否则表示两浮点数进行减法运算。其部分硬件描述语言如下:

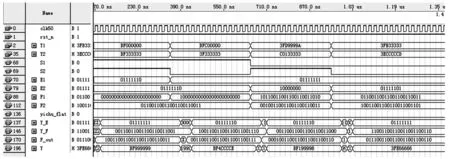

在浮点数加减法运算过程中,规格化处理过程比较重要,只有经过了规格化,其最终结果才能符合IEEE 754标准。本文使用casex语句来完成规格化处理,主要部分硬件描述语言如下:

2 仿真验证

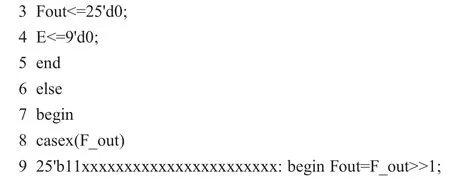

利用硬件描述语言编写,经过编译和综合,可得浮点数运算模块的封装图,在得到封装图的基础上进行了仿真,验证了设计的正确性。浮点数加减法模块共消耗了1 162个LE(逻辑单元)、195个寄存器、97个用户可用管脚、122个测试点。仿真图如图2所示,仿真图中各信号含义参照表1。

图2 浮点数加减法模块仿真图

在时钟clk50和复位信号rst_n的作用下,当复位信号rst_n为低电平时,信号E、F_out、yichu_flat清零置数;当复位信号rst_n为高电平时,在时钟的上升沿,casex判断F_out的结构,E、F_out信号根据casex判断F_out的结构的结果进行减法和左移运算;当casex语句判断后的E[8]值为“1”时,表示有溢出,则溢出标志位yichu_flat置1。

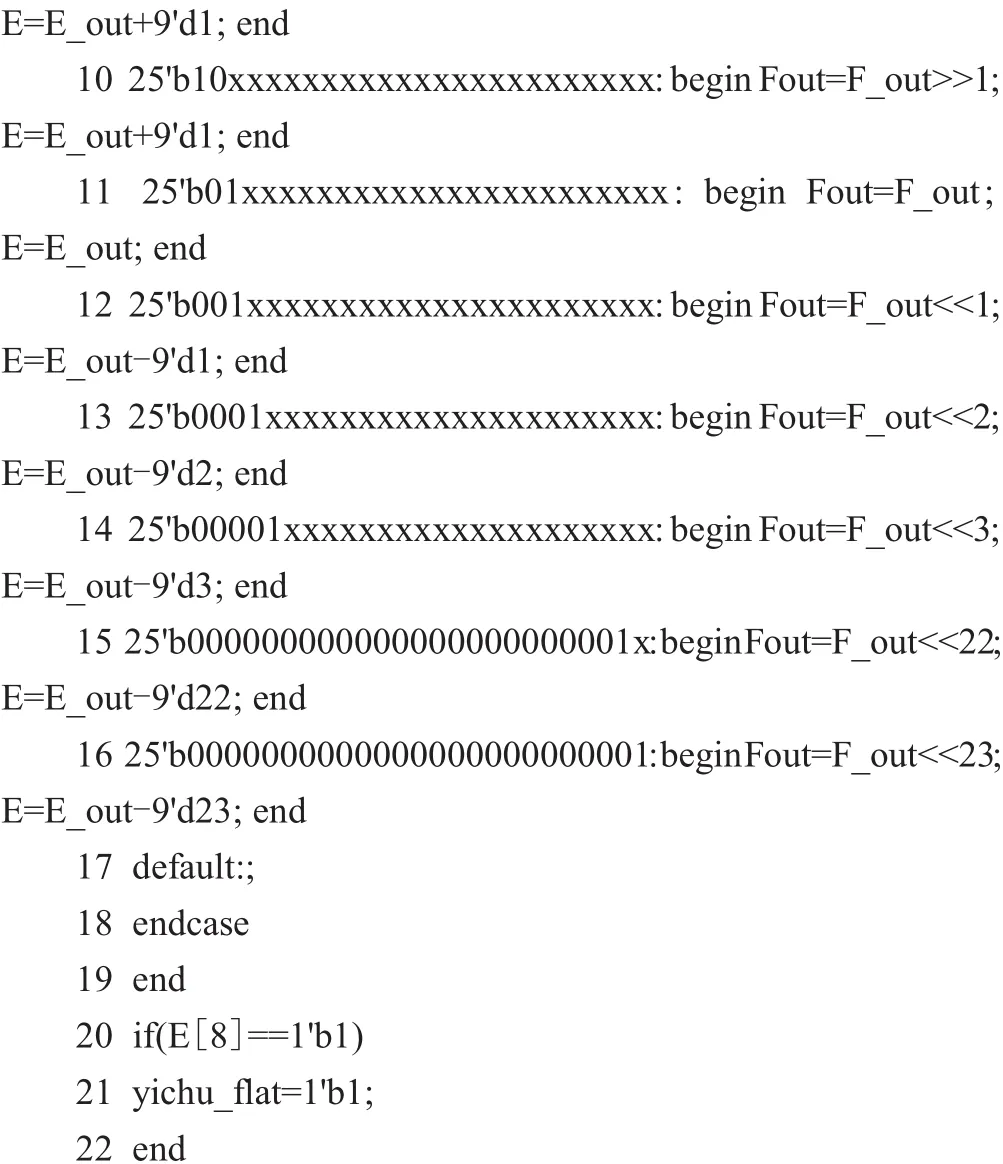

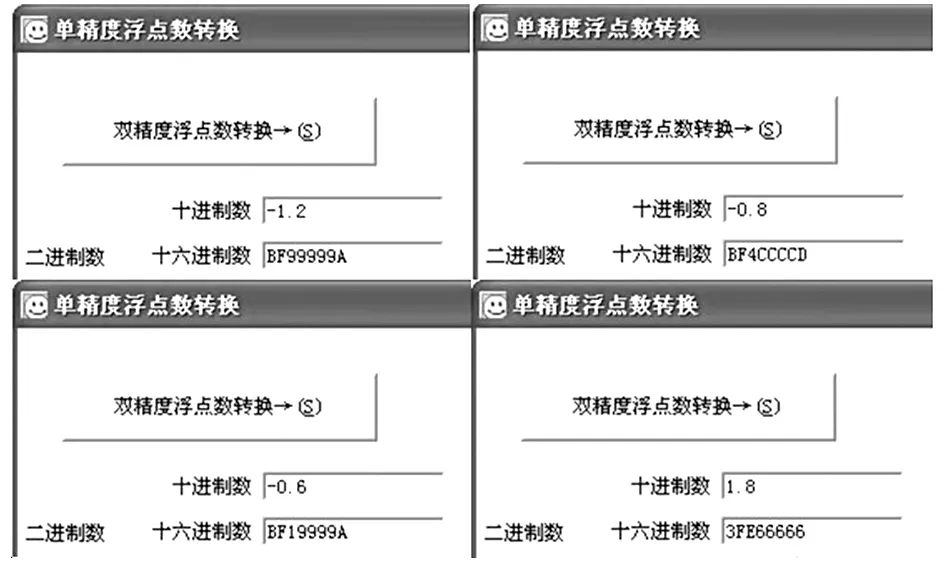

在仿真图中,有4组数据运算,其中输入数据均符合IEEE 754标准,由符号十进制数经过单精度浮点数转换专用软件转换为十六进制数,结果如图3所示。

图3 IEEE-754浮点数软件转换图

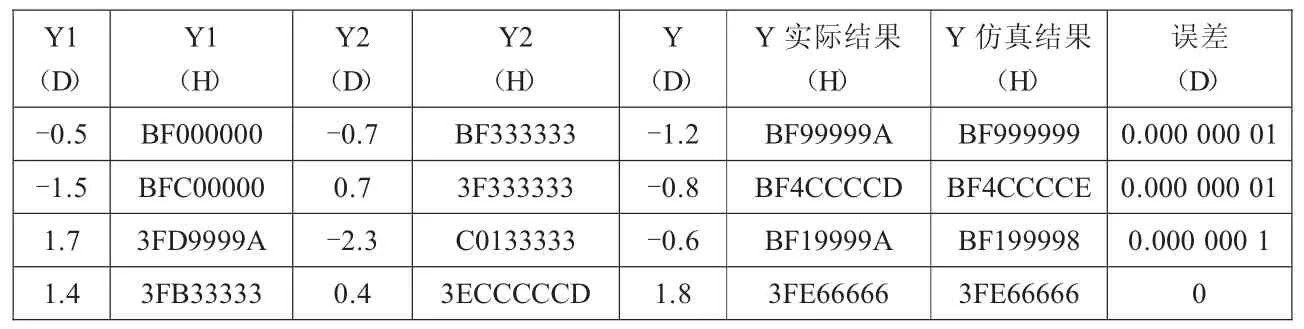

浮点数加减法数值计算表如表2所示,由表可以看出,本设计的仿真结果与实际结果有误差,误差计算公式为:误差=尾码差×2阶码,也可以使用专用软件由十六进制数逆推到有符号十进制数,然后算出误差值。由误差项值可以看出,其数值极小,不影响系统的计算精度,得出FPGA浮点运算加减法设计方法正确可行,精度高。

表2 浮点数加减法数值计算表

3 结语

在如今数控系统需要高精度、高速度的时代背景下,基于FPGA芯片技术特点,使用FPGA实现浮点数运算已经是大势所趋,它正在为人们所广泛接受。