CMOS抗辐射加固集成电路单粒子效应仿真研究进展

赵元富,王 亮,舒 磊,刘家齐,刘 琳,岳素格,李同德,李 园,顾 问

(1.北京微电子技术研究所,北京100076;2.哈尔滨工业大学 航天学院,哈尔滨150001;3.北京工业大学 微电子学院,北京100124)

仿真技术在单粒子效应的发现和研究过程中起到了不可忽视的作用。早在1962年,Wallmark等首次通过计算分析认为宇宙射线会影响器件的正常运行[1],10年后人们才首次在在轨运行的存储器中发现了单粒子翻转(single event upset,SEU)[2-3]。1983年,Diehl等通过对美国圣地亚国家实验室(SNL)3um标准单元库的SPICE仿真,首次提出组合逻辑电路单粒子瞬态(single event transient,SET)的概念,表明粒子攻击组合逻辑电路可形成一个电压瞬态脉冲。该电压脉冲沿组合逻辑向下传递,最终使得锁存器翻转。通过仿真确定了至少能传播4个标准逻辑门的持续脉冲的最小电荷量,还预测了SET可能是SEU加固电路的主要错误来源[4]。这些仿真结果在随后的几十年里被一一证实[5-7]。

随着集成电路在器件结构、尺寸、材料和电压等方面发生的变化,其单粒子效应变得越来越复杂。研究表明,单粒子效应受温度[8-9]、电压[10-11]、器件阈值[12]、逻辑类型[12]及版图结构[13]等多种因素影响,机理变得极为复杂,各种影响因素间的相互耦合使电路发生SEU和SET的机理变得难以确定,给先进集成电路的单粒子加固带来了巨大挑战。在此研究过程中,单粒子效应的仿真,尤其是基于TCAD(technology computer aided design)的仿真,变得越来越重要[14-19]。

本文介绍仿真的基本流程和特征尺寸减小对单粒子辐射效应的影响,并详细介绍CMOS存储单元单粒子效应仿真研究工作的多方面进展,首次提出了利用交叉隔离和错误猝熄的方法改进传统存储单元的加固性能。

1 特征尺寸的缩小对单粒子辐射效应的影响及其仿真

1.1 仿真流程

采用TCAD仿真分析软件对集成电路单粒子效应进行仿真的基本流程,如图1所示。首先,根据版图和工艺规则,建立半导体器件三维模型。三维器件模型反映了器件的版图设计、导线和介质层厚度及有源区掺杂浓度等工艺信息。其次,基于蒙特卡罗方法进行高能粒子输运仿真,计算高能粒子在半导体器件内的轨迹和沉积的能量。再次,仿真半导体器件在各种辐射效应下的全物理过程,计算得到器件在各种辐射效应作用下的电流、电压波形以及收集的电荷,用于分析器件单粒子效应的形成机制,这些效应包括SEU、单粒子闩锁(single event latch,SEL)和SET。最后,进行半导体电路单粒子效应截面统计估算,设定辐射环境,产生粒子样本,模拟样本中各粒子的单粒子效应,给出半导体器件单粒子效应反应截面的统计结果。

图1 TCAD仿真流程Fig.1Flow chart of TCAD simulation

1.2 单粒子翻转

随着器件特征尺寸的减小,器件的结电容减小,工作电压降低,单粒子临界电荷减小,但单粒子效应电离产生的空间电荷量并未等比例减少,这使得电路对单粒子效应更加敏感。

图2给出了入射粒子在180nm和65nm SRAM中影响范围的对比。由图2可见,对于180nm SRAM,单个粒子入射的影响范围是1个存储单元;对于65nm SRAM,单个粒子入射的影响范围是9个存储单元。

由于纳米器件材料、结构和尺寸上的变化,单粒子效应和电路逻辑间的耦合关系也更加复杂,出现了明显的单粒子串扰及多节点电荷收集等现象[7]。对于单粒子引起的多节点电荷收集,通常将被粒子直接撞击的节点称为主动节点,将受单粒子产生的电荷扩散而间接影响的节点称为被动节点,将主动节点电荷通过电荷扩散影响被动节点的过程称为电荷共享。对单粒子电荷收集机理的分析表明,随着电路中主动节点和被动节点间距的减小,节点间的电荷共享效应显著增大。但机理分析只能进行定性描述,还需要通过仿真进行定量研究,以确定单粒子效应在时间和空间上的特性、机理及规律。

图2 入射粒子影响范围的对比Fig.2Comparison of influence ranges of incident particle

通过TCAD 3D混合仿真,研究了图3所示结构中主动节点和被动节点间的电荷共享效应。图4给出了不同节点间距下,被动节点收集的电荷占比随LET的变化。

图3 混合模式仿真结构Fig.3Mixed-mode simulation structure

图4 晶体管电荷共享仿真结果Fig.4Simulation results of charge sharing between transistors

当间距为2um时,被动节点收集的电荷占比小于2%;当间距为0.7um时,被动节点可收集的电荷占比最高可达40%。因此,对于65nm电路,电荷共享效应非常严重,单个粒子很容易影响到多个节点。

1.3 单粒子瞬态

随着器件特征尺寸的减小,器件工作频率增加,SET平均脉宽与典型电路周期及典型单元延迟的比例大幅增大,SET效应更加严重。

图5给出了SET脉冲宽度、典型电路周期及典型门延迟随工艺变化的情况。图5(a)表明,SET脉宽与典型电路时钟周期的比值(scale)增大,将导致SET更容易被锁存单元捕获;图5(b)表明,SET脉宽与典型单元延时的比值(scale)增大,使得SET在逻辑路径上更容易无衰减传播。SET可以发生在电路的任意节点,可传播到输出端,或导致时序/存储电路发生翻转。更多的SET可在逻辑路径上无衰减传播,更容易被存储单元捕获,使得纳米级集成电路的SET问题更加严重。

图5 SET脉冲宽度、典型电路周期和典型门延迟随器件工艺尺寸的变化情况Fig.5SET pulse width,typical clock cycle and typical gate delay vs.device size

SET在传播过程中,可能会发生展宽[20]、猝熄[21]、衰减或掩蔽等现象[12],对于先进工艺纳米集成电路,这些现象的规律将会更加复杂。例如,随着器件尺寸和间距的减小,必将导致电荷共享变得严重,而电路逻辑和SET间的耦合将使SET传播规律更加复杂,可能通过同相节点间的电荷共享实现脉冲展宽,也可能通过异相节点间的电荷共享实现脉冲猝熄,还有可能通过不同路径的脉冲叠加实现脉冲重汇聚。由于SET在纳米电路中传播的形变与掩蔽规律和机理变得极其复杂,需要借助仿真手段进行分析研究。

2 CMOS集成电路单粒子效应仿真研究

2.1 传统DICE加固存储单元加固失效仿真研究

双向 互 锁 存 储 单 元 (dual interlocked storage cell,DICE)是一种针对存储节点的加固方法,广泛用于SRAM和触发器等存储结构的加固设计[22]。但随着器件尺寸减小,单粒子临界电荷减小,单粒子更容易使存储单元翻转,由于器件间距减小,单粒子电离的电荷更容易通过电荷共享影响多个节点。这使得传统DICE加固单元加固性能降低甚至失效,不能取得预期的加固效果。本文通过仿真确定DICE加固单元敏感区域、分析其失效机理,并提出新的加固方法。

2.1.1 DICE加固存储单元敏感区域定位

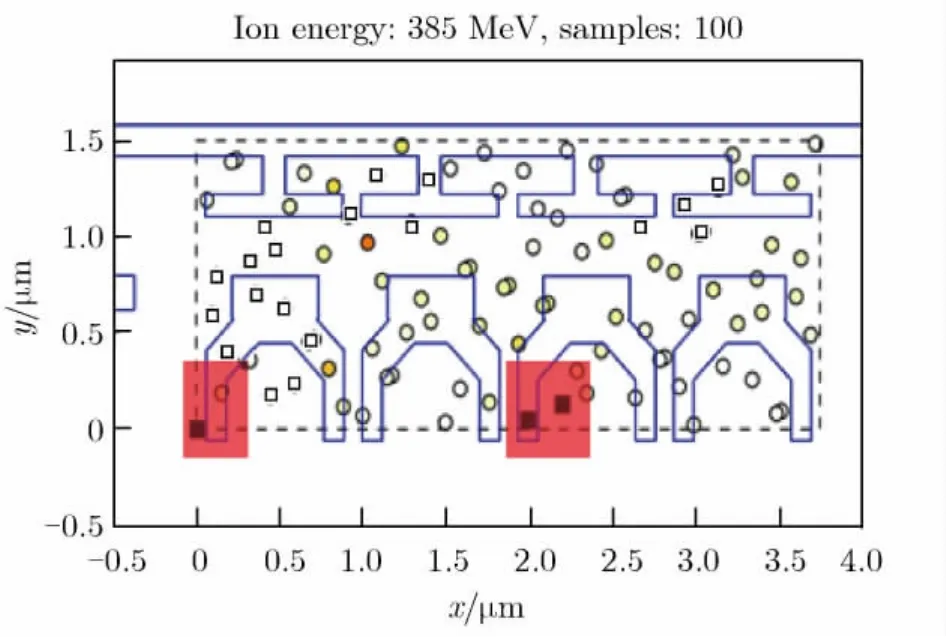

采用单元级单粒子仿真方法定位失效位置,通过半导体器件仿真,建立65nm DICE三维仿真模型,并在存储单元面积范围内产生100个垂直入射的粒子入射点。

对目标存储单元,分别使用 Cl,Ti,Ge,Bi 4种粒子进行入射,仿真研究了其引起的单粒子翻转行为。这4种粒子的能量对应分别为160,175,210,385MeV,表面 LET 值对应分别为13.1,21.8,37.3,97.1MeV·cm2·mg-1。仿真结果表明,Cl,Ti,Ge,Bi 4种粒子各100个,可以引起 DICE存储单元发生翻转的个数对应分别为1,2,2,3。通过仿真得到此目标存储单元的翻转阈值较低,小于14MeV·cm2·mg-1,并 定 位 了 存 储 单 元 的 敏 感区域。

图6为数值仿真得到的Bi粒子入射引起翻转的位置分布图。其中,点的位置为粒子入射位置,黑色方块代表该入射粒子引起翻转,圆圈和白色方块代表未引起翻转。

图6 TCAD仿真Bi粒子入射引起翻转的位置分布图Fig.6Upset location distribution caused by incident of Bi particle through TCAD simulation

2.1.2 DICE加固存储单元失效机理

为进一步研究DICE存储单元发生翻转的辐射效应机理,对能量为385MeV的Bi粒子辐照下DICE存储单元翻转情况进行了深入研究。图6中,100个能量为385MeV的Bi粒子引起3个翻转的入射粒子位置分别为(0um,0um),(1.989um,0.047um),(2.193um,0.129um),选取入射位置为(0um,0um)的情况进行详细分析。

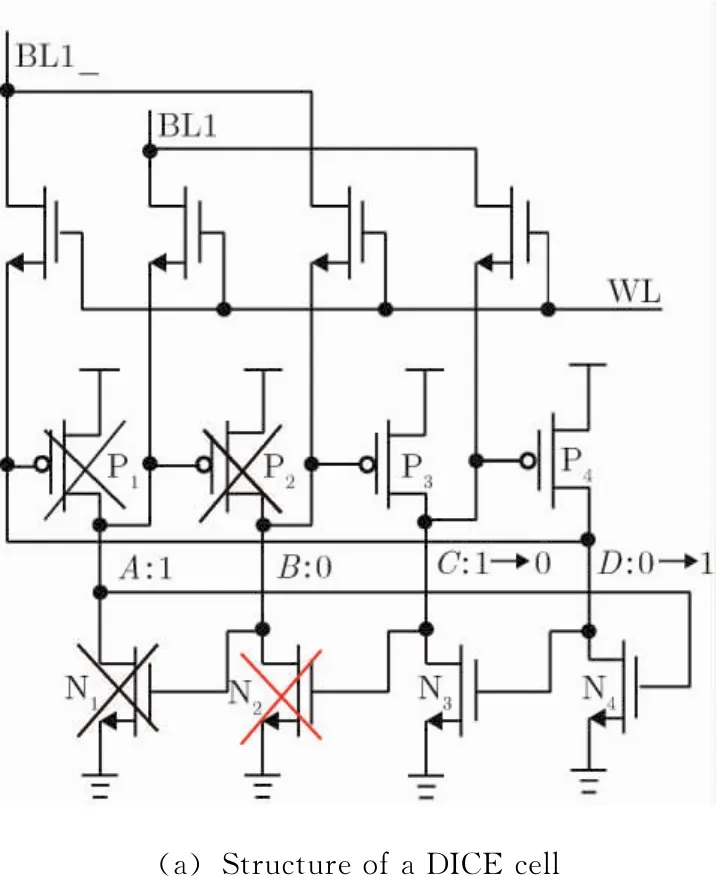

图7(a)为存储单元结构。其中,目标单元DICE的存储状态为(A,B,C,D)=(1,0,1,0),入射位置为(0um,0um)的Bi粒子,靠近NMOS管N3的漏区(存储节点C)。此时,目标单元DICE的敏感器件对是N3-N1和N3-P2。

图7(b)给出了入射位置为(0um,0um)的Bi粒子引起DICE发生翻转时,4个存储节点的电压变化曲线。

图7 DICE单元结构及入射位置为(0um,0um)的Bi粒子引起4个存储节点的电压变化曲线Fig.7Structure of a DICE cell and voltage curves caused by Bi particle incident on position(0um,0um)

由图7可知,入射粒子的直接电离首先影响距离入射位置最近的晶体管N3的漏区,因此,0ps时,存储节点C的电位由“1”翻转向“0”。由存储单元版图可知,节点C翻转到“0”,会开启晶体管P4,电源VDD开始通过晶体管P4向节点D充电,因此,节点D的电位开始由“0”向“1”翻转。节点C翻转到“0”,会使晶体管N2关断。节点D翻转到“1”,会使晶体P1关断。结合关断的晶体管N1和P2,节点A和B处于浮置状态,应该维持原来的数据。但是节点A在20ps开始由“1”翻转向“0”,从而引起DICE单元的最终翻转。因此,节点A是引起DICE单元翻转的关键原因。结合敏感节点对和单元版图,可知引起单元翻转的敏感器件对是N3-N1。也就是N1晶体管引起了节点A的翻转。

为了进一步找出敏感器件对N3-N1发生翻转的内部机理,对器件的三维物理模型进行截面切割,以此来观测晶体管N3和N1漏区下入射离子引起电子的收集情况。

图8给出了不同时刻下存储单元模型内部的电子分布。由图8(a)可知,0ps时,即离子刚入射时,产生的电子首先扩散到晶体管N3的漏区,并发生电子收集,因此引起节点C的翻转。此时,电子已经开始向晶体管N1方向扩散,但还没有扩散到晶体管N1的漏区。由图8(b)可知,20ps时,产生的电子已经扩散到晶体管N1的漏区,并在此处发生电子收集,因此引起节点A在20ps开始由“1”翻转向“0”。可见,在(0um,0um)位置的入射离子产生的电子先后扩散到晶体管N3和N1的漏区,并都发生了电荷收集。因此,敏感器件对N3-N1之间发生的电荷共享效应是DICE单元发生翻转的机理,即同型NMOS敏感器之间发生的电荷共享效应是造成DICE单元发生翻转的原因。

图8 不同时刻下存储单元模型内部的电子分布Fig.8Electron distributions of a SRAM cell at different time

2.1.3 双DICE四交叉加固方法的仿真验证

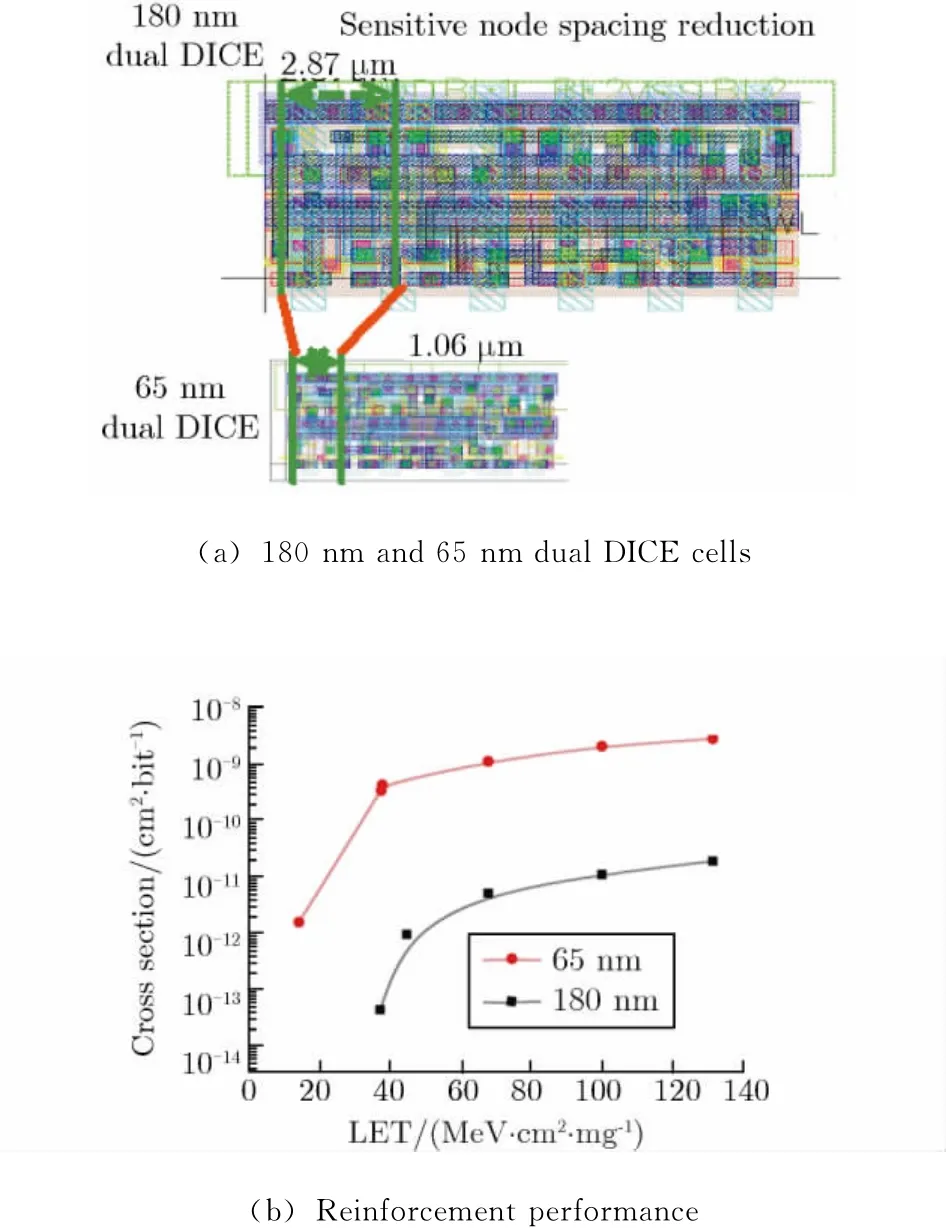

仿真发现DICE单元敏感器件对的电荷共享会导致DICE单元容易发生多节点翻转(multi node upset,MNU),使得传统DICE单元的加固性能降低。对此,提出了将敏感器件对分离的四交叉双DICE加固结构,如图9(a)所示。在不增加版图面积的情况下,实现将敏感器件对的间距增加到原来的2.8倍,且功耗和性能开销可以忽略。图9(b)的仿真结果表明,在180nm工艺下,存储单元的翻转截面降低2个量级以上。

图9 四交叉双DICE单元结构及其加固性能Fig.9Sturcture of a dual DICE four-interleaving cell and its radiation hardness result

2.1.4 仿真结果的试验验证

对180nm四交叉双DICE加固的存储电路进行重离子辐照试验和脉冲激光试验,试验结果和仿真结果的对比,如图10所示。可见,对于180nm四交叉双DICE加固存储电路,单粒子仿真、重离子试验和脉冲激光试验得到每个器件的单粒子饱和截面对 应 分 别 为4.0×10-5, 4.41 × 10-5,5.49×10-5cm2;单粒子仿真和重离子试验得到每个器件10%饱和截面下的LET阈值分别为35.1,33.8MeV·cm2·mg-1;脉冲激光试验得到10%饱和截面下的脉冲激光能量翻转阈值为26nJ。图10中,3条曲线符合较好。单粒子仿真得到的存储单元翻转阈值与重离子试验得到的翻转阈值相差为3.9%,重离子试验结果验证了仿真结果的正确性。

图10 单粒子仿真、重离子试验和脉冲激光试验得到的器件错误截面曲线对比Fig.10Comparison of error cross section curves obtained by single particle simulation,heavy ion experiment and pulsed laser experiment

2.2 65nm工艺存储单元抗MNU加固方法的仿真

2.2.1 65nm工艺四交叉双DICE加固方法的有效性降低

仿真和试验结果证明在180nm工艺下,四交叉双DICE加固方法能够有效地抗MNU加固,但是当工艺尺寸减小到65nm时,四交叉双DICE加固方法的有效性降低。图11(a)中,180nm工艺敏感节点对的间距为2.87um,但在65nm工艺下仅为1.06um。对使用相同的设计加固方法的180nm和65nm四交叉双DICE单元进行仿真,结果如图11(b)所示。可见,180nm四交叉双DICE单元的翻转阈值高达37MeV·cm2·mg-1,而65nm四交叉双DICE单元的翻转阈值小于14MeV·cm2·mg-1,说明65nm工艺下加固单元加固性能明显降低,因此需要针对其薄弱区域进一步加固。

图11 180nm与65nm四交叉双DICE单元及其加固性能的仿真对比Fig.11Simulation comparison of dual DICE fourinterleaving cells with 180nm and 65nm

2.2.2 EQDD加固结构

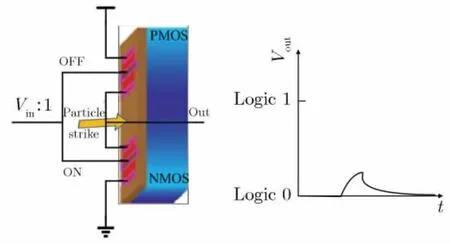

单粒子攻击反偏晶体管到电荷收集产生SET的机理已经研究成熟,但在纳米工艺下,单粒子攻击产生的电压扰动会有一些新的特性。通过仿真反相器正偏晶体管和反偏晶体管分别受粒子攻击产生的电压扰动特性,发现了利用正偏晶体管和反偏晶体管间的电荷共享,可使瞬态脉冲减小,将这个现象称为错误猝熄(error quenching)[17],EQDD(errorquenching double-DICE)称为错误猝熄双DICE。

图12给出了入射粒子对MOS晶体管SEE影响的仿真结果。

由图12(a)和图12(b)可知,粒子入射到“OFF”状态PMOS漏区时,反相器的初始输出为“0”,重离子入射到反偏的PMOS晶体管漏区,此存储节点收集正电荷,反相器的输出电压会瞬态上升,引起较大的从“0”到“1”的“正向”瞬态脉冲;粒子入射到“OFF”状态NMOS漏区时,反相器的初始输出为“1”,重离子入射到反偏的NMOS晶体管漏区,此存储节点收集负电荷,反相器的输出电压会瞬态下降,引起较大的从“1”到“0”的“负向”瞬态脉冲。

由图12(c)和图12(d)可知,粒子入射到“ON”状态PMOS漏区时,反相器的初始输出为“1”,重离子入射到正偏的PMOS晶体管漏区,输出节点的逻辑状态不会改变,此存储节点收集正电荷,会驱动反相器输出电压高于电源电压,即会引起小的从“1”到正“1”的“正向”瞬态脉冲;粒子入射到“ON”状态NMOS漏区时,反相器的初始输出为“0”,重离子入射到正偏的NMOS晶体管漏区,输出节点的逻辑状态不会改变,此存储节点收集负电荷,会拉低反相器输出电压低于地电压,即会引起较小的从“0”到负“0”的“负向”瞬态脉冲。

图12 入射粒子对MOS晶体管SEE影响的仿真结果Fig.12Simulation of the influence of incident particles on SEE of MOS transistors

根据仿真得到单粒子引起的反偏和正偏MOS管瞬态电压扰动特性,发现可以利用电荷共享来对其进行加固,入射粒子引起瞬态电压扰动的仿真结果如图13所示。入射粒子同时影响到“OFF”状态PMOS漏区和“ON”状态NMOS漏区时,由于在电路上此两处漏区实际上是同一逻辑节点,因此,“OFF”状态PMOS漏区上较大的从“0”到“1”的“正向”瞬态脉冲会被“ON”状态NMOS漏区上较小的从“0”到小于“0”的“负向”瞬态脉冲抵消一部分。即高能粒子同时影响了NMOS晶体管漏区和PMOS晶体管漏区,NMOS晶体管漏区收集负电荷引起的负向电压扰动会补偿PMOS晶体管漏区收集正电荷引起的正向电压扰动,从而减小了入射粒子引起的瞬态电压脉冲。图13表明到达两个漏区相连的逻辑节点上的从“0”到“1”的正向电压脉冲变小。

图13 入射粒子引起瞬态电压扰动的仿真结果Fig.13Simulation of transient voltage disturbance caused by incident particles

通过对反相器错误猝熄(EQ)的仿真,首次提出了利用EQ技术的双DICE存储单元版图加固结构,如图14所示。将同一逻辑节点的两个漏区邻近放置,当单粒子事件在NMOS漏区和PMOS漏区之间发生时,就可利用两漏区上产生的电荷共享而引起的互斥脉冲,产生部分抵消作用,从而使单粒子引起的反偏区瞬态电压扰动变小。EQDD加固结构总面积为5.582 5um2,四交叉双DICE加固结构总面积为5.657 2um2,通过对比可知EQDD加固结构的面积更紧凑,且实现了将敏感节点对的间距增加到原来的2.2倍。

图14 利用EQ的版图加固结构EQDDFig.14Hardening structure EQDD with EQ layout

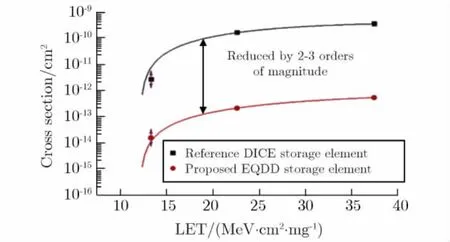

EQDD加固结构存储元件的仿真结果,如图15所示。图15表明,在65nm工艺下,EQDD加固方法能够有效降低双DICE单元的单粒子多节点翻转,与四交叉双DICE加固单元相比,EQDD加固单元的单粒子翻转截面降低2~3个量级[17],仿真验证了该加固结构的有效性。

图15 EQDD加固结构存储元件的仿真结果Fig.15Simulation results of EQDD memory components

2.3.2 65nm EQDD加固方法的试验验证

对采用EQDD加固的65nm存储电路进行重离子辐照试验,并将试验得到的错误截面随LET变化情况和仿真结果进行对比,如图16所示。可见,单粒子仿真和重粒子试验获得的两条曲线符合较好,试验结果再次证明了仿真结果的正确性。

图16 单粒子仿真结果与重离子试验结果对比Fig.16Comparison of single particle simulation and heavy ion experiment results

3 结论

综述了TCAD仿真技术在CMOS抗辐射加固集成电路单粒子辐射效应机理分析和抗辐射加固设计领域的研究进展。以CMOS存储单元为例,介绍了仿真在定位传统抗辐射加固集成电路抗单粒子效应薄弱环节、分析加固失效机理及指导加固设计方面的应用。根据仿真结果,首次提出了利用EQ加固SRAM的方法,并通过仿真和试验验证了该方法的有效性。对CMOS存储单元的仿真研究表明:仿真作为研究单粒子辐射效应的重要手段,对抗辐射加固设计有重要指导作用,需要进一步加强对仿真技术的研究。

随着集成电路全面进入纳米时代,集成电路性能进一步提升,器件单粒子临界电荷会进一步降低,导致集成电路的敏感区域和单粒子攻击产生的电荷所影响的节点数进一步增多,集成电路单粒子效应更加严重。对于先进工艺纳米集成电路,不再存在无需单粒子加固的部分,但全面加固会使得电路功耗开销太大,需要结合仿真准确地寻找纳米集成电路单粒子效应的薄弱环节,有针对性地进行加固。多节点电荷共享、电荷收集和电路逻辑间的耦合效应加强,会使得单粒子效应在时间、空间上发生变化,单粒子辐射效应将会变得更加复杂。需要通过仿真探究单粒子效应和电路逻辑的耦合机理,探索更适合的加固方法,用尽可能小的开销满足加固性能要求。而且对于先进工艺纳米集成电路,新材料和新结构的使用将会引入新的辐射效应机理,需要通过仿真对其机理进行分析。因此,仿真在先进纳米工艺下集成电路单粒子效应研究中的作用将越来越重要,利用仿真探究先进纳米集成电路单粒子辐射效应机理,指导抗辐射加固设计是先进纳米集成电路抗辐射加固的重要手段。