一种宽带可编程增益放大器设计

张博,王云娜,孙景业,吴昊谦

(西安邮电大学电子工程学院,陕西西安710121)

随着无线通信技术的高速发展,集成电路的发展越来越快。可编程增益放大器(Programmable Gain Amplifier,PGA)作为集成电路中的重要模块,也就被广泛应用于无线通信系统等领域[1-6]。其中,PGA在电路中起着变化增益、调整信号动态范围和稳定信号的作用[1-2],如在射频前端电路的信号太弱时,PGA可提供一定增益使信号被放大到适当的信号水平[3-4]。由于增益步进和增益误差是PGA的两项重要指标,不同PGA针对不同应用场景,增益步进和误差要求不同,所以这两项指标的优化设计电路已经相当成熟[7-9]。但是一般会对带宽和噪声系数(noise factor,NF)的设计要求比较低,如文献[6]中的带宽为20 MHz,NF为28 dB,文献[10]中的带宽为57 MHz,NF 为 19.3 dB,文献[11]中的带宽仅为40 MHz。因此,本次设计拟针对PGA的带宽和噪声进行优化设计,除了考虑引入直流失调校准电路(Direct Current Offset Cancellation,DCOC)外,还会重点设计主运放部分电路,对NF,线性度、相位裕度等指标进行优化设计。

1 PGA电路结构

本次PGA电路采用开关控制电阻反馈网络的结构来实现可变增益。主要由OPA、DCOC、电阻反馈网络和2-4译码器4部分组成。总体结构如图1所示。

图1 可编程增益放大器总体结构

图1中四组开关由2-4译码器控制来切换增益档位。其中,R为反馈电阻,VC_0dB、VC_6dB、VC_12 dB和VC_18 dB分别为译码器控制信号,A为运放增益。可实现增益范围为0~18 dB,步进为6 dB。

2 主运放电路设计

PGA电路应用于软件无线电(software define radio,SDR)发射链路,其中主运放电路采用两级运放与共模反馈和输出缓冲器级联的结构。如图2为主运放电路结构。

图2 主运放电路

图2中 NAND、OPA-1st、OPA-2nd、CMFB和输出buffer分别代表运放中与非门、第一级子运放、第二级子运放、共模反馈和输出缓冲器电路,IBIAS为外接偏置电流信号,VC_0和VC_1为译码器输入信号,VC为与非门输出信号,VFP和VFN为DCOC电路输入信号,VREF为电压基准信号,VIP和VIN为输入信号,VOUT_P和VOUT_N为输出信号。本次PGA电路为闭环结构,要实现较大的精度,需要主运放电路增益足够大。已知闭环增益表达式为

其中,β为环路增益,Vout为输出电压,Vin为输入电压。当βA远大于1时,可近似得

对主运放电路进行交流小信号仿真,可得开环增益约56 dB,即为630倍,可以实现闭环电阻反馈网络增益误差在0.15%以内。

2.1 噪声优化设计

针对主运放电路,主要影响的噪声为闪烁噪声和热噪声。对于金属氧化物半导体(Metal Oxide Semiconductor,MOS)管,闪烁噪声产生在栅氧化层和硅衬底界面处。电压源模拟等效噪声的表达式为

其中K是一个与工艺有关的常量,COX是单位面积的栅氧化层电容,1/f表示单位带宽,W和L分别为MOS管宽和长。由上式可知噪声与器件面积WL成反比关系,通过增大器件面积可以减小闪烁噪声。热噪声主要由导体内部载流子的无规则运动产生。运放中晶体管沟道电阻是最大的噪声源。对于一个W相对大的MOS管,源和漏端电阻可忽略,但栅端分布电阻很重要。在版图设计时,可采取将MOS管折叠的方法减小栅端电阻,从而减小欧姆区热噪声。

如图2中,将第一级子运放设计成PMOS管输入的共源放大电路。主要考虑到以下两点:相比较于NMOS管,PMOS管输运空穴是在埋沟中,即与“硅-氧化物”界面有一定距离,不易产生闪烁噪声;PMOS管的器件面积更大,更有助于降低闪烁噪声。

在链路中前一级增益较大时,可以有效压制后级噪声,实现总体低噪声的特性,级联噪声表达式为

因此,为实现较低的输出噪声,设计电路时将第一级子运放输入PMOS管合理取值,使跨导较大的同时,共模反馈电阻、PMOS管与N管的内阻并联阻值大即第一级子运放实现较大增益,利于有效抑制后级噪声。

2.2 相位裕度优化设计

环路相位裕度与开环运放的相位裕度息息相关。在不同增益下,运放的相位裕度会存在偏差。如图2所示,为优化运放的相位裕度问题,本次设计特别在第二级子运放输入与输出端,引入由与非门控制的MOS开关,通过开关通断来调节米勒电容的大小,使开关在0 dB、6 dB、12 dB增益时导通,增加电容,实现相位补偿的目的。此外,第二级运放输入与输出端的电阻与电容共同作用,实现相位与带宽的折衷。

2.3 线性度设计设计

如图2所示,最右边为本次设计的输出缓冲器电路。一般缓冲器电路的增益为1,主要作用是将本级与后级隔离,避免影响本级电路正常工作。本次缓冲器电路除了驱动后级的输入阻抗,实现将本级与后级电路级联的作用之外,另一特点是通过增大功耗与采用伪差分结构的方式,使增益大于1。考虑到在增益小于1时,主运放第二级的输出摆幅可以达到较大值,使主运放第二级线性度变差。所以设计时要求输出缓冲器的增益大于1,可以在不影响主运放第二级的线性度的情况下提高整体线度。

3 直流失调校准电路设计

一般,PGA电路对运放的增益要求比较高,但是器件失配在电路设计中无法避免,失配和前级造成的直流失调会对PGA引入重要问题[9]。由于输入管的失配产生的失调电压,在经过运放自身增益放大到下一级电路输入端时,可能会造成后级电路饱和,比如在输入端存在1 mV失调,运放增益为40 dB,如此会在输出端产生100 mV的直流失调,这样必会导致整个电路出现故障[10],所以考虑到整体电路的动态范围,加入DCOC电路来改善失调情况。

图3 直流反馈DCOC结构

如图3为基本的直流反馈DCOC结构。主要通过反馈环路来减小直流失调。其中,OPA为主运放电路,AMP为失调放大器,LPF为低通滤波器。该闭环系统的传输函数表达式为

其中,A为主运放增益,对应极点为P1,B失调放大器增益,对应极点为P2,低通滤波器增益为1,对应极点为P3。为使电路正常工作,必须满足P1>>P3,P2>>P3。

图4 DCOC电路

如图4为本次设计的DCOC电路。其中VIN_N和VIN_P为输入信号,VF_P和VF_N为输出信号。采用两个MOS管连接的方式,可以代替电阻实现较大的阻抗[10],同时避免了大电阻占面积的问题,减小了整体版图面积。

4 电阻反馈网络设计

图1外围环路即为电阻反馈网络。该结构主要通过2-4译码器控制4组开关通断实现不同增益档位间的切换[11-13]。输入端采用两个100 Ω的电阻并联的方式,可实现输入阻抗为50 Ω。其中,开关用射频MOS管实现,调节MOS管尺寸较大时,导通电阻较小,对反馈网络的阻值影响小,减小导通时对实际增益的影响。且开关管的取值按闭环增益成比例增加,确保更精确的放大系数。采用闭环电阻反馈形式,相对于吉尔伯特等有源结构,可实现高线性度[14-15]。在运放增益足够大的情况下,当第四组开关闭合,其它开关断开时,此时增益为0 dB,增益表达式可简化为:

同理18 dB对应表达式为

5 版图设计和仿真分析

5.1 版图设计

图1所示为总体电路,图5为本次设计的PGA版图,芯片面积为247 μm×180 μm。其中,由于电路设计时,主运放、DCOC和电阻反馈网络均采取差分对称结构,为确保性能,版图的布局布线也差分对称结构。版图设计时,注意电阻反馈网络中各级开关尺寸大小与增益精确度密切相关,需要根据反馈电阻大小合理设计。且增益对各级反馈电阻之间连线上的寄生十分敏感,布线时需要根据电阻比例精确设计布线宽度与长度,按比例关系进行布线设计,否则严重影响增益精度。

图5 PGA芯片版图

5.2 瞬态仿真结果

在输入信号频率为100 MHz,幅值为1 mV时,输出瞬态仿真结果如图6所示。

图6 PGA的瞬态仿真结果

5.3 增益仿真结果

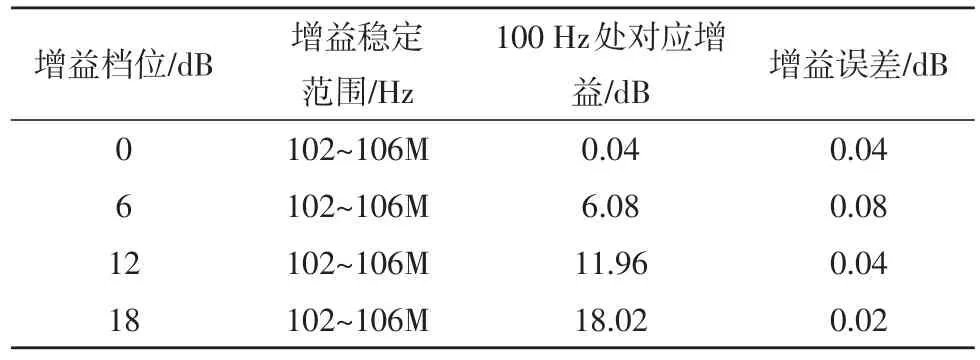

本次设计的PGA电路基于0.18 μm CMOS工艺,在确定输入信号后,分别可得0 dB、6 dB、12 dB、18 dB增益仿真结果如表1所示。

表1 各个档位增益仿真结果

低频时,增益会出现增益压缩的现象,主要原因是主运放电路中引入DCOC,虽然可以实现抵消直流信号差别的作用,但是其会出现压缩直流的同时压缩ac信号,使在低频处产生负增益。但是在100 Hz~100 MHz范围内均稳定在固定增益处。在100 MHz时对应增益分别为:0.04 dB、6.08 dB、11.96 dB、18.02 dB,可见误差均小于0.08 dB。

5.4 噪声系数仿真结果

在输入信号频率为100 MHz,功率为-10 dBm时,各个增益档位对应NF仿真结果如表2所示。

表2 各个增益档位NF仿真结果

结合前面2.2节内容,为了减小整体电路NF,在设计主运放电路时,将第一级增益设计的比较大,根据级联噪声特性,可以有效压制后级噪声,提高电路噪声性能。故在不同增益档位时,增益不同,带宽不同,对应NF值也不相同[7]。

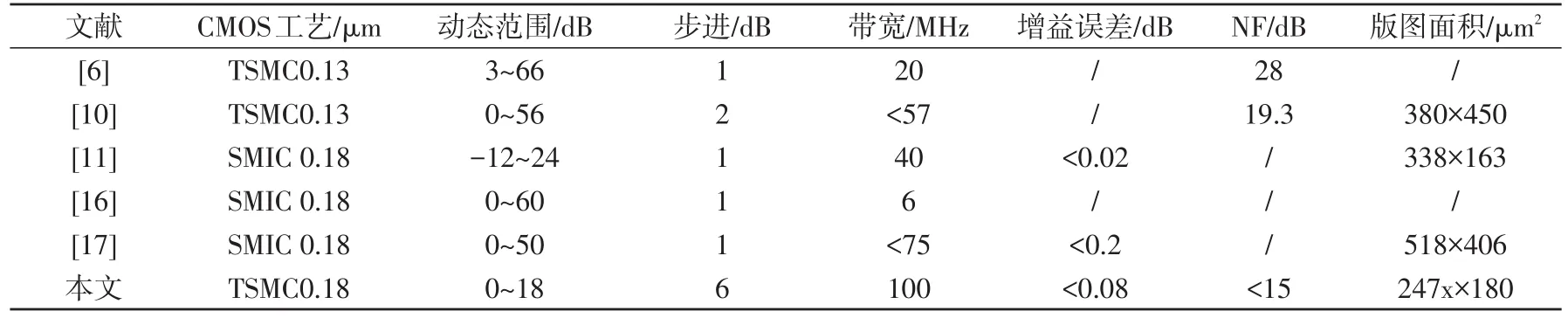

6 结束语

基于台积电0.18 μm工艺,采用闭环电阻反馈网络设计一种宽带可编程增益放大器电路。在设计主运放电路时,将第一级子运放设计成PMOS管输入的同时增加该级增益,减小整体噪声;在第二级输入与输出端添加由与非门控制的MOS开关,调整米勒电容大小,改善相位裕度;输出缓冲器电路采用伪差分结构,实现整体线性度的改善。引入DCOC电路,减小了失配和前级直流失调带来的影响。闭环电阻反馈结构可以实现高精度的闭环增益。仿真结果表明,在电压电源为1.8 V,输入信号100 MHz时,本次设计实现了0~18 dB增益范围变化,6 dB步进,输出增益带宽大于100 MHz,NF小于15 dB,芯片面积为247 μm×180 μm。

表3 本设计与文献中性能指标对比