基于电子控制器的片上可调式性结构设计研究

景琴琴,郭松梅,刘安才

(重庆能源职业学院,重庆,402260)

0 前言

目前,在对电子控制器功能进行调试的过程中,采用的方案主要以串口为主。串口调试方案主要是在既有的通信接口电路中增加独立的调试结构,然后通过模式选择进行工作方式的切换[1]。这一方案在应用的过程中,其优势在于能够节约管脚资源,进而能够降低制造的成本。然而,这一调试方案在实际应用的过程中,其也存在一定的不足。如在对核心电路拓补结构进行修改的时候会对全局的时序收敛产生影响;又如在自身调节方面,有时会存在不能自行调试的情况。另外,这一调试方案在实际应用的过程中,其还存在通信速率较低、误码率较高等劣势[2]。也就是说,串口调试方案难以满足高功能集成度控制芯片调试的需求。因此,本研究为获取低成本、高效率的通用化调试结构,基于JTAG技术对电子控制器的片上可调试性结构进行了设计。

1 电子控制器的片上可调式性结构设计的技术基础

在进行可调试性结构设计的过程中,本研究是基于JTAG技术的基础上进行设计的。因此,需要对JTAG技术的相关理论进行概述。JTAG(Joint Test Action Group)技术,又称IEEE1149.1规范,也称边界扫描技术[3]。JTAG技术是目前应用最为广泛的一种技术。JTAG技术是一种对数字电路的准静态测试方法,其主要被应用于板级电路板连接性能测试以及焊接质量的检测等。基于JTAG技术测试的内容主要有扫描链测试、边界扫描器件间互联测试以及边界和非边界扫描器件间的簇测试等[4]。在扫描链测试的过程中,主要是为了测试边界扫描器件焊接的质量。这也是JTAG技术完成测试的最重要基础。在互联测试的过程中,其测试主要是在EXTEST模式下完成的,测试序列主要包括两个步骤,即输入单元逻辑电平采集以及边界扫描单位预加载。簇测试主要是在部分电路不可通过互联测试进行检测时而采用的一种测试方法,其主要是利用边界扫描器件资源以对周围非边界扫描器件的测试。簇测试主要包括对逻辑和借接口的簇测试、存储器簇测试。

2 基于JTAG技术的可调试行结构设计方案

本研究基于JTAG技术,对调试方案进行了设计。本研究的设计思想主要是将芯片中的所有需要观测的寄存器进行串联,串联后,将其移至测试数据中,并对输出的数据进行分析,进而对电路的行为异常与否进行判断。标准的JTAG引脚由5个部分组成,即TCK、TMS、TDI、TDO、TRST。其中,TCK表示测试时钟,TMS表示测试模式,TDI表示测试数据输入,TDO表示测试数据输出,TRST表示可选的测试复位。JTAG逻辑的组成部分主要有3个,即指令、TAP控制器以及数据寄存器。其中,TAP控制器其与TMS相连,是具备16个状态的状态机,在TMS命令下,选择相应的寄存器将在至TDI和TDO间。数据寄存器主要包括器件寄存器ID、边界扫描寄存器、强制定义的旁路寄存器以及自定义寄存器。无论是哪一种寄存器,其均是由指令寄存器译码进行选择的。本文对JTAG技术接口的硬件逻辑进行重新定义,以促使发挥更大的优势,即不仅具有兼顾功能调试的作用,还具有可移植性,同时还能够降低原有逻辑性能的侵入性。

3 电子控制器的片上可调试性结构设计

3.1 TAP控制器可调试性结构的设计

在JTAG协议规范下,其对TAP控制器的状态迁移进行了明确的规定。在进行正常测试的过程中,受到TMS信号控制,从初始状态进入到指令寄存器控制流程中。在这一控制流程中,在Shift-IR状态下,将指令码输入其中,然后进行更新操作,此时指令码就会生效。然后,受到TMS信号的控制,再次从初始状态进入到DR控制流程中。在此流程中,数据输出主要通过TDO,此时会完成测试。在进行测试的过程中,为复用JTAG接口,并兼顾调试功能,选择的寄存器是自定义寄存器。通过自定义寄存器实现片外JTAG协议与片内标准总线协议之间的转换,形成高复用可调试性接口单元。

3.2 协议转换单元可调试性结构的设计

为实现片内并行总线信号与串行JTAG链路数据转换,为TAP控制器紧耦合一个协议转换单元也是非常的必要的。在进行工作的过程中,这一协议转换单元应该与控制器中的自定义寄存器配合。同时,为促使协议单元不对原有逻辑造成性能上的影响,应将协议转换单元设置为独立的调试模块。协议单元中的核心部件为自定义地址移位和数据移位寄存器。因此,在进行设置的过程中,应对这两个寄存器给予相应的指令。其中,地址移位寄存器与数据移位寄存器的总位宽均为33位。后者低32位与片上读、写数据总线匹配。前者低32位于片上地址总线匹配。后者最高位主要用于读写访问完成的指示。前者最高位主要用于区分读写访问。

3.3 总线主机接口可调试性结构的设计

本研究的可调试性结构设计的自定义寄存器主要有两套。这两套寄存器均需要与TAP控制器连接,然后通过相应的指令进行激活。在激活的过程中,通过进入到地址移位或数据移位寄存器中,进行激活。在首次调试访问过程中,通过查询就可以了解调试的状态,十分的方便且快捷。在进行可调试性的过程中,为两次调试访问可以连续进行性,在首次调试过程中,需要完成串并转换的调试访问。与此同时,为在调试的过程中,促使第二次调试迅速获得结果,应在串并转换期间完成总线仲裁。在总线访问时间一定时,仲裁授予时间应尽可能的短。为缩短仲裁的时间,可通过增加二级仲裁机制的方式实现这一目标。二级机制被激活的过程中,其处于的模式状态是调试模式。在这一模式下,拥有最高访问权的是协议转换单元,其直接占有总线,发起调试访问,进而能够缩短了仲裁授予时间。

3.4 协议转换器与调试软件的可调试性结构设计

可调试性系统应具备一定的完整性。也就是说,系统应包括调试接口的芯片,应包括在调试上位机运行中的调试软件,也应包括连接待测芯片和上位机的调试器。设计开发人员设计的可调试性软件,其能够为客户提供交互界面。在本研究中,上位机运行采用的开发环境是由ARM公司设计和开发的。在这一开发环境下,其提供了具有开放式的调试接口,进而能够实现在不修改集成环境界面的基础上,就将协议转换器进行驱动。协议转换器采用的是NXP公司设计开发的LPC2148微控制器,其能够实现与上位机调试软件的兼容。

4 可调试性结构设计后的实验与结果分析

4.1 逻辑功能

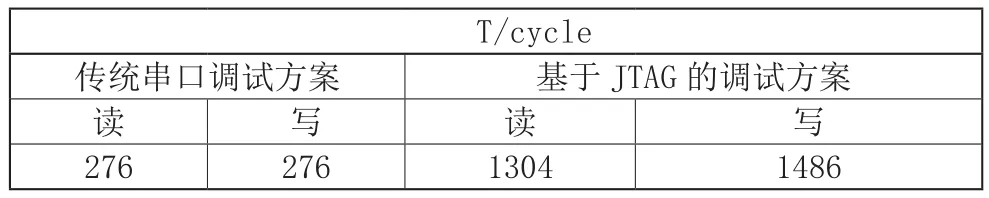

为进一步验证本研究结构设计的功能的正确性,对该调试方案进行逻辑功能测试。在进行测试的过程中,以主机接口的形式,将调试链路集成到以AXI总线为核心的SOC设计中。同时,通过模拟完成上位机发出的测试激励,然后对SOC片上的存储空间进行读写访问。通过比较传统串口和JTAG调试方案的功能测试时间,结果如表1所示。相比于传统的串口调试方案,采用本研究设计的调试方案,其能够显著缩短功能测试的时间。

表1 不同调试性结构设计方案功能测试后的时间比较

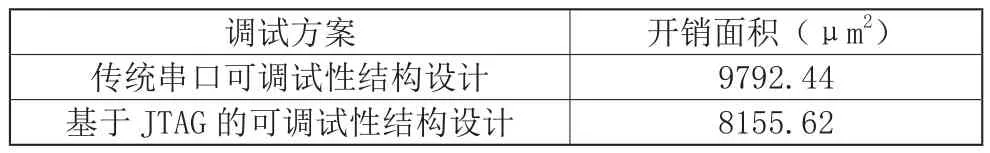

4.2 物理综合实现

本研究还采用物理综合对传统串口和JTAG调试方案的开销面积进行了比较。结果显示,相比于传统的串口调试方案而言,采用本研究设计的调试方案,其能够显著降低开销面积。

表2 不同调试性结构设计方案的开销面积比较

5 结论

本研究基于JTAG调试方案对电子控制器片上进行了结构设计,并通过实验结果显示,这一调试方案不仅能够缩短调试时间,还能够降低面积开销,同时还具有较可靠的调试链路。