ESD应力下改进型SCR器件设计与漏电特性优化

刘湖云,梁海莲,顾晓峰,马艺珂,王 鑫

(江南大学 物联网技术应用教育部工程研究中心,江苏 无锡 214122)

在集成电路静电放电(Electro-Static Discharge, ESD)防护中,可控硅(Silicon Controlled Rectifier, SCR)因具有单位面积的ESD鲁棒性强、寄生电容小等优势而备受关注[1-3].但是,由于SCR器件在ESD应力作用下具有电压深回滞、易闩锁的缺点[4-6],限制了其在ESD防护中的应用.近年来,在提高传统SCR、N跨桥改进型SCR(N-bridge Modified SCR, NMSCR)及其多种改进型SCR结构的ESD防护性能方面,已取得了一定的研究进展.例如,文献[7]通过在NMSCR结构中引入齐纳二极管,以及文献[8]提出的外接PMOS等辅助触发的方法,均可有效降低器件的触发电压和开启时间; 文献[9]在双向SCR中内嵌PMOS的方法可减小器件的电压回滞幅度; 文献[10]通过在P阱中增加N型漂移层和P型晕环注入的方法有助于增强ESD鲁棒性.但是研究人员在改善SCR器件各项ESD防护性能的同时,较少关注在ESD防护过程中器件的漏电特性变化.

金属氧化物半导体(Metal Oxide Semiconductor,MOS)器件在ESD防护中具有工艺易兼容的优点,但在ESD脉冲作用下易受热效应影响,导致器件的漏电流增大,削弱了器件的ESD防护可靠性[11-13].通常可通过以下两种途径减小热效应对MOS器件ESD防护性能的影响[14-16]: 一是选取低热阻材料,提高器件的散热能力,但该类技术仍未完全成熟,低热阻材料与集成电路制备工艺条件的匹配尚有待进一步研究; 二是合理改进器件结构或版图布局,促使器件内部的晶格温度均匀分布.

笔者提出一种内嵌MOS结构的N跨桥SCR器件(SCR embedded with the N bridge and MOS, SCR-N-MOS),并通过优化该器件版图及其金属布线,促进内部电流密度的均匀分布,防止器件内部发生局部过热,保证其漏电特性的稳定.通过工艺计算机辅助设计(Technology Computer Aided Design,TCAD)技术和传输线脉冲(Transmission Line Pulse, TLP)测试,对NMSCR、SCR-N-MOS及其优化前后在ESD应力作用下漏电特性的变化特点进行了比较分析.该器件的结构设计及其版图的金属布线方法可为改善ESD防护器件的漏电特性提供参考.

1 器件结构与TLP测试

1.1 器件结构

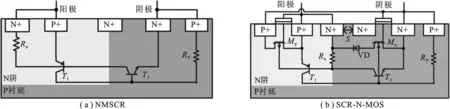

图1(a)和图1(b)给出了NMSCR和SCR-N-MOS器件的剖面结构及等效电路图.与NMSCR相比,SCR-N-MOS既在N阱中引入了一个PMOS,又在P衬底上方引入了一个NMOS.

图1 器件剖面结构及等效电路图

当ESD应力作用在NMSCR阳极端时,在N跨桥与P衬底界面处形成的PN结发生雪崩击穿,产生的电子流向N阱,空穴流向P衬底.当P衬底的寄生电阻Rp上的压降达到 0.7 V 时,寄生NPN管T2导通.随后,由于T2与寄生PNP管T1之间存在正反馈作用,T1迅速导通,形成SCR电流泄放路径,NMSCR完全开启.

与NMSCR不同,当ESD应力作用在SCR-N-MOS的阳极端时,N阱与PMOS源端处形成的PN结先发生雪崩击穿; ESD电流直接通过PMOS源端泄放到地,PMOS电流泄放路径导通.当ESD应力持续增加时,N跨桥与P衬底形成的PN结发生雪崩击穿,SCR电流泄放路径导通.同时,由于N跨桥与NMOS漏端之间的间距S较小,反偏PN-NMOS电流泄放路径也迅速导通.此时,SCR-N-MOS完全导通,形成PMOS、SCR和反偏PN-NMOS这3条ESD电流泄放路径.其中,PMOS有助于降低器件的触发电压,反偏PN-NMOS电流泄放路径有利于降低SCR电流泄放路径的电流密度,削弱SCR的正反馈程度,因此SCR-N-MOS器件具有较高的维持电压.

1.2 TLP测试与分析

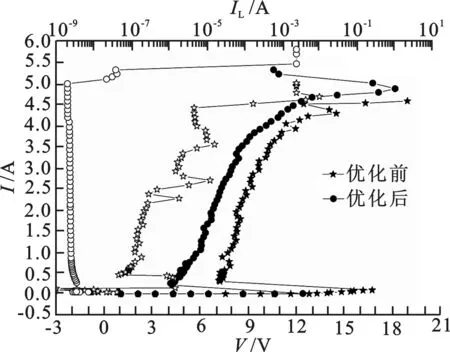

基于0.25 μm Bipolar-CMOS-DMOS(BCD)工艺制备了NMSCR和SCR-N-MOS实验器件.利用Barth 4002型传输线脉冲测试仪测得的NMSCR和SCR-N-MOS的特性曲线如图2所示,具有相同形状的实心和空心符号曲线分别表示同一器件在瞬态ESD应力作用下的电流-电压(I-V)关系和电流-稳态漏电流(I-IL)关系.可以看出,与NMSCR相比,SCR-N-MOS的触发电压从 19.2 V 下降至 16.8 V,电压回滞幅度减小了约28.6%.然而,与NMSCR约 10-9A 量级的漏电流IL相比,SCR-N-MOS的IL较大,且具有缓慢退化的特点,尤其当ESD瞬态电流I从 2.0 A 增大到 3.2 A 时,IL从 2.8× 10-7A 逐渐退化至 1.7× 10-5A,表明该器件具有漏电流不稳定特性,不能构成有效的ESD防护.

2 漏电特性的分析与优化

2.1 仿真实验与分析

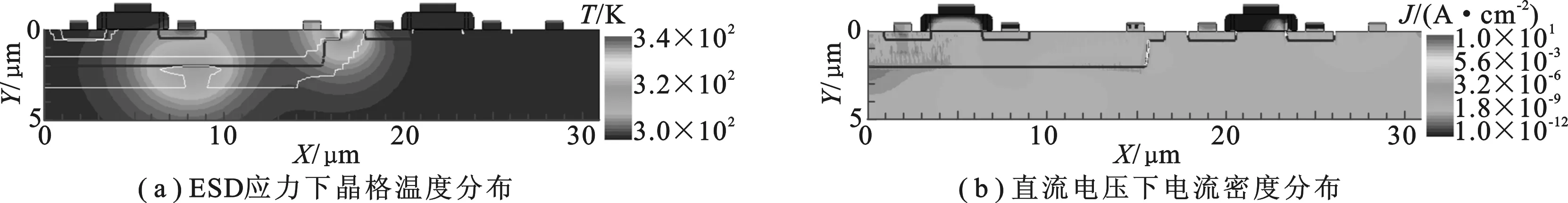

利用TCAD中Sentaurus软件仿真,探究器件在ESD应力作用下漏电流不稳定特性的内在物理机制.当对实验器件施加一上升和下降沿均为 10 ns、脉宽为 100 ns 的 10-4A 的ESD电流脉冲时,得到器件晶格温度分布如图3(a)和图3(c)所示,与NMSCR相比,SCR-N-MOS具有更高的晶格温度,且最高可达 1 160.5 K,表明器件内部的局部过热现象较严重.这是由于ESD应力作用下的N跨桥与P衬底、P衬底与NMOS漏端之间的空间耗尽区会逐渐交叠,形成高场耗尽区.该高场耗尽区会导致器件晶格温度的上升,并最终引起电流聚集效应.如图3(b)和图3(d)所示,在 10 V 直流电压作用下,NMSCR无明显电流路径,而SCR-N-MOS内部晶格温度较高区域存在一条由N跨桥、P衬底、NMOS漏端、P衬底和NMOS源端构成的漏电流路径.

图3 器件TCAD仿真结果

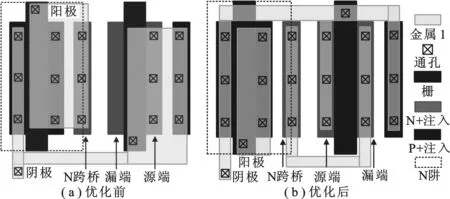

图4 SCR-N-MOS器件优化前后的版图

2.2 漏电特性的优化设计

若能抑制器件内部晶格温度的不均匀分布,便可有效地改善器件的漏电特性.SCR-N-MOS器件优化前后的版图如图4所示,现断开N跨桥与阳极端、NMOS源端与阴极端的金属连接,再将NMOS源漏互换,然后分别连接N跨桥与NMOS漏端、阴极端与NMOS源端,得到优化后的SCR-N-MOS.器件优化后,NMOS漏端与N跨桥之间的距离增加,有利于分散器件的高电场强度区域,削弱器件的热效应;同时NMOS漏端与阴极P+注入区之间的距离减小,可缩短ESD电流的泄放路径,有利于减小器件的触发电压;此外,由于N跨桥不再直接与阳极端相连,可降低N跨桥处电场强度,并且通过金属连线将ESD电流从N跨桥引至NMOS漏端后,可降低器件局部过热区域的电流密度,有利于防止器件在NMOS的栅端发生电流聚集效应.

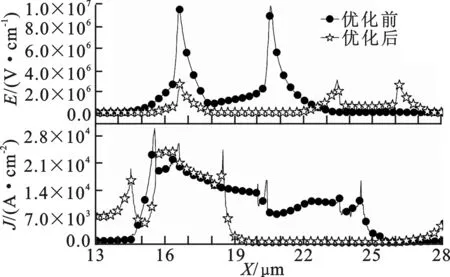

图5 纵向深度为0.1 μm处SCR-N-MOS优化前后的总电流密度与电场强度分布

在10-4A的ESD电流作用下,版图改进前后的SCR-N-MOS器件内部纵向深度Y为 0.1 μm 截面处的电流密度J和电场强度E分布曲线如图5所示.结果表明,与金属版图优化前相比,优化后SCR-N-MOS仅在该截面的横向长度X为 16.5~ 18 μm 处同时具有高电流密度和高电场强度,功率密度聚集效应明显削弱,而且电场强度峰值从 9× 106V/cm 大幅降至 3× 106V/cm. 因此,该器件内部晶格温度峰值也随之下降至 341.5 K,降幅达约70.6%,如图6(a)所示.同时,对版图优化后的SCR-N-MOS进行静态仿真,在 10 V 直流电压作用下,器件内部的电流密度J分布如图6(b)所示.与图3(d)相比,器件内部已无明显的漏电流路径,进一步证明该器件具有较好的局部过热抑制能力,有利于改善器件的漏电特性.

图6 优化后SCR-N-MOS TCAD仿真结果

图7 优化前后SCR-B-MOS的TLP特性曲线

SCR-N-MOS在版图优化前后的TLP特性曲线如图7所示.与优化前相比,优化后的SCR-N-MOS的触发电压从 16.8 V 降至 12.5 V,电压回滞幅度减小约13.8%.并且,由于器件N跨桥与NMOS源端之间的间距减小,降低了内部的导通电阻,增大了二次击穿电流,增强了器件的ESD鲁棒性.同时,在该器件发生二次击穿前,其IL能稳定在 10-9A 量级.实验测试结果表明,该优化方法可避免器件发生漏电流退化现象,提高器件的ESD防护可靠性.

3 结 束 语

基于0.25 μm BCD工艺制备了NMSCR和SCR-N-MOS器件,TLP测试结果表明,SCR-N-MOS的电压回滞幅度可降低约28.6%,但器件的漏电较大且不够稳定.TCAD仿真结果表明,热效应是造成器件漏电特性较差的主要原因.通过调整SCR-N-MOS的版图及其金属布线,不仅改善了器件的漏电特性,降低了电压回滞幅度,还提高了ESD鲁棒性.版图优化后的SCR-N-MOS器件适用于具有小回滞窄ESD设计窗口的片上集成电路的ESD防护.