基于FPGA的高速数据采集系统的设计与实现

汪明

摘要:为有效解决高速数据采集过程中数据的实时性和传输速率等问题,对多通道数据进行有效的检测和控制,笔者开发设计出一种基于FPGA的高速数据采集系统,通过调试和试验得出系统具有良好的性能,为后期研究提供一定的理论基础。

关键词:FPGA;高速数据采集;设计

引言

国外虽然有专业的测量设备,能够实现对千兆频率的数据采集,但是价格昂贵、不适用。国内相关技术人员对于数据的采集和处理技术格外重视,虽然能够达到数据的高速采集和处理,但是国内没有独立的研发部门,高端测试仪器价格昂贵,并受环境因素制约,使其不能有效与嵌入式计算平台进行集成,因此,本文提出基于嵌入式的计算机数据采集模块系统,可以完成对数据的高速采集。

一、整体方案与系统架构

高速数据采集系统包括数据采集、通讯和处理模块、信号调理以及电源模块等。数据采集系统将输入的模拟信号转换为数字信号进行传输,为保证高速数据传统系统的稳定性,应逐渐攻破并行数据流的时序及数据存储和处理等方面的技术性难题。本文提出的一种基于CPCI嵌入式的数据采集系统(图1),包含软硬件的方案构成,其中硬件方案主要包含是CPCI底板、CPU模块、数据采集模块、固态盘模块、信号调理模块及电源模块等,其中CPU模块作为核心模块,可实现数据的高速传输;软件方案包含数据采集模块和数据显示界面。

二、数据采集硬件模块设计

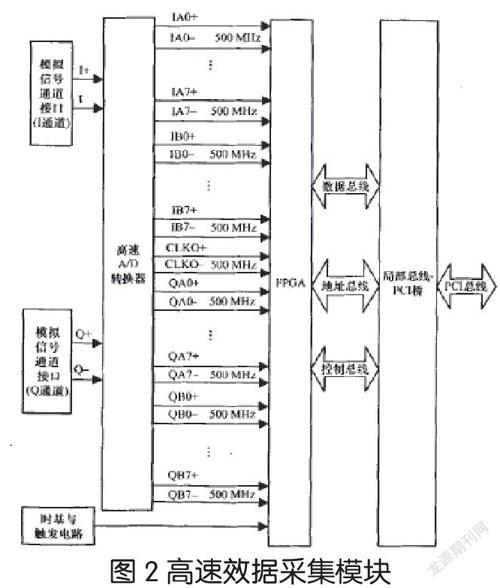

基于FPGA的高速数据采集平台(图2 为高速效据采集模块)在CPCI底板和CPU模块核心模块控制下数据控制平台,其中各项模块和电源等完全兼容CPCI标准底板,使整个系统具有可靠性和扩展性,实现系统的模块化处理。其中,高速数据采集系统包含高速A/D转换器、模拟通道接口和触发电路等硬件,数显前端模拟信号与控制信号可有效连接。

三、FPGA逻辑设计

随着信息化快速发展,使得信息系统对于数据的采集、捕获等方面提出更高的技术要求,需要尽可能增大信号的频带范围,最大化扩大对信息的获取,其要求系统对于数据的采样频率和采样信号带宽等相应的标达到更高的标准,因此使得相应的控制手段更加灵活和方便,FPGA技术应运而生。文中系统选用StratixlI系列器件,因其采用ALM使得该器件具有更高的性能和逻辑扩展性,同时具有更强的DSP,能有效支持14J。该设计采用的主动串行与JTAG方式有效结合,可以将FPGA芯片的MSELx(其中x的值为0、1、2和3)引脚设置合理的电平;同时,在其内部功能上是根据具体方案设定,在考虑该平台扩展性的同时,对其系统资源上进行科学合理的评估。因此,该设计具有广泛的通用性、选择性,一般来说,能够实现一般数据的信号处理。

四、高速采集电路与高速数据流实时存储

对于高速数据采集系统来说,其采集电路和数据流的存储是设计的关键之处。通过对该整体系统的选型和设计,实现高速数据采集系统的完整性、数据流的降速和存储,最终确认数/模转换器与FPGA有效结合,实现数据的高速处理。该方案设计的单通道的采样率为1 GS/s,双通道的采样率为2GS/s,同时能够高速捕获数据并满足实时存储等功能。

五、系统调试及结果分析

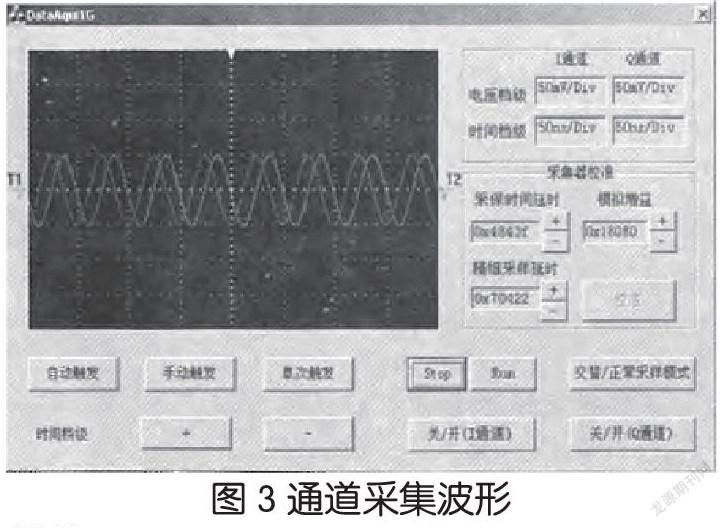

完成对数据的高速传送,需要对整个数据系统进行调试。采样定理是将采集到的模拟信号在不失真的情况下转换为相应的数字信号,其中设备的采样频率应大于模拟信号的两倍。但是在验证过程中,笔者发现数据采集模块的采样率是采样模拟信号的5倍;同时系统性能和功能验证采用的是Agilent LXl33220A标准信号源等,采用的试验环境是Windows操作系統,及相应的人机界面控制软件(如图3)。其中,输入的模拟信号为20MHz/100mV正弦波。

六、结论

与传统的数据采集卡相比,本文设计开发的高速数据采集系统具有良好的功能,能够快速实现数据的传送。同时,该数据采集系统能够广泛应用多种同步数据采集的场合,是一种较理想化的数据采集模式。在后续的研究过程中,可以采用高性能的ADC系统,也可以对数据的采样率和缓存器进行优化和改革,提供更高效的数据处理功能,有效提升对于数据的采集和处理速度,最大化提升数据的采集能力。

参考文献:

[1]吴明锋. 基于FPGA的高速数据采集系统设计与实现[J]. 移动信息, 2018, (7):47-48.

[2]常高嘉, 冯全源(西南交通大学微电子研究所). 基于FPGA的高速数据采集系统的设计与实现[J]. 电子器件, 2012, (5):615-618.