基于FPGA的一种DDR4存储模块设计

谢晨 卓敏

摘?要:5G通信的主要特征包括“高速率、大带宽”,为了满足高速率、大带宽数据的传输要求,需要一种存储技术对数据进行存储。本文就存储技术结合DDR4协议,设计了一种DDR4传输机制,本研究采用高性能的XCVU9P系列的FPGA芯片作为控制芯片,使用其内部自带的DDR4 SDRAM(MIG)IP核进行例化核设计。经过验证,实现在250 MHz时钟下对DDR4 SDRAM的读/写操作,数据无丢失,能够保证高速率、大带宽数据正常传输,该传输机制具有良好的可靠性、适用性及有效性。

关键词:DDR4;高速率;大带宽;FPGA

0 引言

随着通信技术的不断发展,5G技术作为当前新一代通信的热点技术将面临很多研究课题,除了要传输低速率、小带宽数据外,还需要分析高速率、大带宽数据,分析带宽从100 MHz提高到1 GHz,甚至更高带宽。当前最大的难题就是5G高速率的传输将会导致信号的带宽变大,因此对这些高速率的数据流进行实时处理将变得更加困难[1]。

伴随着数字化的高速发展,目前存储是大容量数据存储系统的核心部分,甚至会影响到系统的性能。DDR最大的特点就是传输速率是时钟的两倍,数据同时在上升沿和下降沿同时采样[2]。

本文提出一种基于DDR4 SDRAM的高速数据缓存技术,主控器选用Xilinx公司XCVU9P系列FPGA芯片,数据缓存器选用MT40A512M16HA-083E,通过对DDR4 SDRAM的存储寻址原理及DDR4 IP核的读写控制逻辑的研究,实现了在250 MHz的时钟下,DDR4 SDRAM能够正常进行读写操作。经过测试验证,读写数据正常,无数据丢失。

1 整体设计方案

整体设计方案使用模块化,主要包括光口传输模块、DDR4存储模块、SRIO接口模块。本设计主要对控制芯片FPGA内部逻辑进行了优化设计,其中包括DDR4控制器、不同时钟域之间的数据缓存FIFO。整体方案传输流程如图1所示。

● 光口模块:主要是接收采集模块传输过来的数据。

● DDR4存储模块:用于缓存数据,由于SRIO接口的数据传输速率慢,需要通过DDR4存储模块先将高速数据存储到DDR4中,然后再通过SRIO的时钟将数据传输给SRIO接口模块。

● SRIO接口模块:接收DDR4读出来的数据,然后传输给上位机进行测试分析。

2 DDR4 SDRAM内部结构

DDR4 SDRAM是一种内部可配置高速动态随机存储器,其内部由多个Bank组成,Bank又是由很多行和列构成[3],DDR4的寻址操作就是对行列地址进行操作。

DDR4存储器有几个重要概念,即Bank、Bank Group及Page,例如512Mx16的8 Gb容量的DDR4,内部主要包括2个Bank Group,每个Bank Group包括4个Bank[3]。每个Bank是由多个Page组成的,通过多Page地址去选择相应的Page。

3 DDR4控制器模块设计

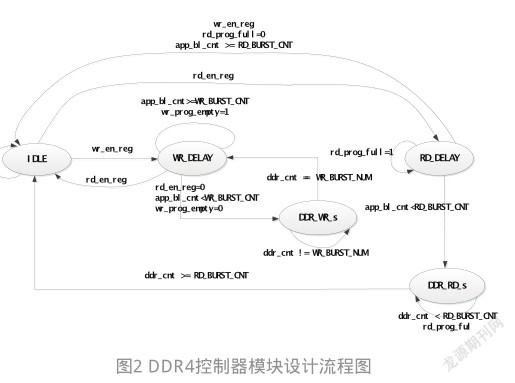

DDR4控制器模块设计如图2所示,将控制器分为IDLE、WR-DELAY、DDR-WR_s、RD_DELAY和DDR_RD_s五个模块。

● IDLE:初始化状态。主要对DDR4内部的信号进行初始化。当收到rd_en_reg和rd_dat_s_reg信号同时有效时,将进入RD_DELAY状态;当收到wr_en_ reg信号有效时,进入WR_DELAY状态;如果在该状态下没有收到相应的有效信号将继续保持该状态。

● WR-DELAY:写等待状态。当在此状态下收到rd_en_reg有效时将会跳到IDLE状态;在没有收到rd_ en_reg有效时,根据条件app_bl_cnt >= WR_BURST_ CNT来判断是否已经写到规定的数据量,如果已经写到规定的数据量,将继续保持在该状态,等待其他有效信号的到来,如果没有写到规定的数据量,判断写FIFO的wr_prog_empty信号,如果wr_prog_empt无效则跳转到DDR_ WR_S状态,反之wr_ prog_empt有效,则继续在该状态下等待有效信号到来。

● DDR_ WR_s:写状態。此状态主要是往DDR4里写数据,由于DDR4 IP核内的Burst Length设为了8[4],所以根据条件ddr_cnt == WR_BURST_NUM来判断,当ddr_cnt计数到了WR_ BURST_NUM的值时,会跳转到WR-DELAY状态,如果没有计数到WR_BURST_NUM的值,则继续保持在该状态。

● RD_DELAY:读等待状态。当在此状态下收到wr_en_reg有效时将会跳转到IDLE状态;在没有收到wr_en_reg有效时,根据读FIFO的rd_prog_full信号来判断,如果rd_prog_full有效时则继续在该状态下等待,若无效则根据条件app_bl_cnt >= RD_BURST_ CNT来判断,如果计数达到了设定的读数据量,则会跳转到IDLE状态,若没有到达设定的读数据量,则跳转到DDR_RD_s状态。

● DDR_RD_s:读状态。此状态主要是将DDR4里的数据往外读,根据条件ddr_cnt >= RD_BURST_ CNT来判断,当计数达到设定的读数据量时则会跳转到IDLE状态,如果没有达到设定的读数据量,且读FIFO的rd_prog_full信号有效,则会继续在该状态下读取DDR4里的数据。

4 仿真验证

采用Vivado 2018.3软件,其中FPGA芯片型号为XCVU9P-flga2104-1-i,进行开发板上验证。在光口模块产生一组递增数,通过光口将数据发送给DDR4存储模块。通过在ILA抓取相应的信号来观察DDR4。

图3是通过ILA抓取的DDR4内部信号状态图[5]。

通过图3可以看出,一开始DDR4处于初始化状态,当wr_en_reg变成高电平时,state跳转到WR_DELAY状态;当wr_prog_empty变成低电平时,state跳转到DDR_WR_s状态。之后,当app_bl_cnt计数到96250时,state跳转到WR_DELAY;如果对写数据部分放大,可以看出数据是递增数;当rd_en_reg和rd_dat_s_reg同时有效时,state从IDLE状态跳转到RD_DELAY状态,当rd_prog_full为低电平时,且app_bl_cnt未计数到RD_BURST_CNT,这个state从RD_DELAY状态跳转到DDR_RD_s状态;当ddr_cnt计数到768000时,state从DDR_RD_s状态跳转到IDLE状态;图4是对读数据部分放大,可以看出数据是正整数。

5 结束语

本研究在Xilinx公司的XCVU9P系列FPGA芯片上完成了DDR4存储模块的读写状态机的设计、代码编写以及验证。使用其内部自带的DDR4 SDRAM(MIG)IP核进行例化核设计。经过开发板上验证,实现在250 MHz时钟下对DDR4 SDRAM的读/写操作,数据无丢失,能够保证高速率、大带宽数据正常传输,该传输机制具有良好的可靠性、适用性及有效性。

参考文献:

[1] 袁行猛,陈亮,徐兰天.基于CPRI协议的5G基带数据传输技术的研究与实现[J].电子产品世界,2019,26(04):41-45+61.

[2] 张亚军.实时频谱仪的数字中频处理设计与实现[D].成都:电子科技大学,2017.

[3] 汪继友.一种特殊应用场景下的DDR4写缓冲设计与验证[D].合肥:安徽大学, 2019.

[4] 苏健渊.基于ARM+FPGA的多屏图像显示系统研究[D].西安:西安电子科技大学, 2014.

[5] 武春锋.基于DDR4 SDRAM的光电图像实时存储技术研究[D].北京:中國科学院大学,2018.