凸起焊盘板外层线路工艺制作技术研究

文/吴柳松 张军杰 刘振宁

0 引言

凸起焊盘(Raised PAD)技术是下一代印制电路板(PCB)服务器中央处理器(CPU)控制模块基板的主要应用技术之一,常见技术参数要求Raised PAD高度为50μm,此要求决定其PCB制作技术的重点在外层线路。镀铜Raised PAD做外层线路方法,除了用真空压膜制作线路,也可用油墨制作线路(先干膜盖孔),但此种工艺制作外层良率较低。本研究提出先制作出外层线路,然后在线路层再镀Rai sed PAD,解决Raised PAD使用油墨制作外层良率低问题,并且能够很好解决Raised PAD的高度增高,不再受到外层线路良率限制,实现一定程度的工艺技术突破。

1 技术概述

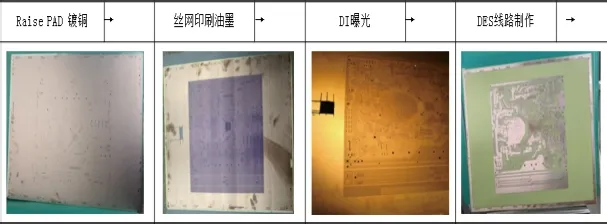

Raised PAD技术类产品(见图1)为美国超威半导体公司、英特尔公司等大客户应市场发展需求,应用前景广阔。Raised PAD技术指标要求较高,高度为50μm,比绿油厚度高25μm,分布在球栅阵列封装(BGA)区域,且PAD是独立连线和夹线设计,因而,Raised PAD产品特征决定其制作工艺制作难点在镀铜后外层线路制作。外层线路制作使用压干膜方法,但必须要用真空压膜才可把铜面PAD高低处覆盖上干膜,曝光后DES生产出外层线路图形。也有使用油墨来制作线路。油墨工艺可分丝网印刷、静电喷涂和浸油,无论采用哪种工艺制作,先用干膜盖PTH孔(预防油墨流入PTH孔),再把湿墨均匀覆盖Raised PAD制作出外层线路。由于Raised PAD高低差造成油墨厚薄不均,影响油墨底层的曝光不良,增加了影像转移难度,导致外层良率较低。本研究提出先制作线路,再镀铜Raised PAD的方法,不仅能在无真空压膜设备下作业,且相比干膜盖孔后用油墨做线路的工艺方法更精简,缩短工时和节约成本。

下文介绍5种方案制作线路的工艺方法,主要从工艺流程、生产设备、使用物料等方面进行剖析,给出一套可行的技术方案,并阐述电镀、外层和防焊制程的制作参数及关键品质标准。

图1 Raised Pad 板外观

2 技术难点

2.1 技术现状分析

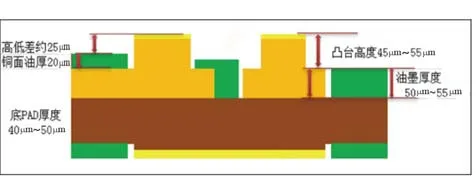

Raised PAD制作成品要求高度50±5μm,其高度比绿油厚度高25μm,如图2所示。

图2 Raised Pad介质层厚度

2.2 Raised Pad 工艺流程

针对外层线路不同工艺方法,Raised Pad板的制作工 艺全流程方案,统计整理如下:

(1)方案1:真空压膜法。具体流程如下:

开料→内层→AOI(自动光学检测)→压合→钻孔→板电→干膜1→烘烤→镀铜Raised PAD→镀金→去膜→真空压膜→线路曝光→DES→外检AOI→防焊→文字→干膜2→化金→去膜→成型→电测→FQC→清洗→包装。

(2)方案2:“干膜封孔+丝网印刷油墨法”。具体流程如下:

开料→内层→内检AOI→压合→钻孔→板电→干膜1→烘烤→镀铜Raised PAD→镀金→去膜→热辊压膜→曝光→显影→印刷油墨一面→烘烤→印刷油墨另一面→烘烤→曝光→DES→外检AOI→防焊→文字→干膜2→化金→去膜→成型→电测→FQC→清洗→包装。

(3)方案3:“干膜封孔+浸油工艺法”。具体流程如下:

开料→内层→AOI→压合→钻孔→板电→干膜1→烘烤→镀铜Raised PAD→镀金→去膜→热辊压膜→曝光→显影→烘干→浸油→烘烤→线路曝光→DES→外检层AOI→防焊→文字→干膜2→化金→去膜→成型→成测→FQC→清洗→包装。

(4)方案4:“干膜封孔+静电喷涂法”。具体流程如下:

开料→内层→AOI→压合→钻孔→板电→干膜1→烘烤→镀铜Raised PAD→镀金→去膜→压膜→曝光→显影→静电喷涂→预烤→曝光→DES→外检AOI→防焊→文字→干膜2→化金→退膜→成型→成测→FQC→清洗→包装。

(5)方案5:先外层线路后镀Raised PAD。具体流程如下:

开料→内层→AOI→压合→钻孔→板电→外层线路→DES→外检AOI→沉铜→干膜1→烘烤→镀铜Raised PAD→镀金→去膜→防焊→文字→干膜2→化金→去膜→成型→成测→FQC→清洗→包装。

3 Raised Pad线路板制作工艺

3.1 Raised Pad板的电镀工艺流程

Raised Pad电镀工艺,包含镀铜与镀金两个流程。从干膜到镀金制程相关参数如下:

(1)压膜:板电后,经过前处理,清洗烘干板面后,使用热辊压膜机压上一层感光抗蚀膜。干膜型号W265,此干膜有65μm,保证镀铜Raised Pad能镀上大于50μm的厚度。

(2)曝光:把压膜后的板放到曝光机台面上,放上底片,使用UV光照射,作用是通过底片把图形转移到板面的干膜层上(LDI曝光机直接镭射光作业把图形转移到板面的干膜层上,无需底片)。其生产制作参数为曝光能量280mj~300mj,曝光能量尺6±1格。

(3)显影:将曝光完后的板静置30min后,撕去干膜表层Mylar,放进显影机,利用显影剂药水(碳酸钠)把未曝光的干膜冲洗掉,留下曝光过的干膜覆盖图形。其生产制作参数为线速1.5m/min~2m/min,碳酸钠浓度1±0.2%。

(4)烘烤:把显影后的板插于框架,放置在箱式烤箱内,设定温度120°,时间10min~20min,目的是使干膜和面铜结合得更牢固,预防后续电镀药水的渗镀。

(5)镀铜Raised Pad(凸台):把烤后的板冷却常温后,放到镀铜线上进行镀铜作业。其生产制作参数参考露出铜面积,设定电流乘以镀铜时间来计算出得到所需的凸台高度镀铜面积(0.06ft2)/镀铜(15ASFX120min)/镀锡(1ASFX10min)。

(6)镀金:Raised Pad板镀铜后,直接镀金作业,要求镀金厚度最小:30U",镍厚118U"~300U",使用3#镀金线。生产制作参数为电流密度(Au:11ASF*Ni:12ASF),线速:0.7m/min,设定面积:5000mm²。

通过以上制程后,Raised PAD已制作完成,如图3~图5所示。

图3 BGA区域镀Raised Pad

图4 Raised Pad放大10倍

图5 Raised Pad切片

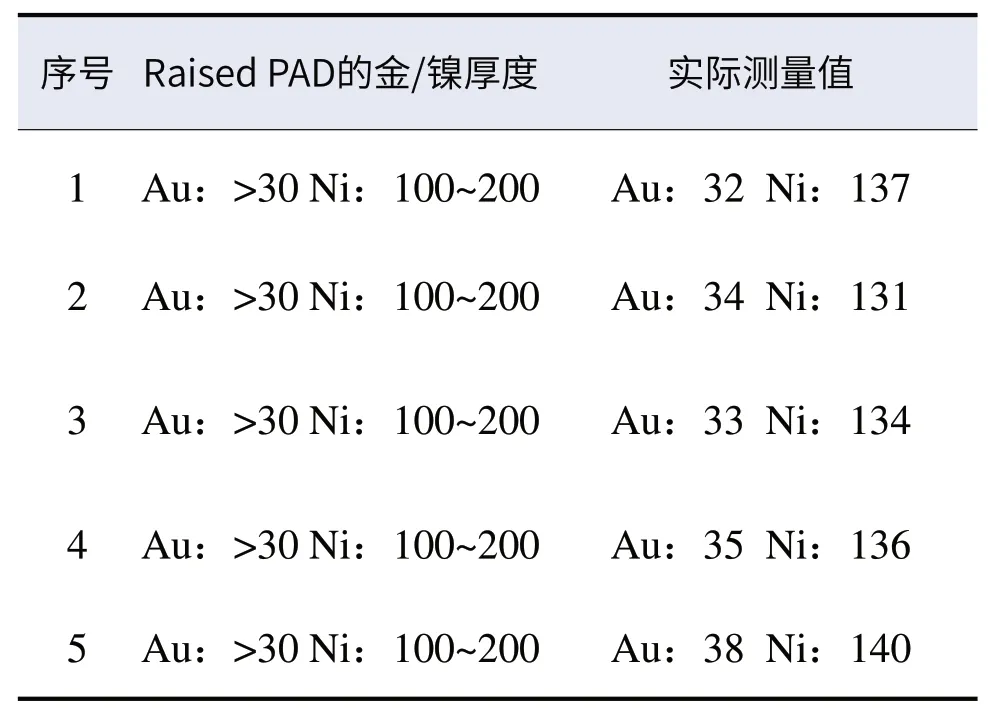

使用切片分析统计电镀Raised PAD的厚度,经测量,数据实际值都在标准范围内(见表1、表2)。

表1 Raised PAD镀铜切片测量数据 单位:μm

表2 Raised PAD镀金测量数据 单位:U〞

3.2 Raised Pad外层线路制作工艺

3.2.1 先镀铜Raised Pad后制作外层线路外层图形的工序

(1)去膜。镀金后Raised Pad板放进去膜线作业,其原理利用去膜药剂(NaOH),把干膜从板面上去除掉,保持板面洁净。生产制作参数:线速1.0m/min~1.5m/min;碳酸钠浓度3%~5%。

(2)压膜。去膜后Raised Pad板经过前处理,清洗烘干板面后,使用热辊压膜机压上一层感光抗蚀膜,干膜型号HD240,此干膜制作干膜封孔之用,防止后续印刷油墨时油墨入孔烤干导致孔内油墨清除不干净。主要参数:线速2.0m/min;压膜温度110℃±10℃。

(3)曝光。把压膜后的板放到曝光机台面上,放上底片,使用UV光照射,通过底片把图形转移到板面的干膜层上。其生产制作参数:曝光能量90mj~110mj, 曝光能量尺6±1格。

(4)显影。曝光完后的板静置30min后,撕去干膜表层Mylar,放进显影机,利用显影剂药水(碳酸钠)把未曝光的干膜冲洗掉,留下曝光过的干膜覆盖图形。生产制作参数:线速4.0m/min~4.5m/min;碳酸钠浓度1%±0.2%。

(5)丝网印刷一面。把显影后板使用丝网印刷机,进行单面印刷作业,在板面上印上一层均匀的湿膜(线路油墨或防焊油墨,解析度达到制作外层线路的要求即可)。生产制作参数:刮刀速度1.5m/min~2.0 m/min;角度45°;压力1.5kg/cm²~2kg/cm²。

(6)预烤。把印好单面的板插框架,放进烤箱预烤,温度75℃,时间5min~10min。目的为把湿膜烤干(不粘手为准)。

(7)丝网印刷另一面。把印刷一面油墨烘烤干的板在同机台进行另一面印刷作业,在板面上印上一层均匀的湿膜。其生产制作参数:刮刀速度1.5m/min~2.0m/min;角度45°;压力1.5kg/cm²~2kg/cm²。

(8)预烤。把印好双面油墨的板插框架,放进烤箱预烤,温度75℃,20min~25min,把湿膜烤干(不粘手为准进行检验),预防粘底片给生产造成不便。

(9)曝光。把印刷双面油墨烤干的板放到曝光机台面上,放上底片,使用UV光照射作业通过底片把图形转移到板面的湿膜层上(LDI曝光机直接镭射光作业把图形转移到板面的湿膜层上,无需底片)。制作生产参数:曝光能量90mj~110mj;曝光能量是5~7格。

(10)酸性蚀刻线(DES)。即显影机(Deve loping)、蚀刻机(Etching)、去膜机(Stripping)的水平线连线作业。把曝光过的板放进显影机,显影出所需要的图形,不需要的露出铜面,经过蚀刻机内酸性蚀刻液腐蚀掉其铜面,留下保护膜覆盖图形,经过去膜机内去膜药剂(氢氧化钠)把覆盖铜面上的保护膜去掉,得到铜层线路图。生产参数:显影机速度:3.5m/min~4m/min,压力1.5kg/cm²~2.0 kg/cm²,碳酸钠浓度1%±0.2%;蚀刻机速度:1OZ铜厚为参 考,4.5m/min±0.5 m/min,压 力2.0kg/cm²~3.0 kg/cm²;去膜机速度:4m/min~5m/min,压力1.5kg/cm²~2.0 kg/cm²,氢氧化钠浓度3%~5%。

(11)外检AOI。针对蚀刻出外层线路图形进行品质检验,与CAM客户原稿设计图形比对是否完整;如不完整,存在缺失项,查看判别,检修,直到符合客户需求品质标准。其作业,检验制程缺陷,预防品质不良出现,及时发现问题、解决问题。

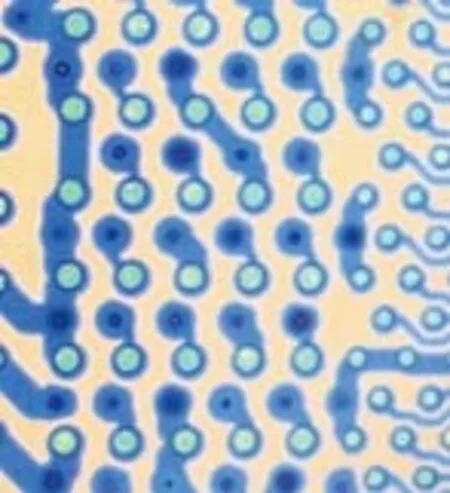

图6~图8为Raised Pad外层线路的不同工艺制作、不同工序所呈现出当时的线路。

图6 真空压膜法线路显影后

图7 “干膜+油墨”法线路显影后

图8 Raised Pad线路蚀刻后

3.2.2 先外层线路后制作镀铜Raised Pad的工序

(1)压膜。板电后,经过前处理,清洗烘干板面后,使用热辊压膜机压上一层感光抗蚀膜。干膜型号HD7240,此压膜温度110℃±10℃,压膜速度2.5m/min±0.5m/min。

(2)曝光。把压膜后的板放到曝光机台面上,放上底片,使用UV光照射,通过底片把图形转移到板面的干膜层上(LDI曝光机直接镭射光作业把图形转移到板面的干膜层上,无需底片)。生产制作参数:曝光能量80mj±10mj, 曝光能量尺6±1格。

(3)显影。曝光完后板静置15min后,撕去干膜表层Mylar,放进显影机,利用显影剂药水(碳酸钠)把未曝光的干膜冲洗掉,留下曝光过的干膜覆盖图形。生产制作参数:线速1.5m/min~2m/min;碳酸钠浓度1±0.2%。

(4) DES.生产参数:显影机速度3.5m/min-4m/min,压 力1.5kg/cm²~2.0 Kg/cm²,碳 酸 钠 浓度1±0.2%;蚀刻机速度1OZ铜厚为参考,4.5m/min±0.5 m/min,压力2.0kg/cm²~3.0 kg/cm²;去膜机速度4m/min~5m/min,压力1.5kg/cm²-2.0 kg/cm²,氢氧化钠浓度3%~5%。

(5)外检AOI(光学自动检测设备)。针对蚀刻出外层线路图形进行品质检验,与CAM客户原稿设计图形比对是否完整;如不完整,存在缺失项,查看判别,检修,直到符合客户需求品质标准。其作业,检验制程缺陷,预防品质不良出现,及时发现问题、解决问题。

(6)沉铜。把外层线路独立的单元,通过沉铜线,沉积一层薄的铜层连接起来,为后面电镀提供能导电的导体。此为化学铜在线路图形之间作为电镀导体的一种运用。生产参数:线速2m/min。

(7)镀铜Raised Pad工序制作相关参数参照以上Raised Pad板的电镀工艺流程工序(1)~(6)。

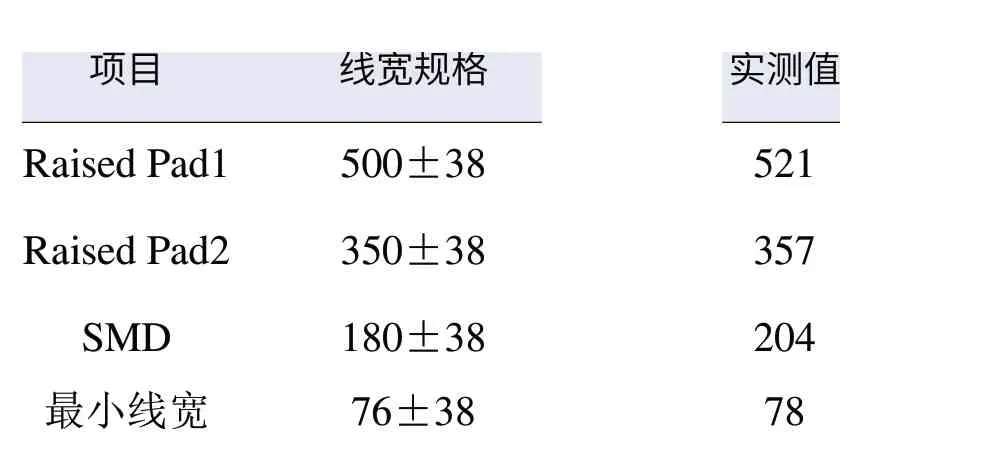

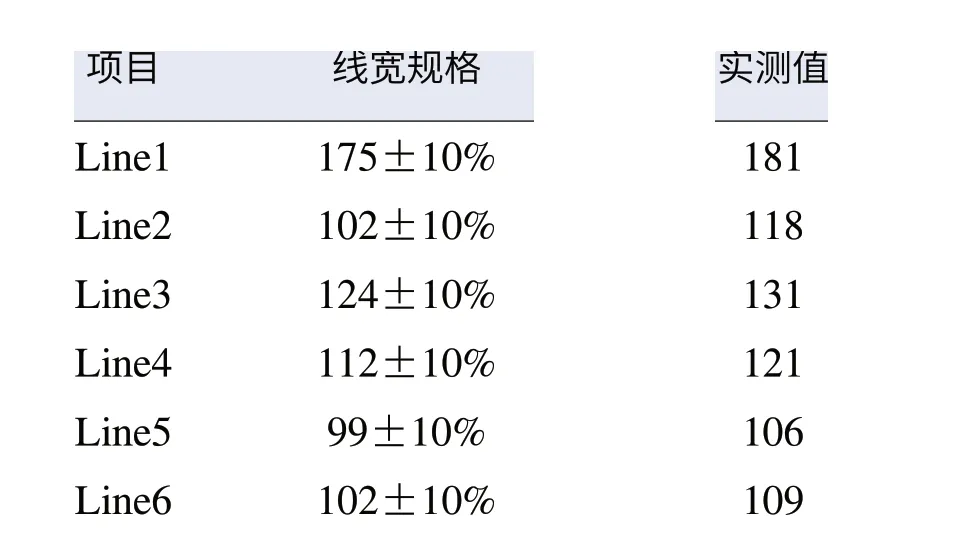

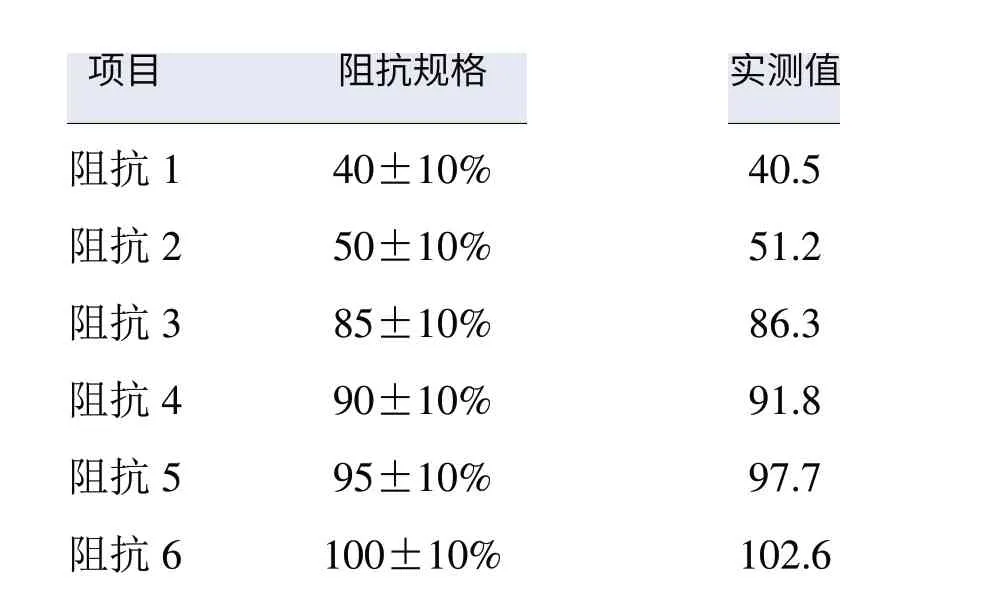

Raised Pad外层线路制作依据基材铜经过板电后,整体铜厚在35μm~40μm。按照铜厚35μm外层铜厚进行补偿线宽作业,其正常补偿38μm。现首件测量线宽数据在中值偏上,符合生产要求。根据数据显示(见表3、表4、表5),Raised Pad板的首件板制作完,线宽测量数据以及相关阻抗测量值在中值偏上,都在标准范围内,符合生产要求,后续批量生产。

表3 TOP面Raised Pad线宽测量数据 单位:μm

表4 Bottom 面阻抗线宽测量数据 单位:μm

表5 Bottom 面阻抗值测量数据 单位:Ω

4 Raised Pad线路板制作工艺对比

4.1 先制作Raised Pad后制作线路的工艺流程

先镀铜Raised Pad后线路制作,由于Raised Pad存在高低差,无真空压膜设备,只能选用油墨制作线路。预防油墨入孔去墨不净,PTH孔先使用干膜盖孔,再丝印油墨(或喷涂,浸油作业)。由于工艺流程长,油墨在Raised Pad之间厚薄不均,抗蚀刻能力差异,导致最终线路良率较低。 见图9。

图9 PCB先镀铜Raised Pad后制作外层线路工艺流程

4.2 先制作线路后制作Raised Pad的工艺流程

先制作外层线路,由于在板电后压膜生产,不存在Raised Pad高低差影响,因而,其外层制作的良率较高,达90%以上,可到达到方案1使用真空压膜设备生产Raised Pad板的外层良率。见图10。

图10 PCB 板先制作外层线路后镀铜Raised Pad工艺流程

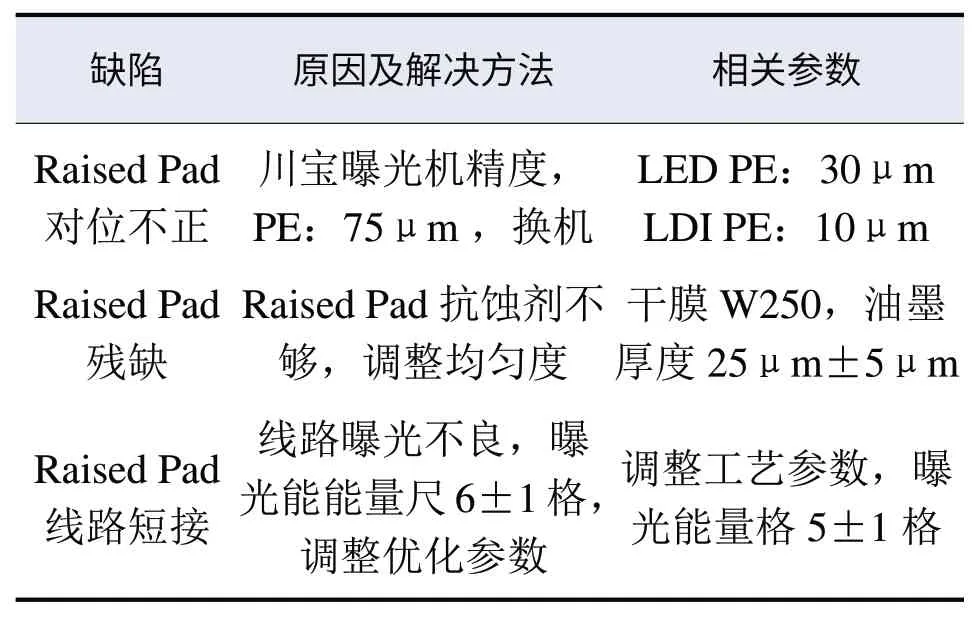

4.3 Raised Pad线路制作的缺陷与工艺改进

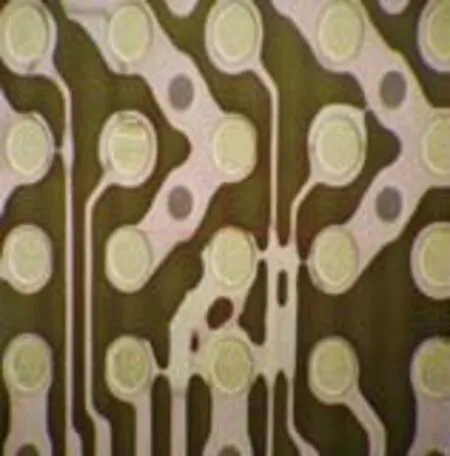

Raised Pad在制作线路时,由于Raised Pad存在高低差,导致抗蚀剂干膜或油墨在覆盖Raised Pad的全面、填充侧壁时,其厚度受工艺技术设备局限性出现不均匀现象,影响抗蚀刻效果(见图11~图13)。具体改进对策见表6。

图11 Raised Pad对位不正

图12 Raised Pad残缺

图13 Raised Pad线路不良

表6 Raised Pad制作线路缺陷工艺改善主要对策

5 Raised Pad线路制作方案比较

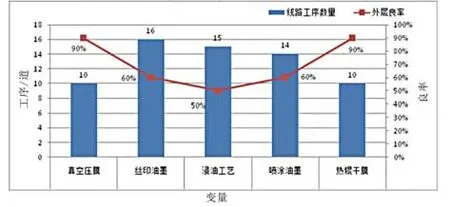

针对5种方案的设备,依据不同制作工艺流程及生产产品良率进行统计比较,见图14、表7。

图14 Raised Pad板不同工序制作外层良率

表7 Raised Pad板不同工艺方法相关数据统计

统计分析以上5种方案流程,前4种先镀铜Rais ed Pad后制作线路,方案5刚好相反,其优势如下:

A.缩短工序,可减去使用干膜盖孔和湿墨制作线路两个工序。

B.精简工艺,省略湿墨印刷制作线路,减少一次影像转移工艺。

C.节省工时,沉铜(10分钟)与丝印油墨(3小时-制作10PNL板计时)耗时相差甚远。

D.物料节省,省去湿墨的物料和工治具的消耗。

E.良率提升>30%,即方案5的外层良率90%相比方案2、方案3、方案4的外层线路良率50%~60%,差异>30%。

综上所述,Raised Pad 外层线路制作,不同的工艺制作方法生产良率存在差异,后续工艺将不断改善,优化参数,改良方法,不断提高产品良率,持续改善之。