基于FPGA的两级冗余编码系统

李圣昆,郝少帅,杨玉华,王淑琴,李 金

(1.中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051;2.上海航天电子技术研究所,上海 201109)

0 引言

测试人员不便直接测试的极端环境(如高温、高空、强磁等)往往需要将测试数据远距离传输到地面接收设备。目前常用的传输方式包括并行传输和串行传输。由于数据线接口过多,并行总线传输方式在电磁干扰较大的环境中,数据传输的可靠性下降严重;串行总线包括PECL、RS422、RS485、HOTLink以及LVDS等。PECL的接口电平逻辑不兼容标准逻辑[1];传统的串行通信如RS232、RS422和RS485的传输速率太低,不能满足实时监测的需求。相同环境条件下,LVDS总线相较HOTLink具有更高的传输速率和更远的传输距离,因此采编设备和地面测试设备的通信总线选为LVDS总线。

LVDS是一种低振幅差分传输技术,由于传输电压仅为350 mV,在没有任何补偿电路的情况下,LVDS信号仅能在几米内实现无误码传输[2];当传输距离超过10 m后,传输信号就会由于电缆损耗等问题,变得无法识别。当下,现有的优化方案主要有硬件电路和软件设计两方面,硬件电路中,添加驱动器和均衡器,LVDS信号的无误码传输距离增加到了70 m[3],但是仍然无法达到150 m回传的任务要求。本文针对恶劣条件下数据远距离传输中可靠性不高的问题,提出了基于FPGA的两级冗余编码系统。

1 系统的硬件优化

信号在电缆中传输时,受到趋肤效应以及介质损耗的影响会产生传输衰减[4],趋肤效应产生传输衰减与传输频率的平方成正比关系,介质损耗产生的衰减与传输速率也是正比关系[5],电缆过长和速率变大都会导致传输衰减的增大,衰减过大时便会产生误码[6]。为了实现数据的无误码传输,文章通过对传输信号使用了均衡以及预加重技术[7],补偿传输过程中的信号衰减,从而实现远距离传输。

整个传输系统如图1所示,由采编存储器、测试台和屏蔽双绞线组成。采编存储器将采集到的信号高速回传给测试台进行处理;测试台接收采编存储器的数据同时发送指令控制整个采集过程;屏蔽双绞线连接测试台和采编存储器实现数据交互。

图1 系统总体设计框图Fig.1 Overall design block diagram of the system

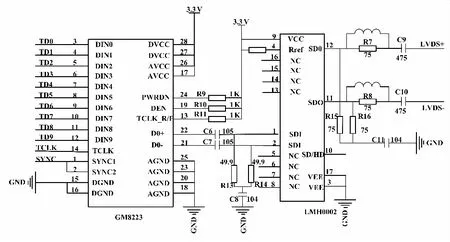

1.1 LVDS发送接口

LVDS发送模块电路如图2所示,编码器选用成都振芯公司的GM8223,电缆驱动器选用TI公司的LMH0002,编码器的传输速率最高为到660 Mb/s,而电缆驱动器的速率超过1 Gb/s,都可以实现高速传输的任务要求,发送模块工作时编码器会将接收到的时钟嵌入数据流中,再转化成串行数据流发送至LMH0002,电缆驱动器对接收到数据流信号进行预加重,把差分输出电压拉高到2.5 V后输出,补偿信号在传输时的衰减,提高数据传输的距离。

图2 LVDS发送模块电路Fig.2 LVDS transmission module circuit

图2中590 Ω的R12用来控制驱动器的输出电压为2.5 V。为了降低由于连接器而引起的回波损耗,用电阻和电感构建了损耗网络[8]。同时为了降低终端反射引起的信号衰减,R13和R14用于阻抗匹配。

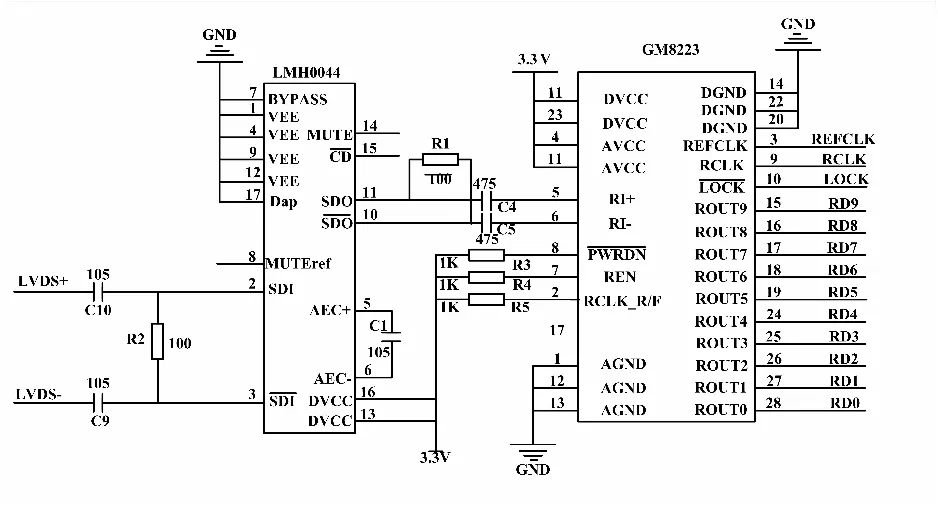

1.2 LVDS接收接口

LVDS接收模块电路如图3所示,解码器同样选用成都振芯公司的GM8224,均衡器选用TI公司的LMH0044,解码器的传输速率与编码器相同,可以实现高速数据接收,接收模块工作时均衡器LMH0044会对从电缆中接收到的衰减数据流进行滤波,再通过恢复电路完成信号的重建,重建后将串行数据流发送至GM8224进行解码,解码后恢复为十位数据和一位时钟。和发送模块相同,R1和R2也是用于用于降低终端发射阻抗匹配电阻[9]。

图3 LVDS接收模块电路Fig.3 LVDS receiving module circuit

2 软件逻辑优化

各种校验码的纠错能力如表1所示。

表1 校验码特性表

文章的软件优化采用两级冗余编码的方式,由表1可知,汉明码加奇偶校和BCH码加奇偶校验在纠错能力上都大于单一的奇偶校验、汉明码和BCH码,但是汉明码的实现比BCH码简单,所以文章采用汉明码校验加偶校验的编码方式,实现高纠错编码[10]。

2.1 一级冗余编码

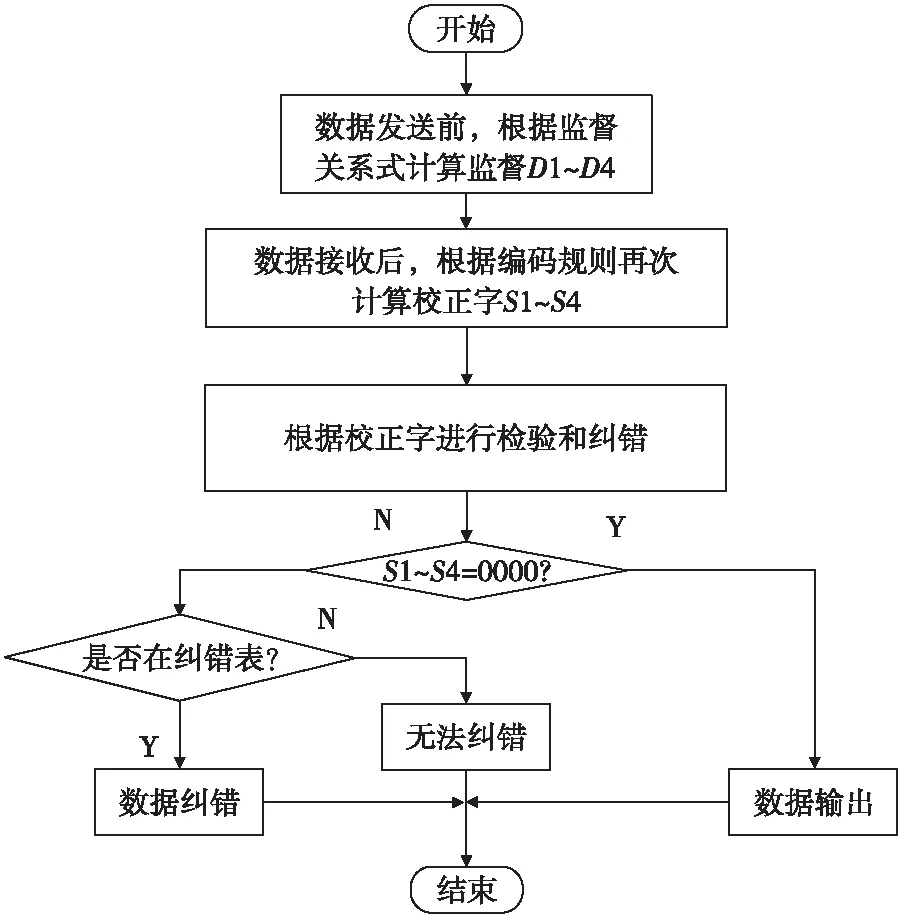

一级冗余编码采用一位纠错的汉明码,该码不仅算法简单,易于硬件电路实现,而且编码效率极高,在数据传输、存储领域应用广泛[11],汉明码校验流程图如图4所示。

图4 明码编码流程图Fig.4 Flow chart of clear code coding

数据传输过程中按字节发送,所以线性分组码中(n,k)中的码长n为8,为了保证监督位可以指示一位错码的所有可能,监督位r必须大于等于3[12],采集到的有效数据都是按字节存储传输,故信息位k取4,则监督位也为4。数据传输时,每字节的有效数据都分成高4 bit、低4 bit,然后依次放入分组码(8,4)编码模块进行编码,根据分组码构造关系,设计冗余位与监督关系,如表2所示。

表2 冗余位与监督关系构造表

根据表2可知,监督关系式为:

S1=D4⊕D6⊕D7⊕D8

(1)

S2=D3⊕D5⊕D7⊕D8

(2)

S3=D2⊕D5⊕D6⊕D8

(3)

S4=D1⊕D5⊕D6⊕D7

(4)

其中,D5、D6、D7、D8为数据位,D1、D2、D3、D4为校验位,令S1、S2、S3、S4为0,便可以得到下式:

D1=D5⊕D6⊕D7

(5)

D2=D5⊕D6⊕D8

(6)

D3=D5⊕D7⊕D8

(7)

D4=D6⊕D7⊕D8

(8)

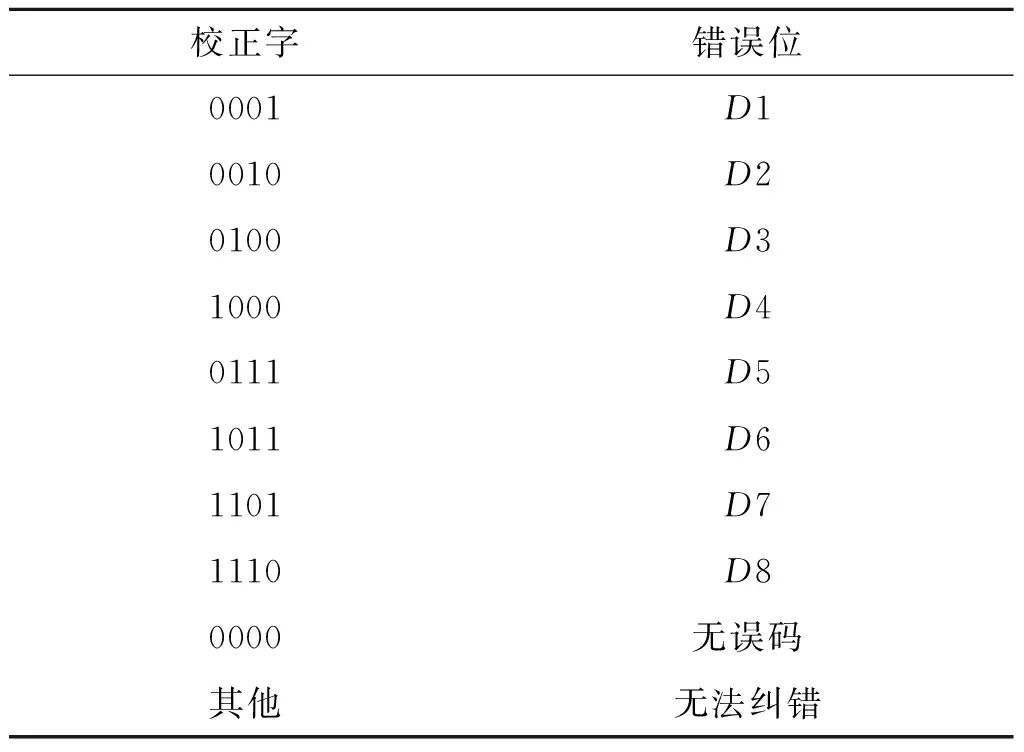

数据接收端接收数据后,根据监督关系式计算得到校正子S1、S2、S3、S4,若接收数据中仅存在一位错误数据,对照表3即可完成字内纠错[13]。为了提高效率,一位纠错时,仅对数据位纠错即可。若错误位数超过两位,则汉明码无法完成纠错,转入二级冗余码进行纠错。

表3 错码查询表

2.2 二级冗余编码

数据传输过程中的错误大都小于等于1位,一级编码就能解决纠错,针对少部分的多位出错,如果选择复杂的校验方式,不仅会进一步降低数据传输的有效带宽,而且会占用过多的FPGA资源,降低系统工作效率,故二级校验选用仅占一位校验位的奇偶校验。二级冗余编码表如表4所示。

传统的奇偶校验仅能判断奇数个错误,且不具备纠错功能[14],然而文章中,处于二级冗余编码的奇偶校验,由于已经确定了误码位置和误码个数,使得奇偶校验具备了纠错的能力。

表4 二级冗余编码表

根据表4可知,dj 为d1、d2、d3、d4的二级校验,其中D8J、D7J、D6J、D5J是d1、d2、d3、d4数据位的偶校验位,D8J作为D81、D82、D83、D84四位数据的校验位,可以通过异或求得,同理也可求得D7J、D6J、D5J。同时为了保证四位偶校验在传输过程中的准确性,对四位偶校验数据也同样进行字内的一级冗余编码。

D8j=D81⊕D82⊕D83⊕D84

(9)

D7j=D71⊕D72⊕D73⊕D74

(10)

D6j=D61⊕D62⊕D63⊕D64

(11)

D5j=D51⊕D52⊕D53⊕D54

(12)

解码时,首先进行字内汉明码纠错,如果错误位数超过两位时,就要启动字间的偶校验进行二级纠错,首先需要利用dj内的一级纠错码对二级冗余数据先行校验,以防由于检验码错误引起的误纠现象发生。例如d1的数据位错误超过两位时,可通过下式进行纠错:

D81=D8j⊕D82⊕D83⊕D84

(13)

D71=D7j⊕D72⊕D73⊕D74

(14)

D61=D6j⊕D62⊕D63⊕D64

(15)

D51=D5j⊕D52⊕D53⊕D54

(16)

通过式(9)—式(12),便可完全恢复出d1的数据位,即实现对d1的四位错误数据的纠错,同理也可对d2、d3、d4的多位纠错。

当两组内多位出错时,如d1中的D81、D82出错,而d2中的D62、D52出错时,也可通过偶校验对d1、d2两组数据进行纠错。

两级冗余编码完成后,由于LVDS编译码器可对10位并行数据完成串并转化,为了有效利用硬件资源,同时应对传输过程中的码间干扰,对发送数据流再进行直流平衡的8 bit/10 bit编码。

3 可靠性验证

为了验证两级冗余编码能否提高数据传输系统的可靠性,可以先搭建试验平台,同时模拟测试环境,进行试验验证。测试平台由地面测试设备、电缆网、采编器三部分组成。电缆网主要由240 m的屏蔽双绞线构成,实现采编器数据的高速回传。

实验中,将采编器和电缆置于高低温箱中,设置高低温循环来模拟温度环境,用函数发生器驱动场源发生器,产生空间磁场,模拟电磁环境。数据回传到地面测试设备后,利用上位机嵌入的数据处理软件,对回传数据进行解包处理,分析传输过程中是否出现误码、丢数的现象。上位机接收的数据如图5所示,其中“EB 90”为数据帧尾,“00 0F 9F EA~00 0F 9F F9”是帧计数,数据是F9~00的自减数。

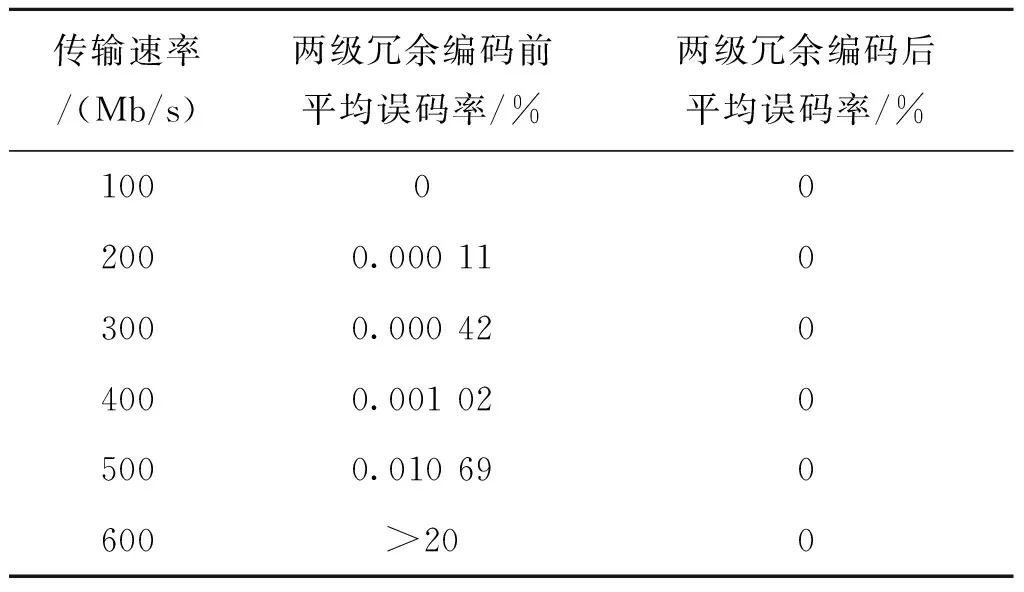

对照表5中的传输速率修改FPGA程序,依次测试每种传输速率的平均误码率,每个速率都进行60 次测试,每次测试传输的数据量约为32 GB,测试结果见表5。

图5 上位机接收原始数据Fig.5 Upper computer receiving original data

表5 两级冗余编码测试结果表

根据表5可得,未进行冗余编码时,仅凭硬件补偿电路,可以使LVDS信号在240 m双绞线中以100 Mb/s的速率无误码传输,随着传输速率的增大,误码率会迅速增大。然而进行两级冗余编码后,可以明显看出传输速率不断增加时,平均误码率仍然为0。

通过对比两级冗余编码前后的试验结果,可以发现在传输速率低于100 Mb/s时,编码前后的平均误码率均为0,即冗余编码不仅没有提高数据传输的可靠性,还占用了部分有效带宽。当传输速率位于100~600 Mb/s之间时,两级冗余编码明显地降低了数据传输的误码率,提高了传输系统的可靠性。

根据表5的测试结果可知,应该根据传输速率和传输距离合理选用编码方式。针对文章中恶劣环境中的远距离高速的传输条件,选用冗余编码实现了240 m屏蔽双绞线上的600 Mb/s的无误码传输。

4 结论

本文提出了基于FPGA的两级冗余编码系统,该系统通过硬件优化和软件优化相结合的方式,来提高数据传输过程中的稳定性。在硬件电路中,通过添加驱动器和均衡器,增强信号的传输能力;在软件逻辑方面,通过两级嵌套编码,字内编码实现字内的一位纠错,字间编码实现字内的多位纠错,字内纠错和字间纠错相结合的编码方式,来实现对数据传输过程的纠错。环境试验结果表明,在240 m的双绞线上,两级冗余编码的传输系统可以以600 Mb/s的速率正确传输。该系统已成功应用于远距离传输设备上。