基于逻辑器件响应特性的自治布尔网络调控*

刘海芳 张建国 龚利爽 王云才

1) (太原理工大学, 新型传感器与智能控制教育部重点实验室, 太原 030024)

2) (太原理工大学物理与光电工程学院, 太原 030024)

3) (广东省信息光子技术重点实验室, 广州 510006)

4) (广东工业大学信息工程学院, 广州 510006)

自治布尔网络已成功应用于随机数产生、基因调控、储备池计算等领域.为了在应用中合理选择器件使输出更好地满足各应用的需求, 本文研究了自治布尔网络中的逻辑器件响应特性变化时, 自治布尔网络输出状态随之变化的规律, 结果显示逻辑器件响应特性变化可以调控自治布尔网络输出在周期和混沌之间转变,且能改变自治布尔网络输出序列的复杂程度.进一步观察了逻辑器件响应特性和链路延时二维参数空间中输出序列复杂程度的分布, 结果显示快的逻辑门响应特性可以增强高复杂序列在链路延时参数空间的分布范围.同时研究了自治布尔网络中任意逻辑器件的响应特性单独变化对网络输出状态的影响, 结果显示不同节点的器件响应特性对序列复杂程度的调控能力有差异.研究表明, 逻辑器件响应特性可以调控网络输出序列复杂程度, 快的响应特性有利于高复杂混沌的稳定产生.

1 引 言

布尔网络是由二元态变量通过定向连接相互作用的系统, 其网络结构简单, 非常容易构造大型网络, 有利于模拟具有阈值行为和多反馈行为的复杂系统[1−4].布尔网络模型已成功应用于生命科学[2,5−7]、气候研究[3,8−9]、地震研究和预测[3]等众多领域.

经典的布尔网络各节点的更新机制是确定的,通常由一个外部时钟控制网络中各个节点同时更新状态, 这种更新机制为同步更新, 或者由一个选择设备指定各节点的更新顺序, 使各节点按照一定的更新顺序更新状态, 这种更新机制为异步更新.在这种确定性的更新机制的布尔网络中, 网络状态是离散的有限的.自治布尔网络是没有设备控制各节点的更新时间和更新顺序, 各节点的更新由节点本身的特性所定, 与确定的更新机制中网络的节点在指定的时间点发生突变不同, 自治更新的网络中节点的状态是连续变化的, 网络输出更加复杂.2009 年,Zhang 等[10]在实验室实现了硬件系统自治布尔网络, 并在实验中观察到改变电压可以改变网络输出状态为有序状态和混沌状态, 其混沌带宽可达吉赫(GHz)(—10 dB), 与现有电学混沌相比具有较大优势, 并推测其原因为逻辑器件的供电电压不同时使得器件引起的各种特征时间发生变化引起的, 如传输延时和器件上升沿下降沿时间.该自治布尔网络硬件系统是仅由逻辑器件经导线相互连接构成的数字电路, 具有电路结构简单、功耗低、易于集成的优点.自治布尔网络硬件系统的实现为在实验室进行多种基于自治布尔模型的系统模拟实验提供了非常有利的条件.目前, 自治布尔网络硬件系统提出以来已在随机数产生[11−15]、储备池计算[16−17]、基因调控[18−19]、不可克隆函数[20]等许多领域获得了成功应用.

自治布尔网络的输出可以在周期和混沌之间转换, 目前, 已有研究学者对自治布尔网络输出不同状态的影响因素进行了分析研究.2010 年Caval−cante 等[21]分析了简单自治布尔网络中输出为混沌的原因, 研究表明网络节点间链路延时的不一致性、器件的滤波效应和延时对输入和历史状态的依赖性均对网络输出混沌状态有影响.2014 年Rosin等[22]通过实验和仿真研究了节点间链路延时参数对耦合自治布尔网络同步的影响, 研究表明在单向耦合网络和双向耦合网络中该延时参数均可以调节耦合强度从而改变网络输出及其同步效果.2014 年Rosin 等[23]进一步研究了超过100 个节点的大网络中, 不同节点间由随机初始状态到达同步状态之前的暂态传输过程存在非常复杂的动态行为, 该暂态传输的平均时间随着网络节点数量增长呈指数增长.2016 年D'Huys 等[24]研究了自治布尔网络的链路延时对网络的影响, 表明链路延时越大网络输出到达稳态之前的暂态传输状态时间越长.2019 年Gong 等[25]分析了电路中噪声对自治布尔网络输出的影响, 证明噪声使网络输出状态不可预测.综上所述, 目前的研究多基于对具有稳定状态的自治布尔网络, 研究节点数量、链路延时对网络到达稳态之前的瞬态传输的时序的影响.对于可以产生混沌的自治布尔网络只是初步探索了产生混沌的影响因素, 并没有详细研究各因素变化对网络输出的影响.

本文研究了自治布尔网络中器件响应特性的变化对网络输出的影响, 逻辑器件是构成自治布尔网络的核心器件, 实际中有多种类型的逻辑器件,其响应特性各不相同, 本文的研究对自治布尔网络在不同应用领域中器件的选择具有重要意义.首先通过单变量布尔模型分析数学模型中参数对器件响应特性的表征性能.然后以小型自治布尔网络为研究对象, 仿真研究器件响应特性变化对自治布尔网络输出状态的调控效果, 观察了器件响应特性和链路延时时间二维参数空间上自治布尔网络输出状态的分布情况, 分析了两个参数之间的相互影响.进一步观察和分析了变量间器件响应特性的不一致性对自治布尔网络输出状态的影响.

2 数学模型

2.1 单节点异或非逻辑门模型

图1 为异或非逻辑门示意图, u1, u2为输入信号, yout为输出信号.实际逻辑器件中, 异或非逻辑门无法对输入信号做瞬时响应, 当输入信号u1, u2维持时间较短时, 异或非逻辑门将不能完全响应,yout不能产生对应的输出波形, 本文称这一特性为逻辑器件响应特性, 在本文的研究中, 对任一给定的信号维持时间为∆tu的输入信号, 输出信号脉冲幅值和脉冲宽度的不同表征了器件响应特性的不同, 输出信号幅值越大、脉冲宽度越宽表明器件响应越快, 能响应更窄的输入信号.

图1 异或非逻辑门示意图Fig.1.The schematic illustration of the XNOR logic gate.

图1 中异或非逻辑门的数学模型如(1)式—(3)式所示, 式中微分项dx/dt 能够模拟器件响应过程, 由于微分项的存在, 使输出不可能发生突变,能够模拟实际器件中器件不能对输入信号做瞬时响应的特性.因此微分项是模拟器件响应特性的核心, τlp为器件响应特性参数, 改变τlp可以改变模型中微分过程的时间长短, 从而调节逻辑器件响应特性.u1(t), u2(t)为输入信号, yout(t)为输出信号,“⊙”表示异或非运算, U1(t), U2(t)为量化的输入信号, Yout(t)为量化的输出信号, uth= yth= 0.5 V为阈值电压, τlp为一阶微分项的常系数, 改变τlp可以调节异或非逻辑门的响应特性.

图2 所示为异或非门对不同输入的输出响应图, 该实验中τlp= 0.125 ns, u2保持低电平0 V,u1初始为高电平1 V 然后转变为低电平0 V 保持一段时间后转变为高电平, 阈值电压为0.5 V, 大于阈值电压为高电平否则为低电平, 图2(a)中tpd为器件输入输出延时, 可以看出当输入信号维持时间小于tpd时, 输出信号来不及穿越阈值输出正确的响应电平(本实验中为高电平), 反之当输入信号维持时间大于tpd时, 逻辑门将收到响应.图2(a)—(c)中u1低电平保持时间分别为1.5, 0.2 ns, 0.1 ns,异或非逻辑门对低电平的响应输出yout应为高电平, 对比图2(a), (b), (c)可以看出, 图2(a)中低电平保持的时间足够长, yout能够完全响应输出为完整的高电平; 图2(b)中低电平保持的时间减短, 器件不能完全响应yout高电平幅值较低时间较短;图2(c)中低电平保持的时间过短, 器件不能响应yout幅值低于阈值0.5 V 不能产生正确的响应, 此时由于输入脉冲太窄, 器件响应特性慢, 不能响应如此快的脉冲, 产生了短脉冲抑制效应.

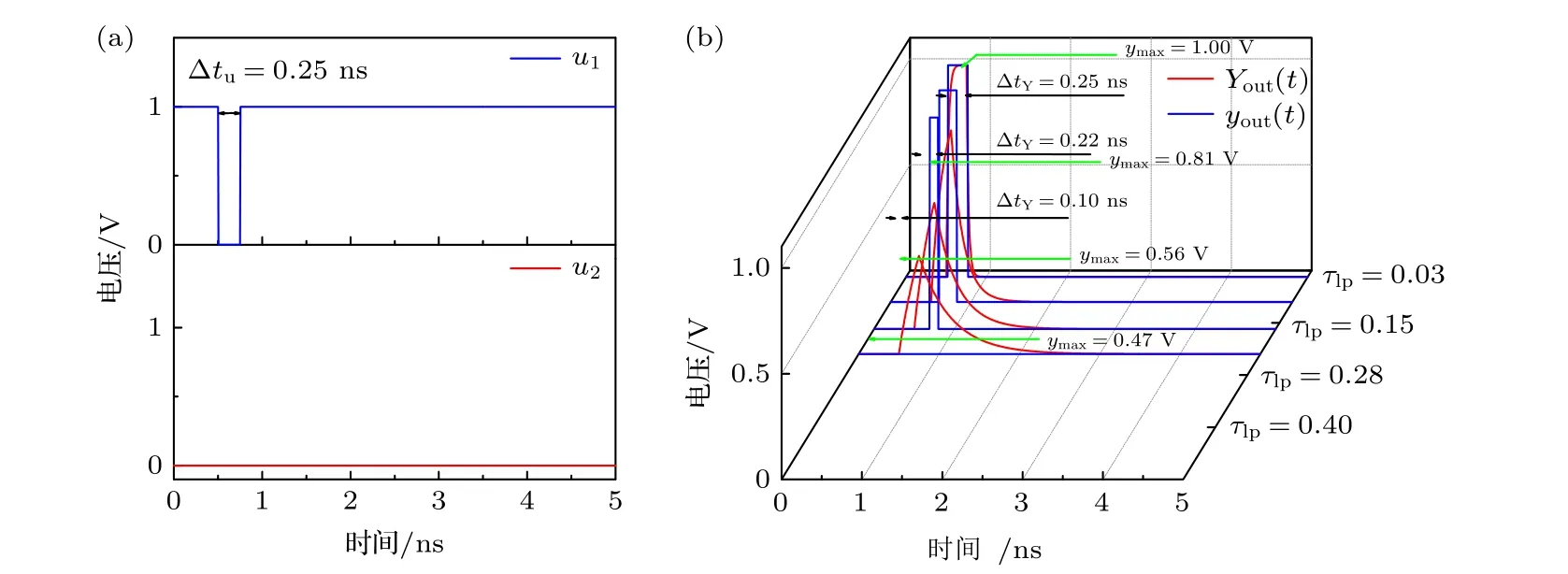

(1)式—(3)式中τlp是器件输入输出延时tpd的常数倍, τlp= tpd/ln(2), tpd表示器件从接收到输入信号的变化开始响应到穿越阈值电压的时间[26].实际器件中tpd受制造工艺、环境温度、工作电压的影响, 不同器件之间差异较大, 相同器件之间也不能完全相同.如图3 所示, 图3(a)为输入信号,u2(t)为恒定低电平0 V, u1(t)初始为高电平1 V,在0.50—0.75 ns 处有一脉冲宽度∆tu= 0.25 ns 的低电平脉冲, yout(t)初始为低电平, 根据逻辑运算,当u2(t)低电平脉冲出现时yout(t)应响应为高电平脉冲, 图3(b)中红色曲线为器件输出信号yout(t),曲线峰值为输出脉冲幅值ymax, 蓝色曲线为输出信号yout(t)经过(2)式量化后的信号Yout(t), 如图所示, 蓝色曲线为矩形脉冲, 其脉冲宽度即为输出信号脉冲宽度∆tY.对比图中不同τlp取值的输出信号可以看出, 随着τlp增大, yout(t)的幅值ymax减小,脉冲宽度∆tY减小, 表明τlp增大器件响应速度变慢, 对于相同的输入信号, 其输出幅值减小脉冲宽度变窄, τlp为0.4 ns 时脉冲宽度减小为0 ns.此时器件响应速度太慢, 不能响应维持时间为0.25 ns的输入信号.

图2 异或非逻辑门输入输出响应波形图 (a) 完全响应波形图; (b) 不完全响应波形图; (c) 非正确响应波形图Fig.2.I/O response waveform of XNOR logic gate: (a) Full response waveform; (b) incomplete response waveform; (c) incorrect re−sponse waveform.

图3 异或非逻辑门输入相同, τlp = 0.03, 0.15, 0.28, 0.40 时输出波形 (a)输入波形; (b)输出波形Fig.3.Output waveforms of XNOR logic gate for τlp = 0.03, 0.15, 0.28, 0.40 when inputs are the same: (a) Input waveform; (b) out−put waveform.

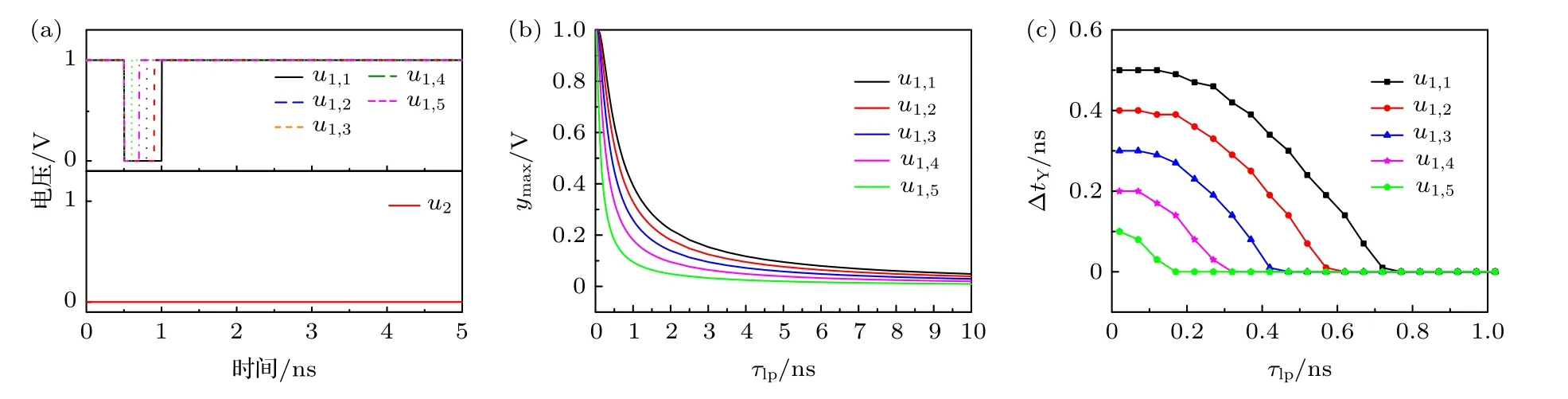

图4 异或非逻辑门输出脉冲幅值和宽度随τlp 变化曲线 (a) 输入波形图; (b) 输出脉冲幅值ymax 随τlp 变化曲线; (c) 输出脉冲宽度∆tY 随τlp 变化曲线Fig.4.Output pulse amplitude and width as a function of τlp : (a) Input waveform; (b) output pulse amplitude as a function of τlp;(c) output pulse width as a function of τlp.

为了更详细直观地观察输出波形随器件响应特性的变化规律, 选取5 个输入信号, 如图4(a)所示, u2完全相同均为低电平0 V, u1,j表示u1的j种不同波形, 其低电平0 V 保持时间分别为0.1, 0.2,0.3, 0.4, 0.5 ns.观察τlp从0.01 ns 增大至5.00 ns时输出脉冲的幅值ymax和宽度∆tY的变化, τlp调节步进为0.05 ns.如图4(b)所示为ymax随τlp的变化曲线, 曲线有明显凹点, 凹点之前ymax随着τlp的变大迅速减小, 且减小的速度越来越快, 凹点之后减小的速度降低曲线趋于平缓.图4(c)为∆tY随着τlp的变化曲线, 可以看出, 对于同一个输入信号随着参数τlp的增大响应脉冲宽度∆tY逐渐减小,最终降为0 ns, 表明此时逻辑器件不能输出正确的响应(此例中为高电平).仿真结果表明模型参数τlp能够对逻辑器件的响应特性进行连续调节, 因此本文中将参数τlp称为器件响应特性参数, 下文中通过调节τlp研究逻辑器件响应特性对自治布尔网络输出的影响.

2.2 自治布尔网络模型

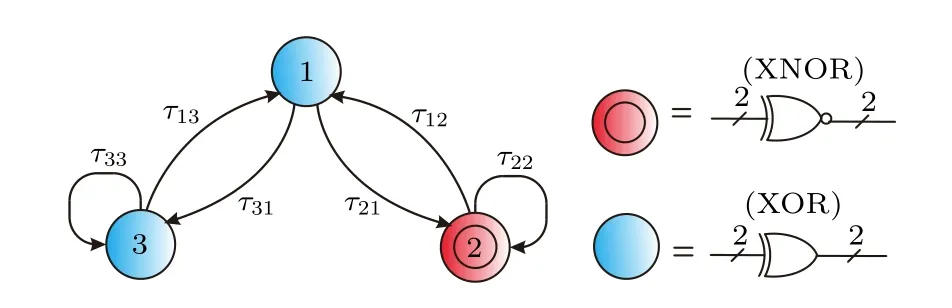

选取文献[10]中提出的三节点小型自治布尔网络作为研究对象, 如图5 所示.节点2 为异或非逻辑门, 节点1, 3 为异或逻辑门, 连接线箭头方向为信号传输方向, τij表示节点j 到i 的链路延时.

图5 自治布尔网络示意图Fig.5.Schematic illustration of autonomous Boolean net−work.

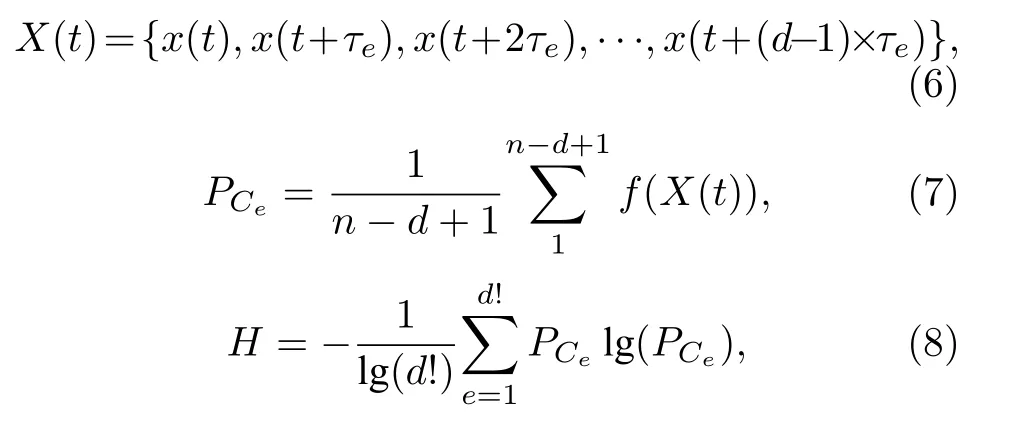

自治布尔网络的数学模型如 (4) 式和(5) 式所示, 对比模型(1) 式和(2)式可见, 三节点模型为3 个模型(1)式中单节点模型相互连接, 网络中节点1, 2, 3 的器件模型中仍然用微分项dx1/dt,dx2/dt, dx3/dt 模拟器件响应输入信号的时间过程,模型(1) 式和(2)式不同的地方是模型(2)式中各器件的输入信号来自其他器件或者件自身的输出信号, 而模型(1)式中输入信号为外部指定的.因此多节点模型中微分项系数τlp,i能够调节器件响应特性, τlp,i减小器件响应速度更快, 使器件能够响应维持时间更短的输入信号.(4)式中“ ⊕ ”表示节点1, 3 的逻辑器件执行异或运算, “⊙”表示节点2 的逻辑器件执行异或非运算, τlp,1, τlp,2, τlp,3分别为图2 中节点1, 2, 3 的器件响应特性参数,x1(t), x2(t), x3(t)分别为图2 中节点1, 2, 3 的输出信号, 逻辑器件自身会对输入信号进行高低电平的判断, 根据判断结果为高(1)或者低(0)做出响应,因此用(5)式对x1(t), x2(t), x3(t)量化后的X1(t),X2(t), X3(t)表示节点1, 2, 3 的输入信号, xth= 0.5 V为阈值电压, Xi(t)为xi(t)经过量化的值, τij为表示节点j 到节点i 的链路延时, 如图2 所示节点之间连接线的箭头方向为信号传输方向.

3 实验结果与分析

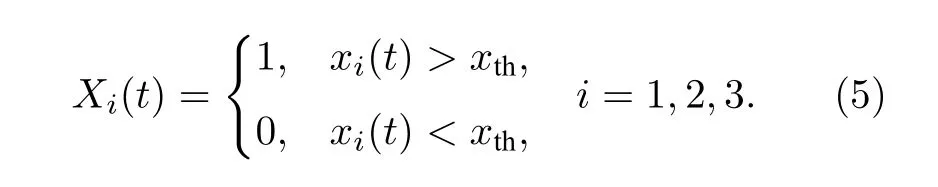

本文以节点1 的输出作为自治布尔网络的输出, 图6 所示为器件响应特性参数τlp变化下的分岔图.在实验中各链路延时取值为τ12= 0.20 ns,τ13= 0.07 ns, τ31= 0.19 ns, τ21= 2.02 ns, τ22=0.97 ns, τ33= 0.21 ns, τlp变化范围为0.01 ns 至3.00 ns, 调节步进为0.001 ns, 纵坐标∆tLDP为输出时序的相邻两个上升沿之间的时间距离, 图6 中可以看出, 随着参数τlp(τlp= τlp,1= τlp,2= τlp,3)的减小, ∆tLDP序列由周期进入混沌, 随着参数τlp继续减小, 混沌周期窗口交替出现, 在τlp越小的区域周期窗口出现频率越小.

图7 为τlp= 0.630 ns, 0.305 ns 和0.050 ns 时网络输出时序、频谱、∆tLDP序列相图.图7(a1),(b1)和(c1)表明 τlp= 0.63 ns 时的输出为周期时序, 对应的频谱中有尖峰, 此时∆tLDP序列相图可以看出, 存在两个相近的∆tLDP, 分别为0.89 和0.92 ns, 表明一个周期内有2 次上升沿和下降沿;图7(a2), (b2), (c2)表明τlp= 0.305 ns 时输出时序比图7(a1)复杂程度更高, 但仍有周期; 图7(a3),(b3), (c3)表明τlp= 0.05 ns 时输出为频谱平坦的混沌.

图6 自治布尔网络分岔图Fig.6.Bifurcation diagram of the autonomous Boolean net−work.

图7 自治布尔网络在τlp = 0.630, 0.305, 0.050 ns 的模拟结果 (a1)−(a3) 时序; (b1)−(b3) 频谱; (c1)−(c3) ∆tLDP 序列相图Fig.7.Simulation results of the autonomous Boolean network for τlp = 0.630, 0.305, 0.050 ns: (a1)−(a3) Time−evolution; (b1)−(b3) power spectra; (c1)−(c3) phase diagrams of ∆tLDP series.

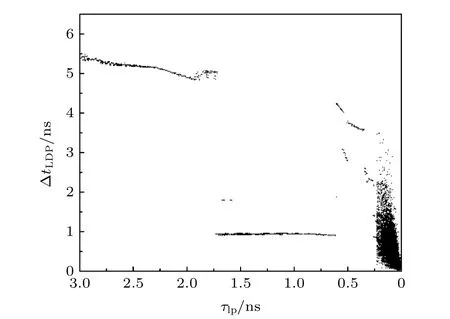

节点之间的链路延时τij是自治布尔网络的另一个重要参数, 不失一般性地, 假设τij和τlp两个参数在调节过程中会相互影响, 为了研究响应特性参数τlp,i和链路延时参数τij之间的相互作用, 本文对自治布尔网络输出的复杂程度在参数τlp,i和τij二维空间上的分布情况进行了研究.排序熵是常用的混沌表征方法, 可以衡量序列的复杂程度,具有计算简单快速的优点[27,28].固本文中应用排序熵H 表征输出序列的复杂程度, 排序熵计算如下:

式中, d 为嵌入维数, τe为延迟时间, 本文中分别设为5 和1, n 为序列x (t)长度, X (t)为x (t)的重构序列, 其中 t ≤n −(d −1)×τe, 序列长度n 需要满足n ≫ d !的条件.任意时刻的X(t)为一个d 维向量, 若有 X [t+(d −i)×τe]=X[t+(d −j)×τe] , 且i < j则称 X [t+(d −i)×τe]≤X[t+(d −j)×τe] , 向量中所有值按大小顺序不同共有d !种排列方式.Ce表示不同的排列方式, e = {1, 2, ···, d !}, (6) 式为排列方式Ce的概率分布, 当任意时刻的d 维向量X (t)的 排 列 方 式 为Ce时f (X(t)) = 1, 否 则f (X(t)) = 0, PCe为X(t)排列方式为Ce的概率.由 (7)式和 (8)式计算可得, 排序熵H 范围为[0, 1],当X(t)为任意排列方式, Ce的概率均相同, 为1/d !, 排序熵H 最大为1, 此时d !排列方式在序列中是等概率出现的, 序列分布随机性好, 排序熵值越高表明序列复杂程度越高.

图8 排序熵值在二维参数空间τlp 和τij 上的分布图 (a) τij = τ12; (b) τij = τ13; (c) τij = τ22; (d) τij = τ21; (e) τij = τ31; (f) τij = τ33Fig.8.Two dimensional maps of H in the parameter space of τlp and τij: (a) τij = τ12; (b) τij = τ13; (c) τij = τ22; (d) τij = τ21; (e) τij =τ31; (f) τij = τ33.

图8 所示为自治布尔网络输出的排序熵在参数τlp(τlp= τlp,1= τlp,2= τlp,3)和τij二维空间上的分布, 图中颜色表示不同的排序熵值, 红色区域的排序熵值较高, 观察可见红色区域主要分布在图中右下三角区域, 表明τij越大τlp越小时布尔网络输出排序熵值越高序列复杂程度越高, 此外, 图中有零散的小面积红色区域分布, 猜测其分布规律可能与τij的取值有关.本文定义序列排序熵值H >0.95 为高复杂序列, 图中黑色曲线为H = 0.95 的等值线, 随着τlp减小, τij轴方向H > 0.95 等值线内区域范围逐渐变宽, 表明τlp减小可以增大τij参数空间中高复杂序列的分布范围, 有利于高复杂混沌的稳定产生.观察比较图中相同列的两幅排序熵分布, 图8(a),(d)、图8(b),(e)具有相似的分布, 表明节点i, j 相互传输的两个延时τij和τji具有一致的调控效果.

进一步研究了自治布尔网络中不同节点处逻辑器件响应特性单独变化对输出的影响.图9(a)—(c)分别为固定τlp,1, τlp,2, τlp,3时, 输出排序熵值在(τlp,1, τlp,2), (τlp,1, τlp,3), (τlp,2, τlp,3)的二维参数空间中的分布图.通过比较第1 行、第2 行、第3 行可以发现, 第1 行图中高排序熵区域较大, 表明任意单个节点τlp,i减小都有利于高排序熵序列的产生.图9(b1)的红色区域显著高于其他分布图,可以表明τlp,2的减小对网络输出的高排序熵空间增强效果最大, 可有效促进高排序熵序列的产生.

4 讨 论

假设自治布尔网络中的节点能够响应任意快的信号, 则输出呈现为越来越快的复杂波形[29].但是实际构成自治布尔网络的逻辑器件不能响应任意快的输入, 因此网络以初始值y01开始演化, 随着时间推移输出序列频率越来越高, 频率高到一定程度时, 由于器件响应特性不能匹配如此快的信号, 会终止输出继续复杂化高频化, 标记此时的序列为y1.之后自治布尔网络会进入新一轮的不断高频化复杂化的过程, 直到被再一次终止, 记新的序列为y2.y2的初始值为y1终止时的部分序列记为y02, 显然y02≠ y01, y2≠ y1.如此输出轨迹不断地被终止, 然后以终止时的序列为初始值重新开始演化, yN≠ yN+1, N 不断增大, 由此形成混沌吸引子.器件响应特性不同, 则轨迹被终止的时间位置不同.器件响应特性快, 则被终止时yN演化达到的复杂程度和频率更高, 有利于增强输出序列的复杂程度和混沌的产生.

图9 排序 熵值在二维参数空间(τlp,i, τlp,j)上的 分布 图 (a1)−(a3) τlp,1 = 0.1, 0.3, 0.5 ns 且(τlp,i, τlp,j) = (τlp,2, τlp,3); (b1)−(b3) τlp,2 = 0.1, 0.3, 0.5 ns 且(τlp,i, τlp,j) = (τlp,1, τlp,3); (c1)−(c3) τlp,3 = 0.1, 0.3, 0.5 ns 且(τlp,i, τlp, j) = (τlp,1, τlp,2)Fig.9.Two dimensional maps of H in the parameter space of (τlp,i, τlp,j): (a1)−(a3) τlp,1 = 0.1, 0.3, 0.5 ns and (τlp,i, τlp,j) =(τlp,2, τlp,3); (b1)−(b3) τlp,2 = 0.1, 0.3, 0.5 ns and (τlp,i, τlp,j) = (τlp,1, τlp,3); (c1)−(c3) τlp,3 = 0.1, 0.3, 0.5 ns and (τlp,i, τlp,j) =(τlp,1, τlp,2).

5 结 论

通过单节点模型, 验证了所用模型的参数τlp能够连续调节节点器件响应特性.利用该模型仿真研究了器件响应特性对自治布尔网络输出的影响.分岔图及时序频谱相图分析表明, 减小τlp即增快器件响应特性, 可以使网络输出进入混沌; 利用排序熵H 表征输出序列复杂程度, H 在(τlp, τij)二维空间上的分布图表明, 快的器件响应特性可以增强高排序熵空间; H 在(τlp,i, τlp,j)二维空间上的分布图表明, 由于网络拓扑结构的影响, 不同节点的器件响应特性对网络输出调控能力不一致, 本文所选3 节点小型自治布尔网络中, 节点1, 3 器件响应特性变化对网络输出影响不大, 节点2 的器件响应特性变化对网络输出具有显著影响.

本文研究成果对自治布尔网络各应用领域器件的选择具有重要意义, 根据不同的应用需求选择不同响应特性的器件, 如在随机数的应用中, 随机数是信息加密过程中的关键组成部分, 随机数的产生速率和不可预测性是信息加密安全性的重要保障, 应用本文的研究结论, 选择器件响应特性快的器件可以提高序列复杂程度, 增强高复杂序列空间, 促进高复杂混沌序列的稳定产生, 进而提高随机数产生速率和不可预测性.