28 nm工艺触发器抗单粒子翻转版图加固技术

苑靖爽,赵元富,王 亮,李同德,孙 雨,朱永钦

(1. 北京微电子技术研究所,北京 100076;2. 中国航天电子技术研究院;3. 中国航天科技集团有限公司 抗辐射集成电路技术试验室: 北京 100094)

随着我国航天事业的发展,更小的特征尺寸成为提升宇航用集成电路性能的必由之路,但也为抗辐射加固设计带来了挑战。随着CMOS工艺进入纳米尺寸,晶体管的尺寸越来越小,器件间的排列更加紧密,电路中敏感节点对之间的物理距离也变得越来越短。在太空中,如器件受到宇宙射线或离子轰击,器件间的电荷共享效应会更加显著[1-2, 16-18]。由于器件存储单元间的间距越来越小,单个高能离子可能会入射到多个敏感区域,2个或2个以上敏感节点同时收集电荷,导致电路发生单粒子翻转(single event upset, SEU)的概率大幅增加[3-4],传统的抗SEU加固方法的针对性和有效性无法保证[5-8]。因此,需寻求新的加固方案,应对越来越显著的SEU问题。

为实现电路抗SEU能力,对电路版图进行了重新布局,实现了版图加固设计。版图加固的设计方法主要基于2个原理:(1)敏感节点对分离原理:在敏感节点对中插入电路中的非敏感节点,尽量在不牺牲面积的前提下增加敏感节点对之间的距离[9];(2)电荷补偿原理:将属于同一敏感节点的NMOS管和PMOS管的漏区邻近放置,当离子同时入射到NMOS和PMOS器件,NMOS漏区和PMOS漏区产生互补的瞬态电流变化趋势,电荷相互抵消,可缓解敏感节点处的单粒子瞬态脉冲电流峰值,减小敏感节点的单粒子敏感性。本文使用不同版图加固方法设计触发器链并进行试验,定性和定量分析了28 nm 工艺下不同版图加固方法对电路抗SEU性能的影响,并与非加固电路进行了对比分析。研究28 nm 工艺下的抗SEU版图结构,对宇航用28 nm体硅电路的抗辐射加固设计具有一定的参考价值。

1 试验电路简介

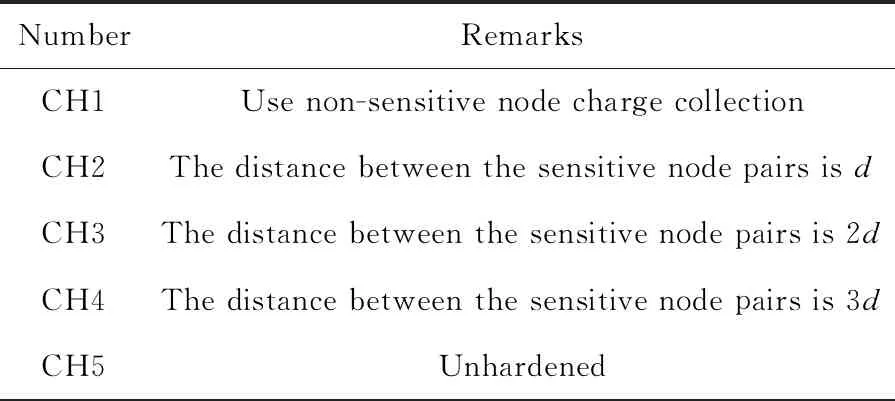

设计了5条低频触发器链(CH1,CH2,CH3,CH4,CH5),用于测试版图加固设计的效果。为提高电路的抗SEU能力提供支撑,5条触发器链均采用双互锁存储单元(dual interlocked storage cell, DICE)结构。其中4条触发器链采用不同的版图加固技术对电路进行加固,另1条触发器链为非加固对比链。试验电路中的触发器清单如表1所列。其中,d为标准单位距离,μm。

表1 试验电路中触发器清单Tab.1 Flip-flops of the test circuit

1) CH1链

CH1链通过电荷补偿原理对电路进行加固。通过电荷补偿原理,对版图进行重新布局,达到对电路进行SEU加固的目的。并与其他链进行对比,验证加固方法的有效性。

2) CH2,CH3,CH4链

这3条链通过隔离敏感节点来对测试电路进行加固,CH2,CH3,CH4链敏感节点对之间的距离分别为d, 2d,3d。通过这3条链,测试28 nm电路中不同敏感节点对的距离对SEU加固性能的影响。

3) CH5链

CH5链未进行加固,用于与加固后的结果进行对比,是对照链。

2 试验过程及方法

2.1 测试系统

试验电路单粒子效应测试系统由试验电路板、继电器控制模块、路由器、程控电源和2台PC机(PC1和PC2)组成。被测器件置于试验电路板上,试验室内的PC1控制程控电源和继电器控制模块,利用继电器控制模块,选择不同的电路板分别进行辐照,利用程控电源提供电路板电源和监控电流,试验室外的PC2作为远程计算机通过网线监控PC1。

图1为单粒子效应试验电路板原理图。输入的测试激励向量由电路板上的FPGA提供,试验过程中,测试电路和对比电路的输出信号会实时发给FPGA进行比较,比较完成后,FPGA会将统计的错误数发给上位机。

2.2 测试方法

试验电路共有5条触发器链,每条触发器链有4 000级。触发器链SEU试验流程如图2所示。离子总注量达到1.0×107cm-2时,停止辐照。

2.3 辐照源

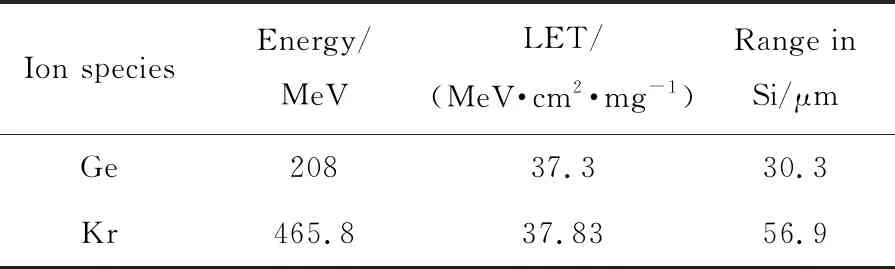

根据国内重离子辐照条件,选取了2种 LET 值的重离子进行SEU试验,重离子参数如表2所列。

表2 SEU试验重离子参数Tab.2 Pamameters of heavy ions for SEU test

3 试验结果及分析

3.1 试验现象及数据

使用Ge离子进行辐照时,频率为100 MHz;使用Kr离子进行辐照时,频率为10 MHz。当输入数据为00和FF时,除了未加固的触发器链,其他链都没有发生翻转;当输入数据为55时,5条测试链中均发生了SEU。因此,仅对比输入数据为55的SEU试验数据。

由图3可见,2种不同的离子入射后,4条加固后的触发器链都发生了翻转。由图3(a)可见,Ge离子入射后,非加固的触发器链的错误数为692,采用电荷补偿原理加固后的触发器链错误数大幅降低,仅有4;由于敏感节点对距离不同,采用敏感节点对分离原理加固后的错误数分别为13,10,7,表明采用敏感节点对分离原理的加固方法,也可有效降低SEU错误数。由图3(b)可见,Kr离子入射后,非加固的触发器链的错误数为689,采用电荷补偿原理加固后的触发器链错误数仅有2;采用敏感节点对分离原理加固后的错误数分别为8,7,4。

3.2 试验分析

通过试验结果对比可知,离子入射后,4条加固后的触发器链都发生了翻转,但翻转数最大只有13。2种加固结构下,触发器链的SEU数都下降了95%以上。因此,可认为4种加固方法都能较好地对电路进行单粒子加固。由4条加固后触发器链的翻转数比较可见,使用电荷补偿原理加固后,在相同入射条件下,发生的SEU数最少。因此,使用电荷补偿原理加固方法的抗SEU效应效果最为显著。电荷补偿原理如图4所示。

以反相器为例,对属于同一逻辑节点输出端的漏区节点n1,n2进行邻近布局。当入射离子同时影响关态PMOS漏区和开态NMOS漏区时,PMOS晶体管漏极节点处收集的正电荷会提高电路的输出电压。如输出最初为“0”且收集了足够的电荷,那输出的逻辑值可能会发生变化。而一旦注入的多余电荷被清除或重新结合, NMOS晶体管就会恢复至“0”。同样,撞击在NMOS晶体管漏极接触节点上的离子会降低节点电压,使其低于接地电压,增强输出状态。二者相互作用,由PMOS晶体管收集的正电荷被NMOS晶体管收集的负电荷抵消,导致PMOS漏区上较大的“0”到“1”的正向瞬态脉冲会被NMOS漏区上较小的负向瞬态脉冲抵消一部分,反映到2个漏区相连的逻辑节点上的“0”到“1”的正向电压脉冲变小了,如图4 所示。这种方法可有效减小节点的单粒子敏感性,提高单元SEU的LET阈值[9]。

利用电荷补偿原理进行版图加固主要应用在DICE结构上。利用电荷补偿原理进行版图加固的触发器不依靠传统的节点分离来降低发生SEU的概率[10-11],而是通过分析布局中每个漏极接触节点对单个离子的电路响应,将每个漏极接触节点放置在布局中,使多个漏极接触节点共同起作用,以全部或部分抵消单个离子对电路的整体影响[12]。

DICE是一种存储单元结构,它利用电路内部节点的双冗余设计实现软错误恢复能力[13-14]。图5为应用于DICE单元的电荷补偿原理版图布局。DICE存储单元不受单个节点SEU的影响,但易受多个电路节点SEU的影响,尤其是随着器件特征尺寸的减小,单个高能离子入射到多个电路节点的概率增加,导致DICE结构不能适用于小尺寸器件的电路加固[15]。基本的8管DICE存储元件结构如图5(a)所示。当DICE设计中“关断”晶体管的漏极接触节点被重离子击中时,连接到该漏极接触节点的电路节点可暂时切换其逻辑状态,但随着电路其余节点的影响,逻辑状态会恢复到初始状态。但若2个“关断”晶体管的漏极接触节点被同一离子击中,就可能导致存储单元发生翻转。因此,采用电荷补偿原理,对DICE结构的版图进行重新布局,对可同时“关断”的任意2个晶体管T1和T2,将另一个“导通”晶体管T3的漏极接触节点置于T1和T2的漏极接触节点之间,3个晶体管的漏极接触节点处于水平方向,其中,T3的漏极接触节点直接连接到T1或T2的漏极接触节点。当2个“截止”晶体管同时被高能离子撞击时,中间的“导通”晶体管的漏极接触节点也会被击中,收集的电荷会抵消在“截止”晶体管漏极处收集的电荷,降低总体在“导通”晶体管和“截止”晶体管之间的共享电路节点处收集的电荷,降低DICE单元发生SEU的概率。

以M1,M3和M4为例,当同一离子撞击到M1和M4时,会导致n1和n4节点发生翻转。对普通的DICE版图结构,若n1和n4节点同时发生翻转,就会导致DICE单元存储数据发生变化。使用图5(b)所示的电荷补偿原理对版图加固后,当同一离子撞击到M1和M4时,必定会导致该离子打到M3,在n3节点处产生的电荷会将n4节点处产生的电荷抵消,降低n4节点收集到的电荷,使n4节点不发生翻转,则仅有n1节点发生翻转,不会导致DICE单元存储状态发生改变。

若离子同时撞击到M1和M3,M1管的入射会导致n1节点存储状态发生翻转,n1翻转将使晶体管M4导通,并驱动节点n4发生翻转。相反,离子撞击到M3时,会降低节点n3的电压,属于同一节点的n3和n4共同作用,使DICE电路恢复时间减小。若离子同时撞击到M1和M4,M4管的入射会导致n4节点存储状态发生翻转,与此同时,离子撞击到M3时,会降低节点n3的电压,属于同一节点的n3和n4共同作用,使DICE电路恢复,不发生翻转。

电荷补偿原理将漏极接触节点放置在布局中,通过上述相对的SEU效果,来进行电路抗SEU加固设计。电荷补偿原理不依赖于敏感电路节点的距离大小,更适合纳米电路。

通过试验可见,不同敏感节点对距离的触发器链抗SEU的性能不同。其中,敏感节点对距离最大的触发器的抗SEU性能越好。但由于敏感节点对分离加大了电路之间的敏感节点对之间的距离,导致电路面积的开销很大。

对比使用电荷补偿原理加固和敏感节点对分离2种加固方式,前者不依赖于敏感节点对,后者则是敏感节点对距离越大,加固效果越好。然而随着器件特征尺寸的减小,电路中器件的间距越来越小,器件间的电荷共享效应对电路翻转的影响越来越大,使用敏感节点隔离的加固方式所造成的面积损失也越来越大。因此,采用电荷补偿原理进行加固更适合28 nm工艺器件或集成电路。

4 结论

本文针对28 nm体硅工艺集成电路的SEU问题,利用集成电路的版图的空间布局,设计了敏感节点对分离和基于电荷补偿原理的2种加固结构。在实现敏感节点对分离结构时,设计了3种不同的分离距离,分别为d, 2d,3d。电荷补偿原理设计时则依据具体工艺的特征。试验结果表明,基于电荷补偿原理结构的抗SEU加固能力最强;与其他敏感节点分离距离相比,分离距离为3d时,加固能力最强;以Ge离子入射为例,2种加固结构下的SEU数均下降了95%以上。需要注意的是,敏感节点对分离这一物理隔离方法对抗SEU加固有效,但随着工艺的进步,隔离的加固方法使电路的面积和性能损失较大,而采用电荷补偿原理等基于辐射效应机理、低开销的加固设计技术应是更小工艺尺寸加固技术开发的重要途径。