Chiplet关键技术与挑战

李乐琪 刘新阳 庞健

摘要:半导体产业正在进入后摩尔时代,Chiplet应运而生。介绍了Chiplet技术现状与接口标准,阐述了应用于Chiplet的先进封装种类:多芯片模块(MCM)封装、2.5D封装和3D封装,并从技术特征、应用场景等方面介绍了这些封装技术的进展。提出了未来发展Chiplet的重要性和迫切性,认为应注重生态建设,早日建立基于Chiplet的技术标准。

关键词:Chiplet;2.5D封装;3D封装;先进封装

Abstract: The semiconductor industry is entering the post-Moore era, and Chiplet emerges as the times require. The current status, inter? face standards of Chiplet technology, and the advanced packaging types applied to Chiplet are introduced, including multichip module(MCM), 2.5D package, and 3D package. The progress of these packaging technologies is discussed from their respective characteristics, ap? plication scenarios, etc. The importance and urgency of developing Chiplet in the future are put forward. It is believed that ecological con? struction should be paid attention to and technical standards based on Chiplet should be established as soon as possible.

Keywords: Chiplet; 2.5D package; 3D package; advanced package

近年来,半导体工艺水平的不断提升使芯片性能得到显著增强,但是摩尔定律正在逐渐逼近物理极限。同时,随着中央处理器(CPU)、图形处理器(GPU)、现场可编程门阵列(FPGA)等高性能运算(HPC)芯片性能的持续提升,人工智能(AI)、车联网、5G等应用相继兴起[1-4],各类应用场景对高带宽、高算力、低延时、低功耗的需求愈发强烈。为解决这一问题,“后摩尔时代”下的异构集成芯片技术——Chiplet应运而生。2015年Marvell创始人周秀文博士在2015年国际固态电路会议(ISSCC)上提出模块化芯片概念。这是Chiplet最早的雛形。Chiplet将芯片性能与芯片工艺解耦,同时2.5D、3D等封装技术如雨后春笋般出现。2.5D、3D封装技术提供更高的互连密度,可以集成更多芯片模块,有助于提升芯片效能,降低系统功耗。这也是HPC芯片开发人员采用2.5D、3D封装技术的原因。

1 Chiplet技术现状与挑战

Chiplet技术是一种利用先进封装方法将不同工艺/功能的芯片进行异质集成的技术。这种技术设计的核心思想是先分后合,即先将单芯片中的功能块拆分出来,再通过先进封装模块将其集成为大的单芯片。“分”可解决怎么把大规模芯片拆分好的问题,其中架构设计是分的关键(需要考虑访问频率、缓存一致性等);“合”是指将功能比较重要的部分合成在一颗芯片上,其中先进封装是合的关键(需要考虑功耗、散热、成本等)。每款使用Chiplet技术的大芯片一定是分与合共同作用的产物。采用Chiplet技术通常有以下4个优势:

(1)芯片可分解成特定模块。这可使单个芯片变得更小并可选择合适的工艺,以提高工艺良率,摆脱制造工艺的限制,降低成本。

(2)Chiplet小芯片可被视为固定模块,并可在不同产品中进行复用,具有较高的灵活性。这不仅可以加快芯片的迭代速度,还能提高芯片的可扩展性。

(3)Chiplet可以集成多核,能够满足高效能运算处理器的需求。

(4)相较于更先进的半导体工艺制程,Chiplet的综合成本更低,收益更高。

目前业内都在积极开展Chiplet的技术布局,包括Intel、AMD、Marvell等知名公司。相关产业生态链也在逐步完善中。2022年3月,Intel牵头并联合9家公司(高通、ARM、AMD、台积电、日月光、三星、微软、谷歌云、META)制定了通用芯粒互连技术(UCIe)标准。该标准实现了互连接口标准的统一,使不同芯片都可以通过统一的协议互连互通,大幅改善了Chiplet技术生态。

在2022年的ISSCC会议上,AMD详细解读了通过3D封装实现3D V-Cache的技术。AMD应用台积电的小外形集成电路(SoIC)技术,将V-Cache放置在CPU计算内核(CCD)上。这块用于扩展L3 Cache的裸片(Die)不会覆盖CPU核。通常CPU核的上方会被放置一层硅片,这样封装尺寸就不会发生变化,热设计也能得到很好的满足。通过3D V-Cache的扩展,每个CCD上的8个CPU核能共享的L3 Cache由原来的32 MB扩展到96 MB。

Intel在2019年发布了一款名为Lakefield的处理器。该处理器采用了Chiplet架构,将10 nm制程的计算Die与22 nm的输入/输出(I/O)Die通过Intel的Foveros技术封装在一起。在2022年ISSCC会议上,Intel又发布了一款采用Chiplet技术的芯片Ponte Vecchio。该芯片拥有超过1 000亿个晶体管,包含5类芯片,并由47个Chiplets组成:16个Xe-HPG架构的计算芯片、8个Rambo Cache芯片、2个Xe基础芯片、11个嵌入式多芯片互连桥(EMIB)连接芯片、2个Xe Link I/O芯片和8个高带宽存储(HBM)芯片。这些Chiplet通过CoEMIB封装在一起。

除了Intel与AMD等在大力发展Chiplet技术外,中国芯片企业也在纷纷布局Chiplet技术。例如,中兴通讯在某个高性能CPU项目中,同样采用了Chiplet技术。Chiplet技术主要包含高速接口技术、先进封装技术、标准协议和生态建设。高速接口技术就如同智慧大脑中的血管技术,为数据的传输提供保障,它的主要指标包括能效、带宽、时延。先进封装是Chiplet的基石,它能使每个Chiplet小芯片连接在一起,从而构成整个系统级的芯片。标准协议可确保每家的芯片都能组合到一起,有利于互联网协议(IP)的重复使用。生态建设决定了Chiplet技术的推广和应用,它需要上下游各方的共同努力,以便实现良性可持续发展。然而,目前多芯片模块(MCM)的性能、成本和成熟度仍面临巨大挑战。例如,MCM芯片热流密度会逐渐增大,芯片内热阻较大,热点(Hotspot)现象呈现三维分布趋势。导热界面材料(TIM)材料和散热盖(Lid)材料的热阻以及均温性均是目前影响封装散热的关键因素。对此,业界常常采用金属TIM或石墨烯TIM材料、真空腔均热板散热盖(VC Lid)和金刚石键合等工艺,但这种方法面临的封装工艺挑战较大,会存在鼓包、翘曲、轻微气泡等问题。虽然芯片级液冷是未来解决大功耗芯片散热的最佳途径,但刻蚀工艺复杂,可靠性要求非常高,该技术目前还处于原理样机的研究阶段。

2 Chiplet接口标准

2.1 SerDes串行互连技术

SerDes串行互连技术采用差分信号传输方式实现了数据的高速传输,具有功耗低、抗干扰强、速度快的优点。根据发射端与接收端之间的距离,互连的SerDes技术可细分为长距(LR)SerDes、中距(MR)SerDes、短距(VSR)SerDes、极短(XSR)SerDes和超短距(USR)SerDes。其中,LR/MR/VSR SerDes的相關技术已经较为成熟,应用比较广泛,封装成本也较低,但缺点是功耗和信号的延迟比较大。XSR的光网络论坛-通用电气接口规范(OIF-CEI 4.0)是专门针对Die之间互连的,并向着100 Gbit/s的方向发展。相较于LR Serdes,XSR Serdes具有功耗低、面积小、通信协议灵活的特点。USR SerDes通过信号增强可进一步降低SerDes的功耗。封装产品可以根据不同项目产品的需求选择合适的SerDes类型,以实现成本与带宽的平衡。

2.2并行互连技术分析

在串行互连的基础上,各大公司技术联盟提出了基于并行数据传输的物理层互连技术。其中,具有代表性的是UCIe。UCIe是Intel主推的一个开放的、多协议兼容的、可满足不同客户对定制封装内多Die互连需求的技术标准。UCIe可同时支持2.5D、3D封装技术,例如MCM、晶圆级封装(CoWoS)、EMIB等。

UCIe 1.0使用成熟的高速串行计算机扩展总线标准(PCIe)和计算机互连标准(CXL)作为低功耗的裸片到裸片(D2D)互连物理层(PHY),可兼容多个协议,包括PCIe、CXL和Raw Mode。同时UCIe支持UCIe Retimer。这样UCIe就能够把互连的结构延伸到封装外。UCIe Retimer一端采用UCIe协议,另外一端采用CXL协议,这样可实现从封装内互连到封装外互连的巧妙转换。综合来看,这套标准可以使不同制造商的小芯片实现互通,即允许不同厂商的芯片进行混搭。不同于之前的业界并口标准,UCIe是一套完整的全栈协议,具有互操作性,并与现有的行业标准兼容,同时未来还将支持3D封装。此外,由于协议制定单位均为业界龙头公司(涵盖制造、设计、应用等领域),UCIe在未来极有可能成为行业统一的标准。Intel推出该标准的目的在于建立以CPU为中心的计算生态环境。此外,NVIDIA于2022年8月宣布加入UCIe组织。Intel曾表示,未来至关重要的是一个开放的小芯片生态系统。对此,主要行业合作伙伴应共同努力,改变行业交付新产品的方式,以实现摩尔定律设定的共同目标。

中兴通讯于2021年开始布局Chiplet互连互通标准,并于2022年6月向中国半导体器件标准化技术委员会半导体集成电路分会(TC78SC2)提交了标准提案。虽然Chiplet受到了业界同行的广泛关注,但是该标准还未在国际标准组织中正式立项。鉴于UCIe的强大性,如果在流协议(各厂家可定义)的上层增加一层协议,系统就无须再使用PCIe/CXL协议。这有助于推动中国Chiplet的互连互通。

3 Chiplet中的先进封装技术

Chiplet技术发展的基础是先进封装。要将多颗芯片高效地整合起来,必须采用先进封装技术。在芯片尺寸不断增大、架构变得复杂的情况下,封装结构由原先的二维发展至三维。按封装介质材料和封装工艺划分,Chiplet的实现方式主要包括以下几种:MCM、2.5D封装、3D封装。比如,台积电的2.5D先进封装技术CoWoS、InFO_oS已经被广泛应用。新的封装形式和结构还在不断演进。诸如SoIC的3D封装技术将在2023年得到广泛应用。

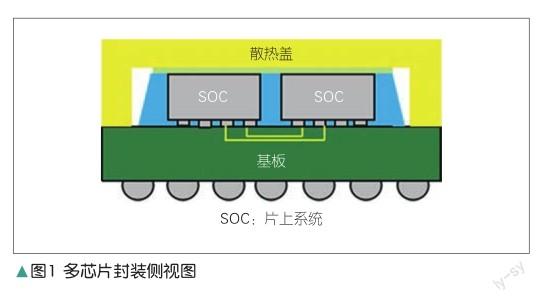

3.1 MCM封装

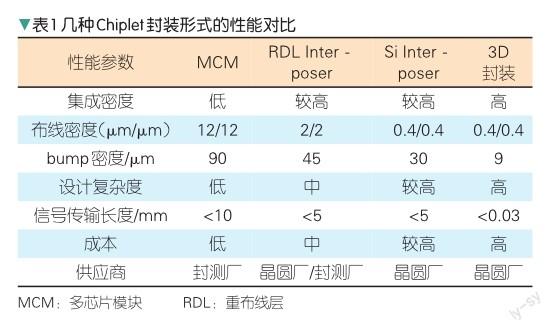

MCM封装是指通过引线键合、倒装芯片技术在有机基板上进行高密度连接的封装技术。图1为MCM封装的侧视图。引线键合与框架封装一般用于I/O数目较少、对信号速率要求较低的情况,而倒装芯片技术可以支持更高的信号速率、更短的信号传输路径。凸块技术用于完成芯片与有机基板的键合,可将多颗不同功能的芯片封装在同一个有机基板上。基板上金属线的互连使芯片与芯片之间的电气进行互连。相对于硅工艺的互连衬底,封装有机基板工艺成熟,在材料和生产成本上有巨大优势。MCM封装能够满足Chiplet芯片需求,封装尺寸可以达到110 mm×110 mm。但受限于基板加工工艺能力,目前封装基板上的走线宽度/间距一般为9μm/12μm。为保证铜走线的工艺控制,在设计时信号走线的线宽大多在12μm以上,布线密度比2.5D封装低。

3.2 2.5D封装

2.5D封装是指在Chiplet芯片之间通过中介层(转接板)进行高密度I/O互连的封装,其特点是多Die集成和高密度性。根据目前的工艺水平,2.5D封装又主要分为重布线层(RDL)Interposer和Si Interposer。

3.2.1 RDL Interposer

RDL Interposer封装能够通过RDL在晶圆级上使多个芯片完成电性连接。相较于MCM封装,RDL Interposer封装技术可以将芯片与芯片之间的距离变得更小,使信号走线宽度和间距大幅度降低,从而提高单位面积的信号密度。目前信号线宽/线距最小可以为2μm/2μm。由于芯片与芯片的间距可以做到60~100μm内,所以D2D信号互连距离可以控制在5 mm以内。相对于Si Inteposer,2.5D RDL Interposer省掉了硅通孔(TSV)工艺,具备更低的热阻和更好的机械特性。RDL介质层采用的是高分子材料,其热膨胀系数和基板类似,因此可以减少对Die的机械应力。图2和图3分别为2.5D(RDL Interposer)Chiplet芯片封装正视图和侧视图。另外,RDL Interposer中金属铜的厚度可以做得更大,金属铜的电阻率也可以做到更低,这有助于降低RDL走线的损耗。

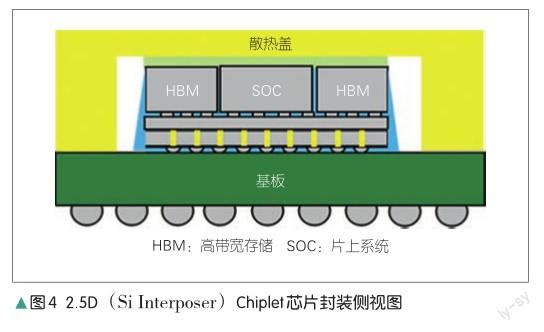

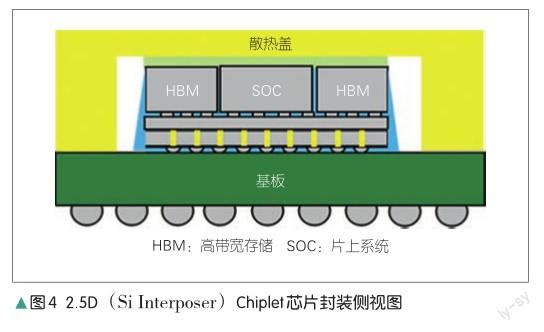

3.2.2 Si Interposer

Si Interposer技術是基于硅工艺的传统2.5D封装技术。该技术在基板和裸片之间放置了额外的硅层,可以实现裸片间的互连通信。中介层则是在硅衬底上通过等离子刻蚀等技术制作的带TSV通孔的硅基板。在硅基板的正面和背面制作RDL可为TSV和硅衬底上集成的芯片提供互连基础。在硅基板上通过微凸点(ubump)和C4凸点(C4 bump)可最终实现芯片和转接板、转接板与封装基板的电性能互连。图4为2.5D(Si Interposer)Chiplet芯片封装侧视图。目前Si In‐terposer的信号线宽/线距最小可以做到0.4μm/0.4μm。相对于RDL Interposer来说,Si Interposer的信号布线密度进一步提高,可以实现更高的I/O密度以及更低的传输延迟和功耗。然而与有机基板及RDL Interposer相比,Si Interposer的成本更高。目前中兴通讯已有采用Si Interposer封装技术的网络交换芯片产品。该产品搭载HBM颗粒,可实现更优异的产品性能。

3.3 3D封装

3D封装是指在2.5D封装技术的基础上为了进一步压缩bump密度,直接在晶圆上通过硅穿孔实现连接的一种封装技术。目前3D封装主要采用Wafer on Wafer、Chip on Wafer的混合键合技术。该方法能够实现的最小键合距离为9μm。由于芯片本身取消了凸点,集成堆叠的厚度变得更薄,因此芯片厚度可以薄至20~30 um。这减少了芯片信号的寄生效应,提高了系统性能。表1列出了几种Chiplet封装形式的主要性能参数。可以看出,3D封装是集成密度最高的。此外,三维集成电路(3DIC)也为Chiplet提供了极大的灵活性。设计人员可在新的产品形态中“混搭”不同的技术专利模块与各种存储芯片及I/O配置。这使得产品能够分解成更小的“芯片组合”。其中,I/O、静态随机存取存储器(SRAM)和电源传输电路可以集成在基础晶片中,而高性能逻辑“芯片组合”则堆叠在顶部。此外,可以在CPU之上堆叠各类小型的I/O控制芯片,从而制造出兼备计算与I/O功能的产品;也可以将芯片组与各种Type-C、蓝牙、WiFi等控制芯片堆叠在一起,制造出超高整合度的控制芯片。

3.4散热解决方案

3.4.1 2D/2.5D方案

2D/2.5D封装方案在散热方面遇到的瓶颈问题是整体功耗较大。对此,业界通常采用Metal TIM或是石墨烯类的TIM材料,如图5所示。这类材料具有较高的导热系数(分别达到80 W·m-1·K-1和20 W·m-1·K-1),不仅能有效降低TIM自身的材料热阻,还能降低Die内的温差。

此外,有关Lid优化的研究也有很多,例如金刚石铜复合Lid、金刚石银复合Lid和VC Lid。从应用前景来看,金刚石铜复合Lid和金刚石复合Lid带来的收益比较有限,且表面工艺问题难以解决,与TIM材料的兼容性较差。由于Vapor相变层快速转换热量,导热率明显提升(约为铜Lid的4倍),因此VC Lid具有不错的应用前景。然而,VC Lid也存在一些封装工艺问题,例如鼓包、翘曲等。

3.4.2 3D方案

对于3D封装结构,为了解决Die堆叠中功率密度叠加的问题,AMD采用键合一层结构硅(Dummy die)的方法。这不仅能起到均温作用,还可解决因公差引起的应力问题。此外,Intel也采用相似的方案。Dummy die的材料包括Si和其他材料。近年来已有研究证明,在GaN或是SiC衬底芯片上键合一层金刚石,可以解决因高功率密度引起的过大温差分布问题。如果Dummy die选择导热率更为优良的金刚石,那么效果会更加明显。

除了TIM材料、系统散热技术外,3D封装芯片散热方案还考虑了内部热源问题。目前芯片级液冷技术是解决这一问题的最佳方法。美国国防先期研究计划局(DARPA)早在2012年便启动了芯片内/芯片间的增强冷却(ICECool)[5]项目。在该项目中,佐治亚理工学院基于倒装芯片架构,采用蚀刻工艺探究了芯片级液冷方案,改善了2.5D、3D芯片架构热耦合的效果[6]。洛桑联邦理工学院(EPFL)在2020年发表在《Nature》杂志上的文章显示,流型通道(MCC)方案散热能力为1 723 W/cm2@60℃[7]。

3.5电热力耦合问题

先进封装和系统集成技术不断演变,不仅提高了电性能,还实现了多样化集成,包括通过异质集成方法实现的具有多种形式的微系统。然而,相应的复杂度和可靠性问题却变成一个更为严峻的挑战。目前2.5D、3D芯片的主要应用场景包括人工智能、网络通信、高性能计算等,其功耗通常较高。因此,如何保证电源完整性和大电流下的散热能力至关重要。另外,复杂的封装结构通常会包含力学特性差异较大的不同材料结构,在焦耳热和封装工艺下均会带来较高的热应力风险。因此,在基于Chiplet技术的应用过程中,由高功率电磁脉冲、芯片自热耗散等引起的电、热、应力等多物理效应十分突出。这需要人们探索相关仿真技术和研究方法,以便为优化设计提供指导。

基于先进集成封装技术的多物理效应主要由电流连续性方程、热传导方程和弹性力学方程组等描述。焦耳热和功率耗散等因素会引起温度升高,产生热变形和热应力。变形会导致仿真模型网格发生变化,反过来会影响电场和温度分布。另外,溫度的改变还会引起材料属性发生变化,导致电场、温度场、应力场发生变化。

目前芯片功耗越来越大,球栅阵列(BGA)/栅格阵列(LGA)的通流能力也在不断提升。由此引发的系统自发热问题不仅会影响芯片的结温,还会对自身端子温度产生较大影响,进而会对系统可靠性造成干扰。BGA/LGA通流仿真涉及电流、热的协同仿真。由于BGA/LGA管脚数量较多,所需的网格量较大,并且端子较为复杂,异型结构仿真需要先做等效简化(简化成圆柱体),然后再做整体的电热联合仿真。

集成封装的结构和材料特性十分复杂,几何尺度跨度大,多场耦合联动效应更为复杂,因此精确多场表征的难度较大。目前市面上有多款可用于分析多物理场耦合的商业软件,其中比较常用的有ANSYS和COMSOL。它们都是基于有限元方法进行多物理场仿真分析的。传统的仿真工具受限于计算机资源,无法处理全芯片模型,通常都会进行简化或利用等效模型来处理。因此,人们需要研究针对三维集成封装中多物理问题的高性能仿真算法。随着Chiplet技术的不断发展,多学科交互与协作将趋于日常化。因此,如何通过各学科人员的紧密合作对多物理场耦合现象进行更为精确的分析,将是业界共同努力的方向。

3.6 CPU Chiplet封装实践

在后摩尔定律时代,由制程工艺提升带来的性能受益已经十分有限。受到缩放比例定律的约束,芯片功耗急剧上升,晶体管成本不降反升,单核的性能已经趋近极限,多核架构的性能提升速度亦在放缓。如何在先进制程之外探索一条CPU性能提升的线路,以覆盖各种高性能计算的场景,已成为各大芯片厂商关注的问题。随着云服务、人工智能、元宇宙时代的来临,下游算力需求呈现多样化及碎片化,而通用处理器不能满足相应需求。因此,CPU也需要不断发展与演进。这具体包括以下几个方面。

(1)芯片定制化:针对不同的场景特点设计具有不同功能的芯片。

(2)架構优化:架构的优化能够最大程度地提升处理器性能。

(3)异构与集成:似乎是延续摩尔定律的最佳实现路径。例如,苹果M1 Ultra芯片利用逐步成熟的3D封装、片间互连等技术,使多芯片有效集成。

在CPU中可以采用2.5D先进封装形式,利用高速并行D2D互连接口将两个芯片通过InFO集成到一起,以构成超大规模的芯片系统。利用多层RDL的InFO结构,结合小尺寸的凸点间距,并采取2μm/2μm的线宽/线间距,可实现更高密度的带宽。

4总结与展望

基于Chiplet的异构集成芯片技术代表了“后摩尔时代”复杂芯片设计的研制方向。Chiplet这种将芯片性能与工艺制程相对解耦的技术为中国集成电路技术的发展开辟了一个新的发展路径。该技术借助现有成熟工艺来提升复杂芯片的性能。作为一种新兴技术,当前Chiplet正处于发展阶段。相关大量关键技术尚未形成标准。中国学术界和产业界应抓住机会,在技术研发和标准制定方面加大投入,尽快掌握核心技术。此外,芯片行业参与者需要避免单打独斗,应注重生态建设,早日建立业界接受的基于Chiplet的异构集成技术标准,以便在未来国际竞争中占据一席之地。

致谢

本研究得到中兴通讯股份有限公司谢业磊高级工程师、严斌高级工程师、孟福生高级工程师、谭晓东高级工程师、陈桂显高级工程师的帮助,谨致谢意!

参考文献

[1]刘新阳. 5G半导体产业发展和创新趋势思考[J].中兴通讯技术, 2021, 27(4): 51-51. DOI: 10.12142/ZTETJ.202104010

[2] SATO K, ZHANG X B. Semiconductor optical amplifier and gain chip used in wavelength tunable lasers [J]. ZTE Communications, 2021, 19(3): 81-87. DOI: 10.12142/ZTECOM.202103010

[3]蔡济帆,徐增熠,迟楠.可见光通信星座整形与人工智能解调技术[J].中兴通讯技术, 2022, 28(4): 19-24. DOI: 10.12142/ZTETJ.202204005

[4] ZHANG C C, ZHANG N, CAO W, et al. AI-based optimization of handover strategy in non-terrestrial networks [J]. ZTE Communications, 2021, 19(4): 98-104. DOI: 10.12142/ZTECOM.202104011

[5] BAR-COHEN A,MAURER J J,FELBINGER J G.DARPAs intra /interchip enhanced cooling (ICECool) program[C]//2013 CS MANTECH Conference. IEEE, 2013: 201-206

[6] BAR-COHEN A,MAURER J J,HAMILTON B A.DARPAs intrachip enhanced cooling program (ICECool): embedded cooling for RF and digital electronics[C]//2015 IEEE MTT-S International Mierouave Symposium. IEEE, 2015: 61-70

[7] ERP V R, SOLEIMANZADEH R, NELA L, et al. Co-designing electronics with microfluidics for more sustainable cooling [J]. Nature, 2020, 585: 211-216

作者簡介

李乐琪,深圳市中兴微电子技术有限公司封测工程部封装设计工程师;主要从事2.5D、3D先进封装的封装方案评估及封装设计工作,参与并支持了多个预研项目及产品项目的设计与交付。

刘新阳,深圳市中兴微电子技术有限公司副总经理,在中国通信学会集成电路专委会、中国半导体行业协会、集成电路产业技术创新战略联盟等多个行业协会中担任委员或理事会理事;主管战略规划、技术规划、品牌和政府公共关系,拥有24年的IC设计行业从业经验,主持了多个重大产品的研发项目并完成批量商用交付。

庞健,深圳市中兴微电子技术有限公司封测工程部封装设计总负责人,主要负责封装技术规划和封装技术预研,拥有20余年项目开发经验,主持了多个商用产品的交付项目。