一种用于脉冲延时发生器中消除触发抖动的方法

梁东飞苏淑靖梁文科邢震震周广兴

(中北大学省部共建动态测试技术国家重点实验室,山西 太原 030051)

脉冲延时发生器作为时序控制部件在诸多领域中发挥了重要的作用,如在测量子弹飞行参数的超高速分幅相机中[1-2],脉冲延时发生器用于设定高分辨率的快门延时时间,首先接收现场发出的外部触发信号,然后依次产生增强器的选通信号。在此过程中触发抖动影响系统的分辨率,降低拍摄的质量,是分幅相机普遍面临的问题之一。因此当脉冲延时发生器工作在外触发模式下时,触发信号与时序电路时钟的同步问题是提高脉冲质量的关键。

文献[3]分析了脉冲延时发生器触发抖动的产生机理,采用时钟约束方法设计高频计数延时电路来抑制抖动,但并没有消除触发信号与系统时钟的抖动。文献[4]中提出了一种基于FPGA 精细调节单元IODELAY 级联实现低抖动同步脉冲技术,这种方法避免了时序电路时钟与触发不同步问题,但是由于FPGA 内的延迟单元有限且不可调节,导致脉冲延时的范围小且分辨率低。文献[5-6]中使用电容充放电技术实现抖动消除,其抖动测量稳定性和准确性由恒流源的输出精度和稳定性、开关的开通速度、电压损耗稳定性和电容容量稳定性决定,该方法电路复杂且影响系统稳定性的因素较多,不易设计。

针对脉冲延时发生器的外部触发信号与时钟信号不同步问题,提出了消抖方法。该方法采用数字时间转化(Time-to-Digital Converter,TDC)原理对随机抖动进行高精度实时测量,延时电路进行相应的随机抖动补偿。测量电路使用全数字电路实现,补偿只需要在原有延时上增加一个补偿量,就可使其性能稳定且不影响时序电路对脉冲的延时功能。该方法对高精度宽范围的脉冲延时发生器研制有重要意义。

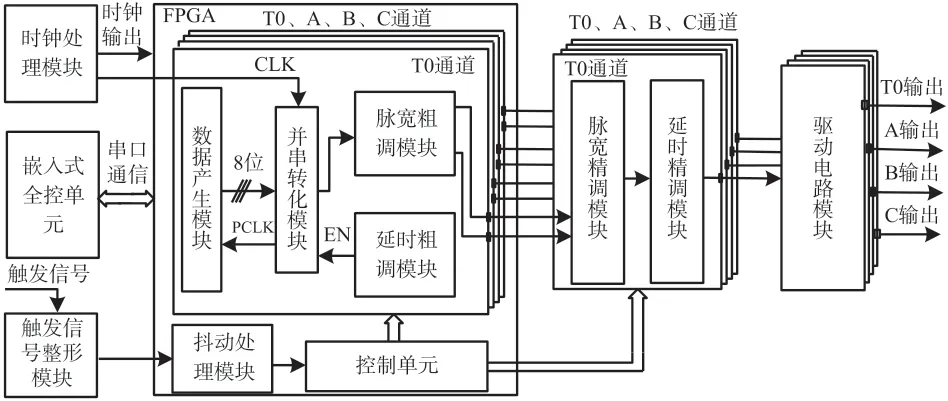

1 脉冲延时发生器总体方案

图1 为四通道脉冲延时发生器的原理框图,各通道原理相同,硬件主要有触发信号整形模块、数据产生模块、并串转化模块、脉宽和延时粗调模块、脉宽和延时精调模块、驱动电路模块、抖动处理模块、时钟处理模块、嵌入式全控单元和控制单元。其中数据产生模块、并串转化模块、脉宽和延时粗调模块、控制单元和抖动处理模块在FPGA 内部实现。在FPGA 接收到嵌入式全控单元下发的通道延时、脉冲参数和脉冲类型的指令并对系统各个模块进行相应的配置后,脉冲类型的数据存储在数据产生模块中,通过并串转化模块生成相应的脉冲。控制单元在接收到外部触发信号或自生成触发信号后,延时粗调电路开始工作,完成延时后启动并串转化模块生成相应的脉冲。设计了脉宽粗调电路将生成脉冲扇出两路经过延迟单元进行脉宽粗调,两路脉冲再经过脉宽精调的延时电路后合成设定脉宽的脉冲信号,此脉冲宽度为两路信号的相对延时。最后脉冲经过延时精调模块后通过驱动电路模块生成幅值可调的脉冲。

图1 脉冲延时发生器原理框图

脉冲延时发生器可在内触发或外触发方式下工作,当工作在内触发方式时,触发信号由内部控制单元在系统时钟驱动下产生,时钟和触发信号是同步的。当工作在外部触发方式时,系统时钟通过上升沿同步由外部输入的触发信号时会产生抖动,抖动会降低脉冲延时的分辨率和精度。所以针对此问题,本文提出了一种随机抖动的消除方法。

2 随机抖动消除方法及硬件设计

2.1 随机抖动消除原理

外触发模式下随机抖动产生机理如图2 所示。如果设定触发信号和T0通道的延时时间为Td=NT+t,其中T为系统的时钟周期,t为小于T的细延时时间。由图2 可知未补偿的T0通道的延时会比设定值Td大一个随机抖动时间Tj,Tj的值在(0,T)随机分布。如果将触发信号造成的Tj测出并送给控制单元,在系统粗延时完成后再额外增加一个补偿时间Tc满足公式(1),使得Td=(N-1)T+Tc就可以消除随机抖动,其中(N-1)T为粗延时时间,Tc作为细延时时间。

图2 随机抖动产生

随机抖动的消除原理如图3 所示,该电路主要由抖动测量模块和抖动补偿模块组成。其中抖动测量模块采用抽头延时链技术,当外触发信号输入时,通过控制单元启动脉冲产生电路进行延时粗调。同时抖动测量模块对400 MHz 时钟同步外触发产生的随机抖动进行测量,并将测量结果通过控制单元发送至抖动补偿模块进行补偿输出。

图3 随机抖动消除硬件电路结构

2.2 抖动测量电路设计

抖动测量电路原理如图4 所示,由三输入三链TDC 组成。触发信号经过处理后生成脉冲间隔为5T,脉冲个数为3 的触发脉冲,将触发脉冲送给3 条输入路径。输入路径和延时链用开关矩阵进行相互连接,切换开关矩阵的状态使每条延时链分别连接3 条输入路径。在触发脉冲的上升沿到来时,3 条延时链开始同时测量,测量完成后改变开关矩阵状态,等待触发信号的第二个脉冲上升沿到来时再次进行测量,3 次测量完成后进行编码发送给FIFO。TDC 选用400 MHz 的时钟信号,该信号由超低相位噪声的模拟锁相环芯片ADF4356 倍频得到,ADF4356 的时基选用IQD 公司的10 MHz 的铷时钟LFRBXO059244Bulk,具有±1.5×10-9的频率稳定度,有助于更精确的测量[7]。

图4 TDC 测量原理

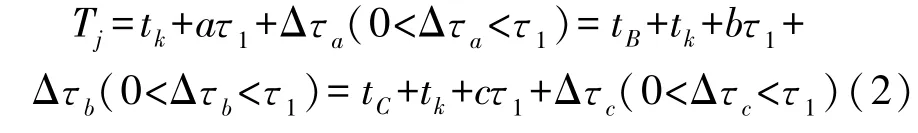

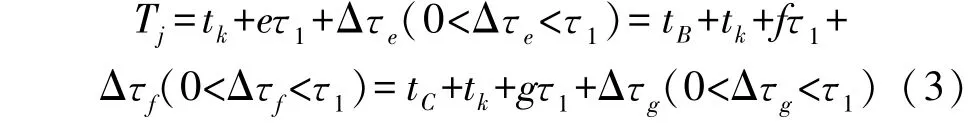

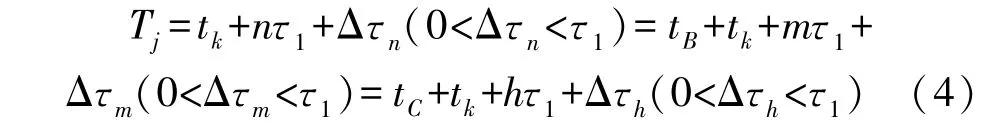

在测量过程中,随机抖动大小由输入单元,开关矩阵和延时链3 个部分的总延时组成。路径B和路径C的输入单元延时时间定义为tB和tC,开关矩阵的延时定义为tk,3 条延时链中延迟单元的时间分别定义为τ1、τ2、τ3。第一条延时链测量的随机抖动Tj表示为:

式中:Δτa、Δτb和Δτc为A、B、C三条路径经过第一条延时链的测量误差,a、b和c为三条路径经过第一条延时链的延迟单元个数。第二条延时链测量的随机抖动Tj为:

式中:Δτe、Δτf和Δτg为A、B、C三条路径通过第二条延时链的测量误差,e、f和g为三条路径经过第二条延时链的延迟单元个数。第三条延时链测量的随机抖动Tj为:

式中:Δτm、Δτn和Δτh为A、B、C三条路径经过第三条延时链的测量误差,m、n和h为三条路径经过第三条延时链的延迟单元个数。由式(2)、式(3)和式(4)可知,测量结果可用S(a,b,c,e,f,g,n,m,h)表征随机抖动Tj,测量结果中的9 个变量表示对延时链的延迟单元进行了9 次的分割,为简化分析,图5 为该TDC 的第一个触发脉冲测量时的时间分割原理。由于输入单元的延时不同和延时链中延迟单元的差异性,导致每一个延迟单元的开始和结束位置相互错位。当第一个触发脉冲输入到三输入三链TDC 时,假设测量时间的停止点落在A点时,延时链1 经过的延迟单元个数为a,测量结果的误差范围为第a个延迟单元的延时时间,单条延时链的测量结果的精度由延迟单元的延时决定。延时链2 和3 经过的延迟单元个数分别为f和h,测量结果落在时间分割后的第i(a,f,h)个延迟单元。测量结果的误差范围为三条延时链的测量交集(分割后的第i个延时单元),测量精度相比于单链进一步提高,摆脱了延时单元的延时大小对测量精度的束缚。由于输入单元和每个延迟单元的延时时间不确定性,完整的三输入三链TDC 的精度由TDC 码密度校正的结果决定。

图5 并行延时线时间分割示意图

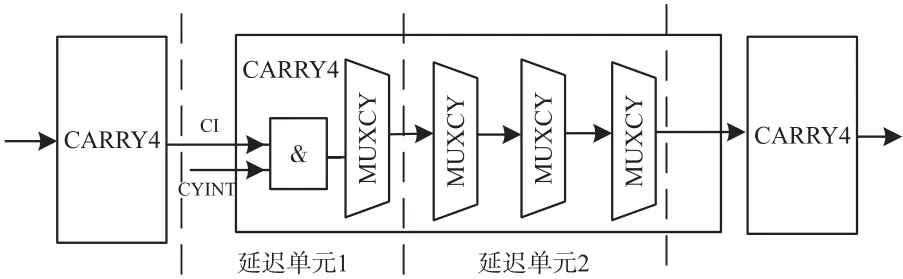

延时链选用FPGA 的CARRY4(超前快速进位逻辑结构)级联构成。为了减小延迟单元的差异性,将CARRY4 整个逻辑单元分割为两个延迟单元,如图6所示。在400 MHz 的工作频率下,Xilinx 的Artix-7系列FPGA 平均每个延迟单元为33 ps,至少需要76个延迟单元才能满足测量需求。考虑到温度对延时链的影响,为TDC 的测量范围留有一定的裕量,设计每条测量链包含80 个延迟单元[8-10]。

图6 CARRY4 分割方案

2.3 抖动补偿模块设计

由式(1)可知,补偿时间的范围为0~5 ns。5 ns的延时范围比较容易实现,而更好的补偿精度需要更高分辨率的延时控制,选用MC100EP196 延时芯片,借助其数字控制和压控功能可实现高达1 ps 的分辨率,其延时电路原理如图7 所示。抖动补偿模块的粗延时电路通过控制延时阵列实现10 ps 到5 ns 的延时,分辨率为10 ps。细延时电路使用外部输入电压调节压控延时实现0~10 ps 的延时,分辨率为1 ps。

图7 MC100EP196 延时电路原理

数字控制延时电路的实现比较简单,将锁存器的使能信号清零,就能够实时地通过FPGA 给MC100EP196 发送十位的二进制的延时指令。压控延时电路的控制电压由20 位的DACMAX5719 产生,并且通过电压跟随器将其输出和MC100EP196隔离来增强驱动能力和抗干扰能力。DAC 的4.096 V参考电压由高精度基准电压源LT1461 产生,保证了参考电压的精度和稳定性。由于MC100EP196 的输入信号是差分信号,所以选择SN65EPT22D 将FPGA 产生的单端脉冲信号转化为差分信号。

通过对实际芯片的测试,得出延时指令Data 和设定的延时时间td(ps)之间的关系为:

3 TDC 码密度校正

由于工艺不同导致每个延迟单元的时间存在差异,因此需要对每一个延迟单元进行校准。使用随机脉冲作为TDC 的输入信号,随机脉冲与时钟信号的时间间隔在(0,T)范围内随机分布,当样本容量足够大时,认为输入的随机脉冲均匀分布。如果某一级的延迟单元的延时时间越长,则测量结果落入该延迟单元的次数越多。统计测量结果中每一级延迟单元的次数,次数越多则延迟时间越大,若第k个延迟单元的次数为nk,则第k个延迟单元的的延迟时间Tk为式(6)所示[11-12]。

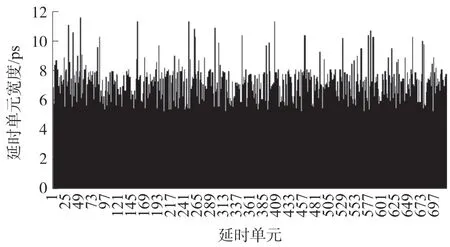

通过码密度校正,得到三输入三链TDC 经过分割后的每一级延迟单元的延时时间估计值,如图8所示。其横坐标为所有分割后的延迟单元按时间先后排列的序号,纵坐标为每个延迟单元的延迟时间。

图8 延迟单元延迟时间测试图

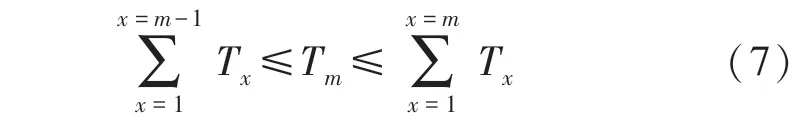

假设测量结果落在第m个延迟单元,则可以求出所测量时间间隔Tm的范围为:

由式(7)可知,Tm需要一个值Ti(Ti∈Tm)来表示,使测量误差最小,测量的标准方差可以表示为:

对式(8)求导可知,测量结果的最后一个延迟单元选取Ti=(Ti+Ti-1)/2 时方差最小。

4 实验结果

对所设计的三输入三链TDC 的精度进行测试,时间间隔的测量精度定义为单次测量精度,用固定的时间间隔测量结果的标准差来表示。当输入时间间隔为2 ns 时,测量30 次的结果如图9 所示,RMS精度为18.9 ps。

图9 时间间隔测量结果

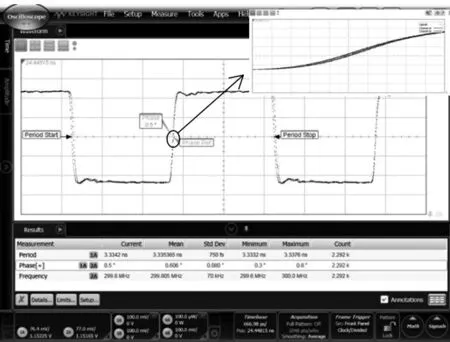

为了消除延时补偿模块的固有延时对测试的影响,使用脉冲码型发生器81134A 生成两路同步信号channel 1 和channel 2,频率设置为300 MHz,占空比50%,输出电平1.5 V,用延时补偿模块对channel 1 进行2.997 ns 的延时,对channel 2 进行3 .000 ns 的延时。使用带宽为20 GHz 的DCA-X 86100D 示波器测试两路延时后的脉冲,测试结果如图10 所示。从测试结果可以看出,两个通道的相位差为0.3°~0.8°,计算可得延时补偿电路对应3 ns延时的抖动最大为4.2 ps。

图10 实验结果图

5 结论

本文介绍了一种延时脉冲发生器消除抖动的方案,对其主要的模块进行了详细的论述。通过TDC测量出随机抖动的值,然后通过延时电路来补偿时钟与触发不同步造成的抖动。分别对测量模块和延时补偿模块进行测量,实验结果表明:测量模块造成脉冲的抖动为18.9 ps,抖动补偿模块的抖动为4.2 ps,最终系统的抖动为19.3 ps,有效地抑制了抖动,对研制低抖动高精度延时脉冲发生器具有一定的参考和应用价值。