带隙基准电压源的抗SET 设计

翟馗斌,卢雪梅,郝 宁,王 涛,葛维维,李 博,轩 昂,杨孙伟,郭明齐,王赢玺

(1.辽宁大学物理学院,沈阳 110080;2.中国科学院微电子研究所,北京 100017)

1 引 言

近些年来,随着集成电路的快速发展及集成电路应用领域的广泛拓展,研究航天领域的集成电路成为我国科技发展的重中之重。对于空间站及航天器,单粒子瞬态效应一直是影响电子器件正常工作的主要原因[1]。宇宙中的高能粒子入射电路后,带电粒子与电子元器件碰撞,电离产生电子-空穴对。如果在敏感节点处发生,其产生的载流子会被电场收集,形成瞬态的脉冲电流,从而使电路性能退化或失效[2]。这种影响即称为单粒子效应(Single Event Effect,SEE),其中单粒子瞬态(Single Event Transient,SET)主要是通过影响电路中的某一个敏感节点来影响其功能的[3]。带隙基准电压源作为DC-DC 转换器、LDO 电路及ADC 电路中的重要组成部分,其输出的变化一旦受到此类效率的影响,将对整个电路的运行构成威胁。在此提出一种通过电流补偿进行单粒子翻转加固的带隙基准结构,并基于0.18 μm体硅工艺完成电路设计工作。

2 抗SET 带隙基准电路设计

2.1 带隙基准电路

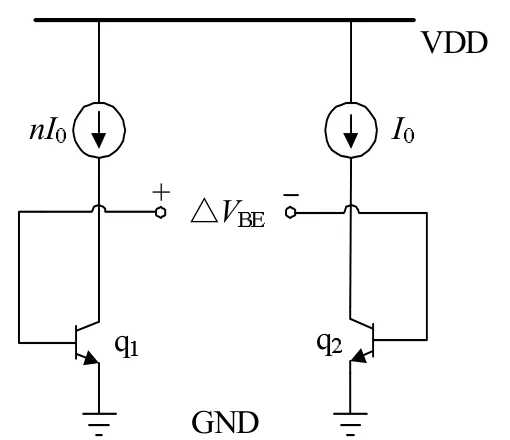

带隙基准电路是在调节器件尺寸参数并进行合理设计后,输出一个几乎不受温度影响的稳定的参考电压。1964 年,Hilbiber 发现了两个不同电流密度的三极管在工作时,两个三极管的基极-发射极电压之差与温度成正比[4]。正温度系数产生与温度成正比的PTAT 电流,原理如图1 所示。根据三极管的集电极电流和基极-发射极电压之间的关系,经过分析得知,该电流与温度成反比,即CTAT 电流。

图1 实现正温度系数的电路原理图

将正温度系数电压与负温度系数电压按照一定权重相加,可以得出具有零温度系数的带隙基准电压[5],公式如下:

通过以上分析并调整器件尺寸相关参数,设计出带隙基准电路,电路图如图2 所示。按照此设计,电路的输出电压基本不随温度的改变而变化,维持在1.19V 左右。

图2 带隙基准电路原理图

2.2 带隙基准电路的抗SET 加固

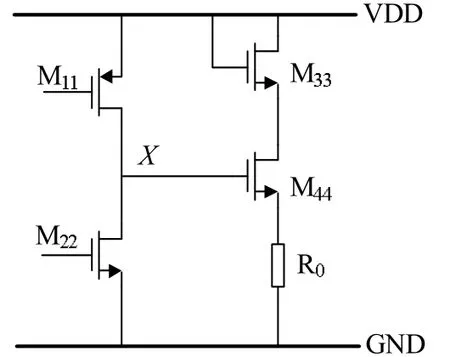

在模拟电路中,MOS 管的栅极电压对单粒子瞬态效应极其敏感,以如图3 的电路结构为例,如果SET 发生在X 点,高能粒子入射进入电子元器件内部后,导致输出电压突然增大,M44管的栅极电压发生变化,继而影响之后的放大电路的输出。为了减小SET 对电路的影响,提出一种SET 电流补偿电路,如图4 所示。

图3 电路敏感节点示例图

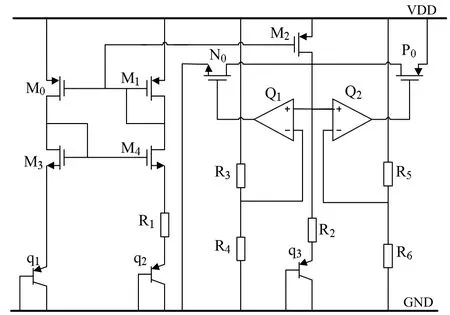

图4 带有抗SET 结构的带隙基准电压源

此电路由比较器Q1、Q2,一对互补晶体管P0、N0及四个电阻R3、R4、R5、R6组成。电流补偿电路的输入端连接带隙基准电压源的输出端,另一端与电阻R3、R4(R5、R6)并联,采取电阻分压的形式为其提供参考电压。比较器Q1(Q2)的输出端连接N0管(P0管)栅极,同时,N0、P0的漏极连接带隙基准电压源的输出端。此电流补偿电路的工作过程主要分为两种情况:

第一种情况是当电路正常运行、没有产生SET效应时,比较器Q1输出为低电平,Q2输出高电平,使两管均处于截止状态,此时不会影响电路的输出。

第二种情况是当高能粒子入射到电路中的敏感节点产生SET 瞬态电流时,电路的输出电压突然增大或减小。根据SET 效应产生脉冲信号的方向,比较器Q1或Q2发生电平转换,继而开启其输出连接的MOS 管,产生补偿电流,从而抑制SET 效应产生影响。比较器Q1输入的参考电压略高于带隙基准电路的输出。

图4 中的抗SET 加固电路具有互补的特点,如果单粒子射入抗SET 加固电路,在带隙基准电路没有发生SET 时,比较器连接的P0管(N0管)受SET瞬态电流的影响而误开启,就会产生电流使输出电压升高(降低)。当比较器输入的电压高于(低于)参考电压时,Q2(Q1)将开启P0管(N0管)产生补偿电流以保证带隙基准电压源的输出电压稳定,所以此抗SET 加固电路没有引入新的敏感节点。

本设计采用的比较器Q1如图5 所示。Q1与Q2结构与原理基本相同,只有部分MOS 管尺寸存在差异,采用带有有源电流镜和实际电流源的差动对,Vin-端为比较放大器的参考电压。采用电阻分压的方式,通过调节两个电阻的阻值之比,调节出合适的电压用来做Vin-的输入电压。此处Q1输入的参考电压为1.22V,Q2输入的参考电压为1.16V,具体应用时可根据不同工艺与电路应用需要进行调整。

图5 比较器Q1 电路原理图

在电路没有发生SET 效应时,比较器Q1的Vin+端的输入电压低于Vin-端的输入电压,但是二者的差值不大,M7、M9和M10都处于饱和区。当发生SET效应时,Vin+的输入电压受高能粒子影响突然增大,导致增大而ID9减小,最后导致比较器的输出电压增大。Q1输出的N0管开启,产生补偿电流从而抑制SET 带来的影响。Q2与Q1同理,当发生SET 效应导致电路的输出电压突然减小时,比较器Q2连接的PMOS 管导通,产生补偿电流,进而抑制SET 带来的影响。

3 SET 效应仿真与分析

3.1 仿真设计

电路验证采用Cadance 的Spectre 仿真,通过向敏感节点注入电路的方式进行能量粒子入射仿真。常用的SET 效应等效电流源基本分为两种,一种是双指数电流源,另一种为分段式电流源。Messenger等人提出的双指数电流源的模型[6],如下式:

其中,Qtot为辐射粒子穿过器件后留在器件内部的电荷;τ1为反偏PN 结的时间常数,τ2是建立辐射粒子初始化轨迹的时间常数。为电流源的峰值电流I0,其参数为:I0=130 μA,τ1=203 ns,τ2=200 ns。Spectre 仿真时间为1μs。

Qtot和粒子的能量传输值(LET 值)与收集深度成正比。此处也采用该模型进行粒子入射仿真。

为验证该电流补偿电路的加固效果,设计了三种电路进行仿真结果对比。第一种是抗辐照加固的带隙基准电路;第二种是普通带隙基准电路;第三种为复现文献[7]中的抗辐照结构。三种电路均采用相同的SMIC 180nm 工艺模型进行仿真。

3.2 单粒子瞬态仿真

为了便于比较,对未加固(图2)和已加固的带隙基准电路(图4)分别进行单粒子瞬态仿真。将相同的双指数电流源注入到电路中,使其在带隙基准电路的输出端产生瞬态电压[8]。对于未进行SET 加固的电路,其电压的上升时间和下降时间大约分别为20ps 和300ps。

在图4 电路中注入双指数电流源后,比较器Q1及Q2可以通过输出电压的变化,输出高低电平控制P0管和N0管开启或截止,进而降低对输出电压的影响。可见利用所设计的电流补偿电路来抑制SET 十分有效。

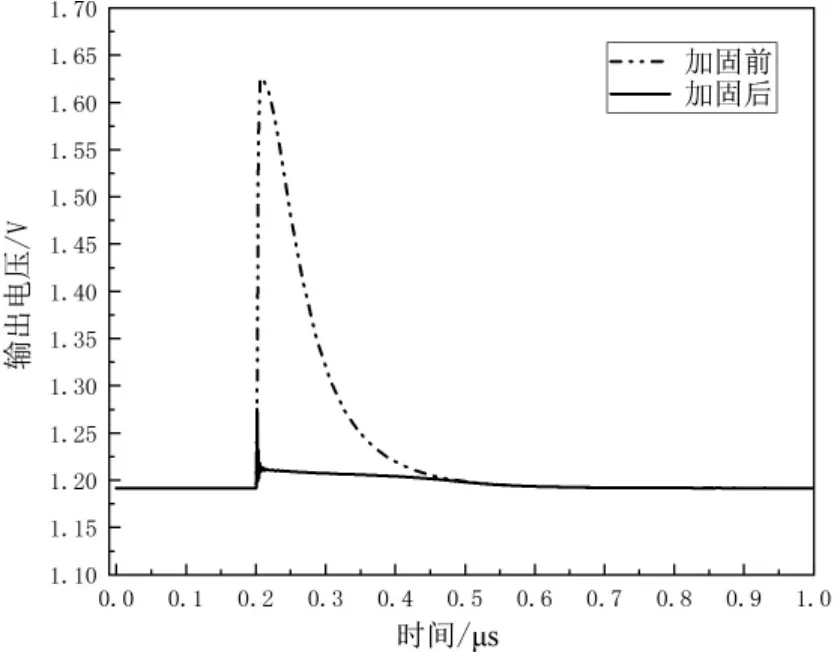

正SET 效应的仿真波形如图6 所示。根据双指数电流方向的不同,当未加固的电路发生SET 效应,输出电压变化,由原来的1.19 V 升高至1.64 V,受沉积电荷的影响,电路的输出电压与未受SET 影响相比升高约0.45V。加固后,在注入相同数值的双指数电流源后,电路的输出电压由1.19 V 升高至1.27V,与加固前的电路相比,输出电压振幅由原来的0.45V 降至0.08V,下降了约83%。由此可见比较器Q1及N0管的存在有效地抑制了正SET 效应所带来的影响。

图6 正SET 效应仿真波形

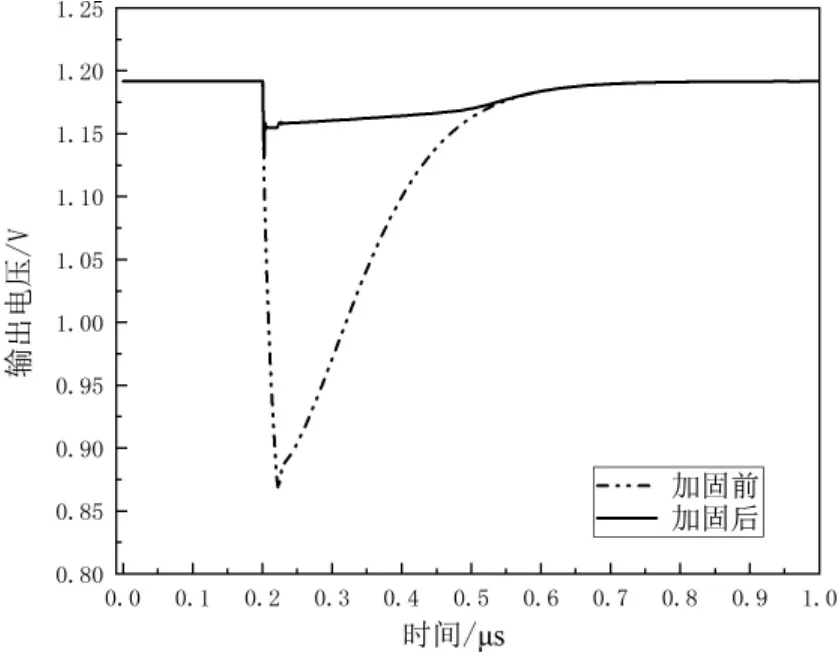

当电路受到另一方向瞬态电流源的影响时,仿真得到负SET 效应仿真波形,如图7 所示。对于未进行SET 加固的带隙基准电路,其输出电压受到双指数电流脉冲影响,从1.19V 下降至0.86V,峰值电压下降约0.33V,对于加固后的电路,输出电压下降至1.14V,与加固前相比,其振幅下降了约85%。由此可见比较器Q2及其输出端连接的P0可以有效降低负SET 效应所带来的影响。

图7 负SET 效应仿真波形

3.3 电路对比及其优点

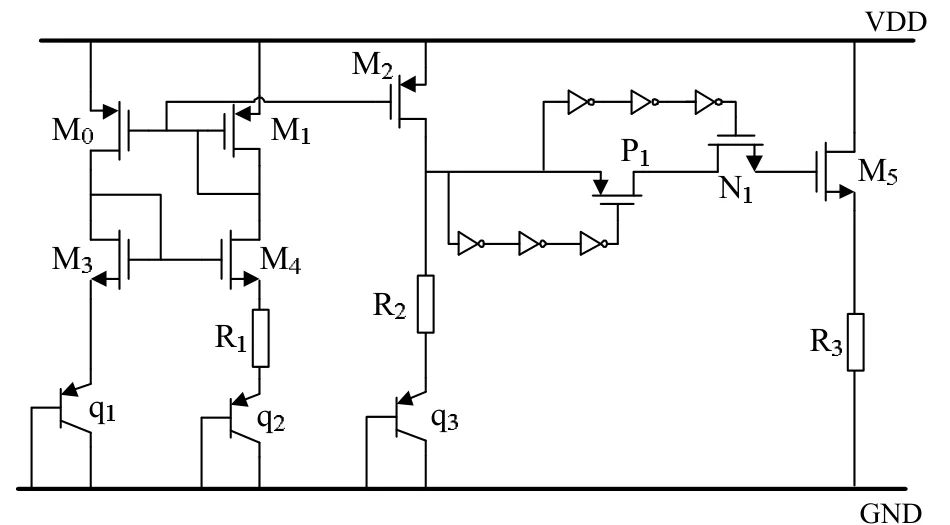

在仿真中复现文献[7]中的电路,如图8 所示。此设计利用P1管与N1管作为连接带隙基准电路输出与其负载的开关。反相器用来控制两管的开启与闭合,当电路中发生SET 效应导致电路的输出电压突然升高或降低时,P1或N1闭合以防止负载电路受到影响。原文献中所使用的制程工艺有所不同,为便于比较,在此采用同样的SMIC 180nm 工艺对其加固结构进行设计,主体电路则采用本设计的带隙基准电路(图2)。

图8 文献[7]中所用的抗SET 带隙基准电压源

采用相同激励源模拟粒子注入,结果如图9 所示。受双指数电流源影响,电路的输出电压最低下降到1.17 V,最高上升至1.27 V,与加固之前比较,电压的变化缩小了约95%和83%,抗SET 效果显著。然而当利用同样数值的双指数电流源注入P1的漏极时,其输出电压从1.19V 下降至0.86V,与正常情况相比下降29%,说明P1的漏极为敏感节点。为验证此观点,将不同尺寸的P1与N1的漏极注入相同数值的双指数电流源,仿真结果如图10 所示。

图9 复现结构仿真波形

图10 P1 漏极注入双指数电流源后的仿真波形

由图10 可知P1与N1的尺寸越大,负载电路的输入电压就越稳定;P1与N1的尺寸越小,其漏极对SET 就越敏感。当MOS 器件W=5μm 及以下时,P1及N1管的漏极在高能粒子入射后会对后部负载电路造成很大影响,为整个电路引入了新的敏感节点。

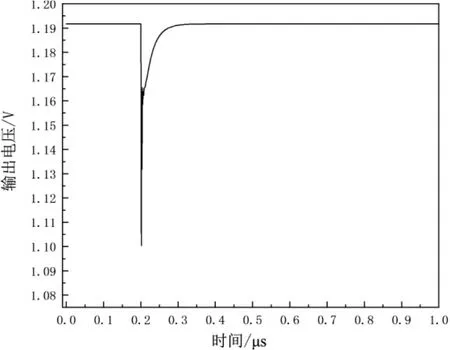

由于本设计的电路补偿电路具有对称互补的优点,所以即使N0受到SET 效应影响被错误地打开而导致输出电压降低至参考电压以下,另一端也会保持正常工作,稳定地输出电压。为了验证此优点,利用相同数值的双指数电流源对N0的漏端进行注入,所得到仿真结果波形如图11 所示。将双指数电流注入后,带隙基准电路的输出电压从1.19V 下降至1.1V 左右,振幅约为0.09 V,与复现文献中的电路相比,性能更加稳定。

图11 N0 注入双指数电流源后的仿真波形

由仿真波形可知,当N0受到SET 影响后,对带隙基准电路的输出电压影响很小,可以忽略不计。所以,对于本次设计的抗SET 带隙基准电路,即使其抗SET 结构受到高能粒子轰击导致其输出电压降低,电路通过其结构特性也可以有效地降低SET 效应对电路的影响。

4 结束语

随着器件特征尺寸的不断缩小,SET 对带隙基准电路输出稳定性的影响会越来越显著。由于带隙基准电压源为负载电路提供稳定电压,所以企业和科研机构对带隙基准电路抗辐照加固的研究非常重视。由于抗辐射工艺生产厂家少,加固的成本高等原因,用商用工艺进行电路级加固仍然是目前的趋势。本研究主要从电路层面进行抗SET 加固,事实证明,采用电流补偿电路,不但可以有效地抑制SET 效应,还可以避免引入新的敏感节点。目前,对于带隙基准电路的抗辐照加固没有通用的方法,但无论运用何种方式进行加固,或多或少都会对电路造成影响,对设计需求和设计开销等多方面考虑才是正确的选择。