ADC 控制器的设计方法及实现

唐 虹

(中国电子科技集团公司第四十七研究所,沈阳 110000)

1 引 言

MCU 内ADC 的控制器设计主要是完成对ADC模拟部分的控制[1-2]。控制主要包括:采样开关的产生、采样时间的设置、采样通道的选取、产生数据的处理、模拟看门狗的设计、中断的产生。通过对ADC控制器的设计便可实现对ADC 的时序控制、开关使能、通道选择等功能[3]。针对ADC 的数字部分,在此设计一种逐次比较型ADC 的控制器设计,着重介绍其设计原理和实现过程。

2 总体设计

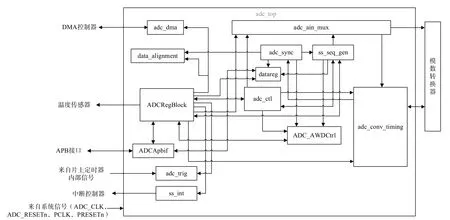

电路采用自顶向下分层次的正向设计思想[4-5],并采用模块化设计。所设计的ADC 控制器包括通道选择模块(adc_ain_mux)、DMA 传输控制模块(adc_dma)、数据对齐处理模块(data_alignment)、信号同步模块(adc_sync)、时序产生模块(ss_seq_gen)、数据寄存模块(datareg)、ADC 控制产生模块(adc_ctl)、模拟看门狗模块(ADC_AWDCTRL)、寄存器读写模块(ADCRegBlock)、总线接口模块(ADCApbif)、触发产生模块(adc_trig)以及ADC 转换时序控制模块(adc_convtimg),共计12 个模块。总体设计的原理框图如图1 所示。

图1 电路模块化结构图

3 ADC 控制产生模块设计

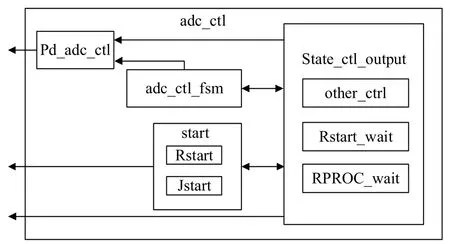

控制产生模块adc_ctl 是ADC 设计的核心部分,需要加以特别而周全的考虑。adc_ctl 模块主要由adc_ctl_fsm 和start 模块(包括Rstart 和Jstart 信号控制逻辑)以及其他的逻辑控制(包括Pd_adc_ctl 和State_ctl_output,后者又包括other_ctrl、Rstart_wait和RPROC_wait 信号控制逻辑)构成。如图2 所示是adc_ctl 模块的结构框图。

图2 adc_ctl 模块结构图

adc_ctl 模块的功能就是根据ADC 的设置,产生ADC 启动信号和掉电控制信号、采样序列控制控制信号,并且控制外部通道的转换。

adc_ctl_fsm 模块的主要功能是控制外部通道的转换。如图3 所示为ADC1 的adc_ctl_fsm 状态转换图。具体设计方法为:

图3 ADC1 的adc_ctl_fsm 状态转换图

当APB 总线复位时,ADC 处于IDLE 状态。当Rstart 信号有效,即规则触发信号有效时,ADC 将由IDLE 状态切换到RPROC 状态,进行规则通道的转换;如果在规则通道转换期间(RPROC 状态)产生外部注入触发(Jstart 有效),ADC 将由IDLE 状态切换到RST_R 状态,即当前转换被复位;ADC 紧接着由RST_R 状态切换到JPROC 状态,即注入通道序列被以单次扫描方式进行转换;当注入转换完成(Jdone&RPROC_wait)时,ADC 将由JPROC 状态切换到RST_J 状态,ADC 紧接着由RST_J 状态切换到RPROC 状态,恢复上次被中断的规则组通道转换。当ADC 非断电(~ADON),或是ADC 规则通道转换完成,并且处于非自动注入模式(~JAUTO&Rdone),ADC 将由RPROC 状态切换到IDLE 状态;如果设置了JAUTO 位,在规则组通道转换完成之后(JAUTO&Rdone),注入组通道被自动转换,即ADC状态由RPROC 状态切换到JPROC 状态。如果是持续转换,并且规则通道转换完成之后,规则通道组将从头开始进行规则通道转换。

当ADC 处于IDLE 状态之下,如果Jstart 有效,即当注入触发信号有效时,ADC 将由IDLE 状态切换到JPROC 状态,进行注入通道的转换;当JAUTO置位还设置了CONT 位,即自动注入模式并且持续转换置位,那么当注入转换完成之后,即Jdone&(CONT&JAUTO)有效,ADC 将由JPROC 状态切换到RPROC 状态,将继续规则通道的转换。当自动注入模式下持续转换置位时,规则通道至注入通道的转换序列将被连续执行。在ADC 断电(~ADON),或是ADC 注入通道转换完成,并且非“(CONT&JAUTO)||RPROC_wait||Rstart_wait”的情况下,ADC 将由JPROC状态切换到IDLE 状态。如果在注入转换期间(JPROC 状态)产生规则事件,注入转换不会被中断,但在注入序列结束后(Jdone&Rstart_wait),ADC将由JPROC 状态切换到RST_J 状态,ADC 紧接着由RST_J 状态切换到RPROC 状态,规则组通道转换被执行。即当Jdone&Rstart_wait 有效时,ADC 将由JPROC 状态切换到RST_J 状态。如果是持续转换,并且注入通道已转换完成,转换将从注入通道组开头开始注入通道转换;如果Jstart 有效或者在其他条件下ADC 保持JPROC 状态不变,即仍在执行ADC 的注入转换。

当ADC 处于RST_R 状态时,当ADC 断电(~ADON),ADC 将由RST_R 状态切换到IDLE 状态,否则RST_R 状态切换到JPROC 状态。

当ADC 处于RST_J 状态时,当ADC 断电(~ADON),ADC 将由RST_J 状态切换到IDLE 状态,否则ADC 将由RST_J 状态切换到RJPROC 状态。

当ADC 处于RST_Ralte 状态时,对于ADC1 的状态机,当ADC 断电(~ADON),ADC 将由RST_Ralte状态切换到IDLE 状态。

Start 模块主要负责产生adc_ctl_fsm 的规则通道和注入通道的启动信号Jstart 和Rstart。Rstart 信号逻辑图如图4 所示。Jstart 逻辑图与此一致。

图4 Rstart 信号逻辑图

4 功能仿真

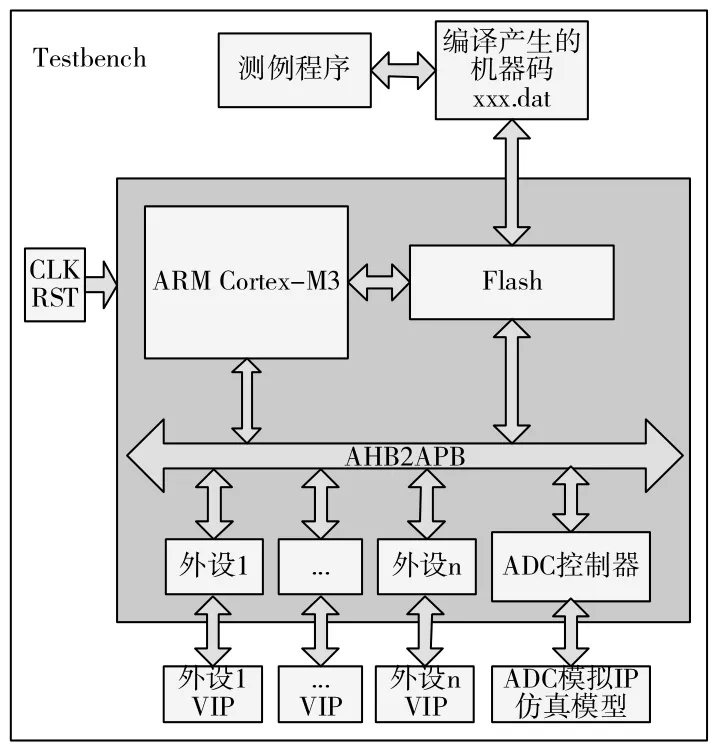

基于上述讨论,在ADC 控制器设计完成后,将其与MCU 其他模块进行系统整合,对于ADC 模拟IP,通过撰写仿真模型完成模拟与数字之间的仿真[6]。搭建仿真与验证平台进行功能仿真验证。ADC 仿真验证平台的原理框图如图5 所示,其中包括处理器内核ARM Cortex-M3、flash 存储器(用于存放测例程序),ADC 控制器设计、ADC 模拟IP 仿真模型以及平台激励信号[7-8]。

图5 ADC 控制器仿真验证平台

图6 为ADC 控制器的仿真波形图。该例程是MCU 内部两个ADC 同时工作,当有来自ADC1 的外部触发(Jtrig_r)产生,在第一个触发产生时,ADC1上的所有注入通道被转换,该程序设置为ADC1 注入通道长度为4,每次触发ADC1 完成4 个数据转换;第二个触发产生时,ADC2 上的所有注入通道被转换,该程序设置为ADC2 注入通道长度为4,每次触发ADC2 完成4 个数据。依此规律反复循环转换,即实现设计预期的功能目标。

图6 ADC 注入组触发仿真波形

5 结束语

通过本设计的研究,即可完成ADC 控制器的设计与实现,并将其集成在MCU 中,验证功能的正确性。该设计可以被广泛应用于各类MCU 的ADC 控制中,完成对ADC 的控制及数据处理,可以丰富ADC的功能,具有一定的通用性。