一种基于芯片片内总线的DMA 控制器芯片的设计与验证*

苏 兴,刘 威,2,3,4

(1.武汉大学 物理科学与技术学院,湖北 武汉 430072;2.武汉大学 微电子学院,湖北 武汉 430072;3.湖北珞珈实验室,湖北 武汉 430072;4.武汉量子技术研究院,湖北 武汉 430072)

0 引言

随着微电子领域技术的迅速发展,IC 已进入片上系统(System on Chip),即SoC 时代。片内总线(Internal Chip Bus)作为IC 系统的连接部件,用于把各个模块联系起来,从而解决整个集成电路内部间的互相通信问题[1]。

在现有的众多片内总线中,由ARM 公司研发推出的一种高级微控制器总线架构AMBA (Advanced Microcontroller Bus Architecture)因自身特点深受研究人员和市场开发商的喜爱。在AMBA3.0 版本中,定义4 种接口类型[2],其中AHB 总线因自身兼容性强、扩展性高,设计简单等优势而广泛用于各类高级系统结构中[3],AXI 总线规范主要描述了IP 核之间的信息交互[4]。

为了结合AXI 总线和AHB 总线各自优点,得到一种具有高速性及易用性的总线协议,市场上又出现了一种新的自定义片内总线协议ICB(Internal Chip Bus)。ICB 总线结构如图1 所示。它具有如下特性:更加简单的协议控制,两个独立通道,读写操作共用的地址通道,共用结果返回通道;同时,与AXI 总线一样,采用分离的地址阶段和数据阶段;采用地址区间寻址,支持任意主从数目拓扑结构。每个读写操作都会在地址通道上产生地址,而不是像AXI 总线只产生起始地址;协议非常简单,易于转换成其他总线,譬如AXI、AHB、APB 等。

图1 ICB 总线结构

1 DMA

1.1 DMA 概念

DMA(Direct Memory Access,直接存储器访问)是一种完全由硬件执行输入/输出数据交换的方式,外部设备直接对计算机存储器进行读操作,而不需要经过CPU(处理器)。这种传输方式,取消了中间媒介的延迟,可以直接在目的地址和源地址直接完成传输,大大提高了传输效率[6]。

在进行数据传输时,芯片作为主设备完成所有操作,从而减轻了处理单元负担。此外,DMA 传输支持块传输和散/聚传输,以分别处理连续内存映射地址和非连续内存地址(非连续内存地址映射下,通过指针寄存器完成),可提高使用效率。

1.2 DMA 配置

DMA 使用模式寄存器设置DMA 传输[7]。

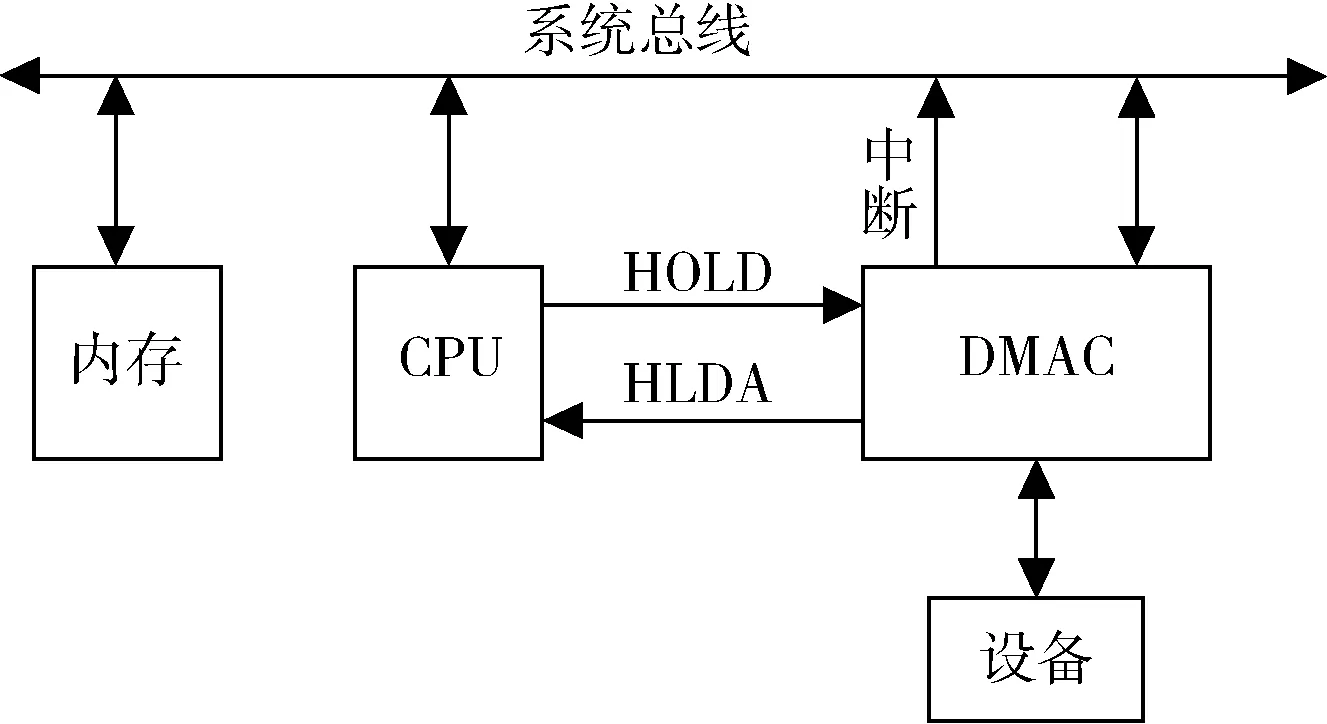

典型的DMA 传输过程如图2 所示。DMAC(DMA Controller,DMA 控制器)向CPU 发送DMA 总线控制请求信号HOLD,一旦DMAC 收到HLDA 响应信号,DMAC 将代替CPU 进行总线控制,全权负责内存和外设之间的数据传输,CPU 从中释放出来,待完成数据传输或发生错误后,DMA 向CPU 发起一个中断信号,归还总线控制权到CPU,整个传输过程结束。DMA 引擎的作用是控制数据搬移,涉及读和写两种操作[8],通常在一个DMA 引擎里同时实现了这两种功能,在进行数据传输时,先读后写,整个过程都在一个系统中实现。

图2 DMA 传输过程

总结DMA 配置过程:(1)确定传输数据的外设、寄存器地址和确定传输方向;(2)确定每次传输的数据量值和传输数据的字节数;(3)配置通道优先级;(4)确定传输是循环模式还是非循环模式以及如若需要开启中断,则开启响应位中断。

1.3 DMA 应用

DMA 技术因自身特点可以适合应用在高速高数据量传输中,多见于图像处理、数据采集等应用[9]。

随着移动互联网和云计算发展,基于嵌入式系统的智能移动设备也越来越多,如何快速有效地发送接收和处理设备收集的数据,是系统开发者需要思考的难题。基于DMA,可以实现串口数据的发送和接收,这样,有利于降低对MCU(Micro Control Unit 微处理器)的占用,提高数据处理的效率[10]。

DMA 同时也广泛应用于PCIE 总线上,PCIE 总线由于其大吞吐量和支持DMA 的特性,适用于雷达领域,因此需要高速的数据传输系统和高速的数据采集系统。实际通信中,数据由光纤传入FPGA 中,CPU 再将数据的处理结果发送。在这个过程中,CPU 实际只需要给FPGA 发送一次启动DMA 的命令,之后每次DMA 传输的流程就可以由数据源端发起,减少了CPU 与FPGA 的反复交互[11]。

为了满足近年来机器视觉、无人驾驶等智能识别技术领域的发展,图像处理技术的要求越来越高,DMA2D控制器应运而生。使用DMA2D 控制器,即通过DMA 连接显示器引脚或存储控制器引脚将像素数据传输到液晶屏,从而加快显示每帧图像在屏幕上的显示速度,也可以通过配置实现部分显示,如只刷新图像的部分内容。由于帧频率越高动画越流畅,因此提升DMA 的传输速度,有利于显示效果的提高[12]。

2 配置与验证

2.1 设计思路

ICB 总线总的可以分为命令通道和响应通道,主机通过ICB 总线向从机发送命令,从机通过ICB 总线响应主机,如图3 所示。

图3 ICB 通道传输

ICB 通道与信号如表1 所示,ICB 的读写有两次握手,一次是主机发起读写请求,然后从机响应。另一次是从机发起读写反馈请求,主机响应。两次握手结束也就意味着完成一次读写。

表1 ICB 通道与信号

2.2 RTL 代码分析

2.2.1 寄存器配置ICB 时序

(1)dma_cfg_icb_cmd_ready(DMA 配 置ICB 总线命令准备寄存器):如果是读寄存器的值,则需要等待rsp_valid 信号为0 时才能读,此时表示没有对寄存器进行写值;如果是写寄存器的值,当dma_cfg_icb_cmd_valid 信号产生时则立即将ready 拉高。

(2)dma_cfg_icb_rsp_valid(DMA 配 置ICB 总线响应有效寄存器):当cmd 命令信号握手后,表明写或者读寄存器值正常,则可以在下一个周期将该信号拉高,直到与rsp 响应信号握手,将这个值拉低。

(3)dma_cfg_icb_rsp_rdata(DMA 配 置ICB 总线响应读数据寄存器):可以利用组合逻辑实现,但本次模块中采用握手后的下一个周期读出寄存器的值。并且当rsp_valid 信号没有拉低时,rdata 的值需要一直保持,握手成功后根据寄存器地址进行赋值。

(4)dma_icb_cmd_addr(DMA_ICB 命令地址寄存器):为组合逻辑,当cmd 握手后,如果为读状态,则地址变为s_reg 寄存地址加上偏移量;如果为写状态,则为d_reg 中的地址加偏移量。其中偏移量用发出的读或者写命令的次数代替。

2.2.2 FIFO 模块

(1)读与写地址:初始地址都为0,当空的时候无法进行读操作,满的时候无法进行写操作。

(2)空、满与溢出信号:当地址的低5 位相同,并且最高位不同时,则表示FIFO 已经满了,当读写指针所有位都相同时,则表示FIFO 为空。溢出信号是当FIFO 满的时候,还要继续写进数据时指示的信号,所以可以利用时序逻辑。

(3)读数据与写数据:读数据与写数据根据读写使能信号以及空满信号,将指针对应的数据读出或者写入。

(4)sub_full 即满信号:由于时序逻辑的延迟,导致状态机在判断下一个状态时要提前知道FIFO 是否满了,由于FIFO 的full 信号比next_state 信号晚两个周期,因此需要一个sub_full 信号来指示FIFO 是否即将满了。

2.2.3 DMA 的数据传输

在传输阶段,DMA 主要有三个状态:初始状态,读SRAM 状态,写SRAM 状态。初始状态:表示DMA 还未开始传输。读SRAM 状态:当DMA 使能信号为0 时,其下一状态为初始状态。当FIFO 还没有满,并且读的数据数目还没有达到要求的数目,下一状态继续读;否则下一个状态为写。写SRAM 状态:当DMA 使能信号为0时,其下一状态为初始状态。当FIFO 还未空,并且写的数据数目没有达到要求的数目,下一个状态继续写。如果读的数据还没读完,则下一个状态变为读。否则下一个状态变为初始状态。

2.2.4 ICB 访存时序

图4、图5 所示是通过ICB 读写的时序。

图4 写时序

图5 读时序

2.3 DMA 配置过程

DMA 配置模块主要由ICB slave 接口和配置寄存器堆组成。

ICB slave 接口:DMA 在配置时需要以从设备的角度完成ICB 时序通信。输入信号直接和CPU 发来的信号相连即可。主要考虑输出的信号。

s_icb_cmd_ready 信号:可以根据DMA 可能出现的状况判定,最简单的方法就是令其等于s_icb_cmd_valid信号,也就是认为DMA 总是准备好的。这需要在编写配置模块时确保不会出现意外状况导致停顿。s_icb_rsp_valid 信号可以设置成每次cmd 握手后拉高,在rsp 握手后拉低。s_icb_rsp_rdata 则需要根据输入地址选择对应的寄存器值。

寄存器堆:DMA 工作需要配置如源地址寄存器、目的地址寄存器、搬运长度寄存器、状态寄存器等一系列寄存器。它们需要有固定的偏移地址,从而可以被s_cmd_addr 地址信号确定位置以访问。

3 结论

本文设计了一个基于ICB 协议的DMA 控制器,利用EDA 工具完成仿真验证,并改善了部分代码以提升代码质量,最终DMA 控制器功能行使正确,符合设计目标。在整个设计过程中,主要完成的工作内容如下:

(1)研究并总结相关协议以及 DMA 传输原理,基于AMBA 总线架构提出DMA 控制器设计方案,完成方案的制定。

(2)详细分析了DMA 控制器的具体功能,依据功能划分模块,借助硬件编程语言Verilog 编写代码,实现模块划分功能。

(3)完成DMA 控制器的前端功能仿真验证。结果符合传输要求,子模块功能正常行使,符合设计需求。

本次设计的DMA 控制器实现了预期功能需求,但功能较为简单单一,还无法满足其他需求,经过考虑,可以在尝试从以下几个方面入手改进:(1)接入其他总线,从而得到通用方向的DMA 控制器;(2)提高内部通道数量,通道数目越多,则控制器一次可响应的请求越多,现在的市场环境,多种外设集成是大势所趋,提升兼容性,可以很好地实现系统传输效率的提升。