适用于智能变电站混合数据源接入的保护同步采样方法

刘益青,高伟聪,高厚磊,王林先

(1.济南大学 自动化与电气工程学院,山东 济南 250022;2.山东外事翻译职业学院 经管学院,山东 济南 250100;3.山东大学 电气工程学院,山东 济南 250061;4.积成电子股份有限公司 厂站部,山东 济南 250100)

0 引言

智能变电站采用电子式互感器时,采样值SV(Sampled Value)以点对点直连方式传输,以避免外部全局时钟影响继电保护的可靠性。单纯采用电磁式互感器时,其二次输出直接接入模拟量采集合并单元MU(Merging Unit)实现就地数字化采样。合并单元采用点对点方式传输时,数据处理、传输和等待的延时固定[1-2],可以与电子式互感器直接SV接入时采用相同的插值方法完成采样数据同步和采样率变换[3-4]。

但在智能变电站建设实践中,往往会遇到保护装置需要同时接入SV和电磁式互感器等多种类型数据源的情况,通常的解决方案是增加模拟量输入合并单元,将全部输入量统一为SV,但该方案存在增加设备和投资的缺点。在智能化保护装置中实现多路SV的点对点插值同步方法已经比较成熟[5],基于此方法,本文设计了一种适应同时接入不同类型数据信号的保护同步采样方法,该方法借鉴传统微机保护实现模拟量采集的技术,对全数字保护现有的插值同步模块稍加改造即可实现,既适用于智能变电站的保护设备,还可应用于级联合并单元的设计。

1 智能变电站保护数据采集与传输

1.1 智能变电站数字化保护的数据源类型

智能变电站中采用了电子式互感器,相比传统的电磁式互感器,具有绝缘简单、动态范围宽、无磁饱和等优点,在高电压等级电网中具有很好的技术经济性。而在中低电压电网中,由于绝缘问题不突出,电子式互感器的经济性优势不明显,运行可靠性也亟待提高。同时,常规的电磁式互感器具有相当成熟的运行经验,并且保护装置对其磁饱和特性有了有效的应对措施。因此,在中低电压电网中,仍倾向于保留电磁式互感器的方案,采用模拟量采集的合并单元实现数字化采集,然后通过光纤实现数字化传输。这种方案有较好的兼容性,既利用了光纤传输的抗干扰性和可靠性,又可减少互感器二次接线数量,节约投资。

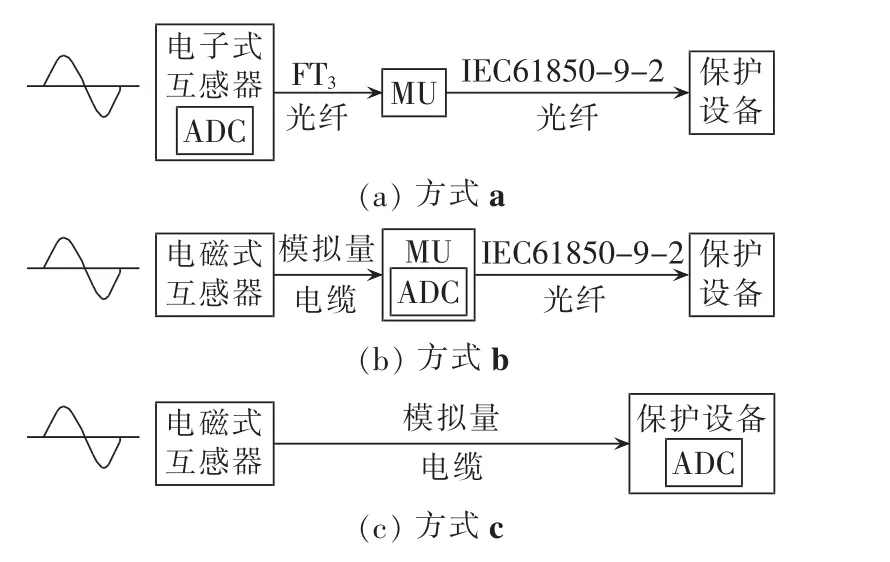

从实际应用看,目前智能变电站中的继电保护设备数据源存在以下3种类型,如图1所示。

a.电子式互感器就地数字化后,通过合并单元以IEC61850-9-2帧格式[6]接入保护装置。

b.电磁式互感器通过合并单元进行AD转换后,通过光纤接入保护装置。

c.电磁式互感器以电缆直接接入保护装置。

图1 智能变电站继电保护数据源分类Fig.1 Three data source types of smart substation protections

1.2 智能变电站混合数据源接入的应用场合

正是由于智能变电站的继电保护系统存在上述不同的数据源接入形式,就必然要适应同时接入电磁式互感器模拟量和SV数字量的情况。下面列举几个可能的实际应用场合。

a.变压器各侧不同电压等级使用不同类型的电流互感器[7],例如高压侧采用电子式互感器、中低压侧采用电磁式互感器,如图2(a)所示。

b.变压器低压侧的备用电源自投装置[8],主变低压侧电流从合并单元接入,需要同时完成分段保护,并且分段电流为电磁式互感器模拟量接入的情况,如图2(b)所示。

c.智能变电站10 kV低压馈线间隔通常采用电磁式互感器,在母线电压合并单元采集时,馈线保护需要同时接入电磁式电流互感器和电压合并单元的电压SV输出。

d.常规变电站在进行智能化改造过程中,母线保护改造完成间隔为电子式互感器、合并单元接入,未改造间隔仍为电磁式互感器接入[9-10]。

图2 智能变电站混合数据源接入的典型应用Fig.2 Typical applications of hybrid datasource types in smart substation

2 混合数据源的保护同步采样方法

2.1 插值同步的实用算法

通过数据插值的方法实现多间隔保护数据的同步是目前智能变电站主保护的基本技术方案。实现插值同步的根本前提是从采集设备对一次电流、电压进行数字化采样的时刻到保护装置接收到采样值的时刻之间的延时固定不变。通过保护装置与采集设备(主要是合并单元)之间采用点对点的直连光纤链路可以保证上述延时不变。这样,保护装置可依据SV的接收时刻推知一次原始数据的采集时刻,进而在不同SV输入之间实现一次原始数据侧的同步采样[11]。

实用化的插值同步方案在具体实现时还要解决以下关键技术问题。

a.插值时刻基准的选择。

采用插值算法实现多路数据的同步采样,需要确定统一的插值时刻,即确定将各路数据同步到哪个时刻上。插值时刻的选取方法有固定通道法、第一时间到达法和指定插值时刻法3种[12]。本文采用指定插值时刻法,并通过实时测频调整插值时刻实现同步采样。

b.帧接收时刻的精确标定。

采用数据插值的方法实现数据同步需要3个条件:合并单元的发送间隔抖动足够小;数据传输链路延时固定;数据帧接收时刻精确标定。第1个条件由合并单元设计保证,采用现场可编程门阵列(FPGA)实现时通常可以做到时间抖动小于4 μs[13];第2个条件在采用点对点直连时可以满足;第3个条件需要由SV的接收者保证,通常由FPGA实现,在介质访问控制(MAC)层数据解帧时进行硬件时间戳精确定标。

c.插值数值算法的选择。

常用的插值数值算法主要包括线性插值、二次插值和三次样条插值[14]等,在实际应用中选择何种插值算法主要从计算量和插值精度2个方面权衡。线性插值可满足大多数继电保护的应用要求,只是在高次谐波含量较高的场合,三次样条插值的计算精度有一定优势[15]。然而无论采用哪种插值算法,均不影响本文的保护数据同步采样方法的原理,因此不作进一步的详细讨论。

2.2 保护设备只接入SV的同步采样方法

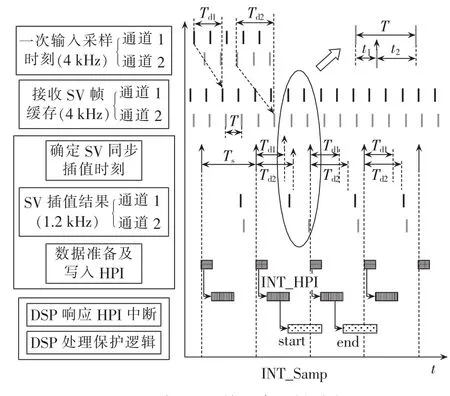

智能变电站的保护装置如果只接入SV数字量,且采用点对点的光纤直连方式时,可直接采用数据插值的方法实现同步采样。具体的同步插值时序如图3所示。

图3 只输入SV的同步采样时序图Fig.3 Synchronous sampling sequence for SV input only

2路SV的额定延时分别为Td1和Td2,依据该额定延时和SV帧接收时刻,可推知SV对应的一次输入采样时刻。保护装置再根据采样间隔Ts,确定插值脉冲的时刻,并将插值脉冲对应的时刻,分别对2路SV推算到一次侧时刻。该时刻往往不会恰好有SV,此时可通过数据插值运算获得所需SV。通过上述处理,对于保护装置而言,多路SV数据在保护采样脉冲时刻实现了同步采样。

如果保护装置仅接入SV数字量,采样脉冲的时刻可以按照前述3种选择方式任意选择,因为此时同步的目的仅仅是将多路SV数据还原到一次侧的同一时刻即可。不同的采样脉冲基准不影响插值结果的同步性,只是会造成后续保护逻辑处理的延时不同。

2.3 电磁式互感器与SV同时接入的同步采样方法

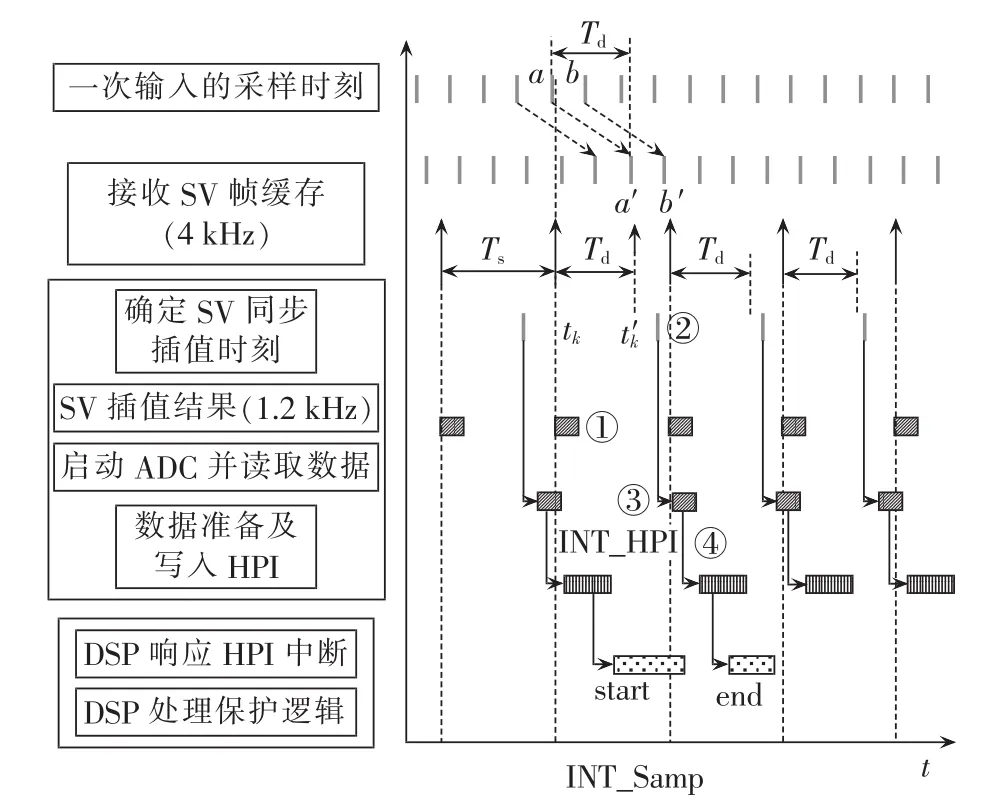

当保护装置同时有电磁式互感器的模拟量输入和SV数字量输入时,仍然可以用数据插值的方法实现同步采样,但是采样脉冲基准的选择必须遵循:SV数字量反映的一次输入与电磁式互感器反映的一次输入严格同时。以此为根本要求,设计了完全基于采样脉冲实现的多类型数据源接入时的同步采样方案,处理时序如图4所示。

图4 同时接入模拟量和SV的同步采样时序图Fig.4 Synchronous sampling sequence for analog and SV inputs

图4中第一行的采样序列对应电子式互感器一次输入的采样时刻,SV可以由电子式互感器的前端采集模块就地数字化得到,也可以由模拟量输入的合并单元获得。以相邻2次采样的a帧、b帧SV数据为例,经过额定延时Td(包括采集器延时、合并单元处理延时和链路传输延时)后,保护装置接收到这2帧SV数据帧并存入数据缓存区,为区别不同时标,标记为 a′帧和 b′帧。

每间隔Ts时间(插值结果选为1.2 kHz时,Ts≈833 μs),由定时器产生一个采样脉冲,该时刻记为tk。采样脉冲有以下2个作用。

a.在tk时刻启动保护装置内部的AD转换器(ADC),进行AD转换,并读取AD转换结果,实现模拟量接入通道的定时采样,如图4中步骤①所示。

b.确定SV插值同步时刻的基准,如图4中步骤②所示。tk对应的一次输入时刻在a、b 2帧之间,因此只要获得tk对应的SV,即可实现SV数据与保护装置直接采集的模拟量之间的同步采样。

由于在tk时刻保护装置尚未接收到a、b这2帧数据,因此还无法得到与模拟量同步的SV。在延时Td之后(等效于将采样脉冲延迟Td时间到t′k),保护装置接收到a′和b′这2帧SV数据,即可作为插值计算数据源,得到t′k时刻的插值结果,也就得到了一次输入tk时刻的SV,显然该值与直接输入保护装置的模拟量采集为同一时刻的SV。

步骤②完成之后,SV通道、模拟量通道各自对应一次输入tk时刻的同步采样值就已经全部得到。处理时序中的步骤③将步骤①和步骤②中各自获得的SV进行数据组帧并写入数字信号处理器(DSP)的 HPI(Host Port Interface)缓存,然后触发HPI中断(步骤④),通知DSP读取已经同步好的保护数据,DSP按预定节奏进行保护计算和逻辑判断。

从图4的同步采样时序可以看出,保护装置要得到tk时刻的同步采样值,最长需要等待Td+T的延时,其中T为插值算法导致的最大延时,即4 kHz下的采样间隔(参见图3)。同时,触发DSP的HPI中断也会存在最大T时间的抖动。这种时序处理略显复杂,但可以最大限度地缩短保护数据处理延时,提高保护的速动性。并且对常规微机保护中定时响应采样中断的处理时序改变也不大,有利于提高软件继承性和可靠性。这一点也是与图3所示的全部为SV输入时的处理时序不同的地方,图3所示处理方式,HPI中断的时间间隔是均匀的,因此也可用于合并单元的插值同步。

合并单元要求的是输出抖动足够小,保护装置则要求速动性,因此本方案在应用于保护装置或合并单元时,由于考虑的主要因素不同,处理时需要区别对待。合并单元为了保证发送数据抖动尽量小,通过插入等待时间,始终保持同步SV的发送延时固定为 kTs(k=1,2,…),k 依据 Td+T 的大小取值,例如当Ts<Td+T<2Ts时取 k=2,通常合并单元的 Ts仍保持4 kHz。

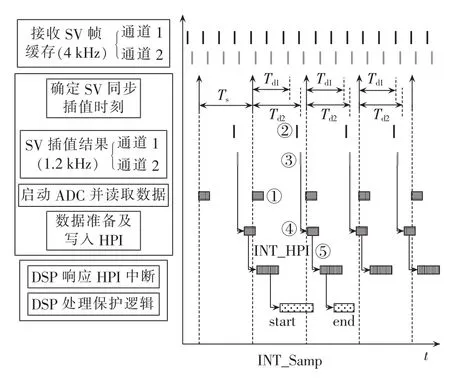

更一般的情况是,保护装置需要同时接入多路SV数据,下面以同时接入模拟量和2路SV的情况为例说明,处理时序如图5所示。

2路SV的额定延时分别为Td1和Td2。图5中,步骤①完成模拟量AD转换;步骤②和③分别获取2路SV的同步SV,对应时刻分别为2路SV同步插值运算完成后的数据可用时刻,其抖动不影响采样脉冲决定的插值时刻的准确性;步骤④完成步骤准备,汇总步骤①、②、③中数据;步骤⑤触发HPI中断完成数据传输。与只接入1路SV数据相比不同之处在于保护装置得到同一时刻SV的最长等待延时为 max{Td1,Td2}+T,其中 T 仍为插值算法导致的最大延时。同理可推知n路SV接入时,最长延时为max{Td1,Td2,…,Tdn}+T。

图5 接入模拟量和多路SV的同步采样时序图Fig.5 Synchronous sampling sequence for analog and multi-channel SV inputs

3 实现方案及验证

3.1 FPGA实现方案

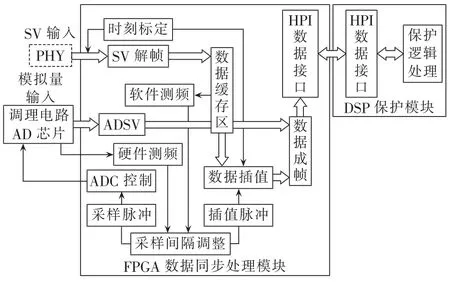

采用Xilinx公司的Spartan-6系列FPGA芯片和TI公司的浮点DSP主处理器为核心器件,实现本文所述的保护同步采样方案,如图6所示。

图6 采用FPGA实现同步采样方案的框图Fig.6 Block diagram of FPGA-based synchronous sampling scheme

由于FPGA具有并行处理能力,可以保证延时固定,适用于高速数据处理应用,因此采用FPGA作为数据处理模块,采用DSP完成保护计算和逻辑处理。二者之间通过DSP芯片的HPI进行数据交换。

不同数据源的保护同步采样功能主要由FPGA模块完成,按完成的功能可以划分为数据处理部分和信号控制部分。

数据处理部分主要完成以下工作:对接收的IEC 61850-9-2格式的SV数据帧按照ASN.1编码规则进行解帧处理;读取ADC的模数转换结果,并存入数据缓存区;进行插值运算,获取与模拟量AD转换时刻同步的多路SV数据SV;对已同步的不同来源数据进行汇总、成帧并写入HPI缓冲区。

信号控制部分主要完成以下工作:在MAC层对接收的SV数据帧标定硬件时间戳;实时计算输入信号频率,包括硬件测频和软件测频(3.2节详述);根据实时频率调整采样间隔Ts;通过采样脉冲控制ADC,启动AD转换;根据采样脉冲时刻、额定延时和SV数据接收时标,生成同步插值脉冲,控制插值时刻,启动数据插值运算;数据准备完毕后通知DSP,触发HPI中断。

3.2 信号频率跟踪与采样间隔调整

传统微机保护,为了减少频谱泄漏,通常采用频率跟踪技术,通过实时调整采样间隔以保证采样频率为被采集信号频率的整数倍,即实现同步采样。智能变电站中的合并单元按照固定采样率进行数字化采样,通常不会跟踪信号频率和调整采样间隔,为此保护装置需要对数据进行专门预处理或者对傅里叶变换计算结果进行修正[16]。

为实现保护插值数据的严格同步采样,以继承常规微机保护的成熟保护算法,本文设计方案需要对输入信号进行频率采集。根据实时频率,调整采样间隔(即图4中Ts)。采样间隔确定后,一方面通过FPGA中ADC控制逻辑调整采样脉冲时刻,发给AD芯片的启动转换信号;另一方面通过额定延时和SV帧接收时刻确定保护数据插值时刻。

频率跟踪的对象可以选择是电磁式互感器的模拟量输入或SV输入。对模拟量输入进行测频采用硬件调理电路实现,利用施密特触发器将正弦波整形为方波,通过检测方波周期实现频率测量。对于SV输入通道,即要求实现对等时间间隔的4 kHz采样数据进行软件测频,本文采用过零检测算法配合低通滤波器实现。

3.3 SV品质因数的处理

IEC61850标准对采用数字化传输SV定义了品质因数q,用于反映SV的数据是否有效、是否同步等属性,以便数据使用者正确处理各种异常情况。在本文设计的保护同步采样方案中,对品质因数中的“有效位”、“检修位”进行了相应处理,而且可以反映SV数据的“双路AD差异过大”品质属性。处理原则如下。

a.对于模拟量接入通道。根据AD采集回路的自检结果置数据“有效位”;根据保护装置的检修状态置“检修位”,由于采集回路在保护装置内部,因此不会出现检修不一致的状态;当模拟量采集通道数量冗余时,采用双AD并行转换模式,比较双AD的转换结果,相应地置“双路AD差异过大”标志。

b.对于SV接入通道。由于要从4 kHz的原始采样数据降频插值成1.2 kHz的同步采样数据,所以插值运算可能只用到插值时刻前后的数帧SV数据(例如线性插值只用前后2帧)。因此插值结果的“有效位”,根据插值所使用的SV数据“有效位”生成,只要使用到的原始SV数据帧中有1帧为“无效”数据,则插值结果为“无效”。未使用的SV数据出现“无效”,不影响插值结果数据的“有效位”,只给出告警信息。同理,插值结果的“检修位”根据插值所使用的SV数据“检修位”生成。如果出现插值所使用的前后2帧SV数据“检修位”不同的情况,则维持上次插值结果状态,并置本次插值结果数据“无效”。对于订阅的双AD数据,对插值之后的结果进行双AD差异过大判断,并置相应标志。

除了对品质因数进行实时处理外,还须对SV数据异常情况进行检测和处理。若仅1帧丢失则进行纠错,不影响数据同步结果;若发生多帧连续丢失,则直接补空帧,置数据品质为无效。

在FPGA数据处理模块中,不管是模拟量接入还是SV接入,均记录每一个采样点的品质状态,并通过HPI与SV数据一起传送给保护模块,由保护模块根据具体情况进行告警或保护闭锁,以提高数字化保护的可靠性和适应性。

3.4 实现方案的有效性验证

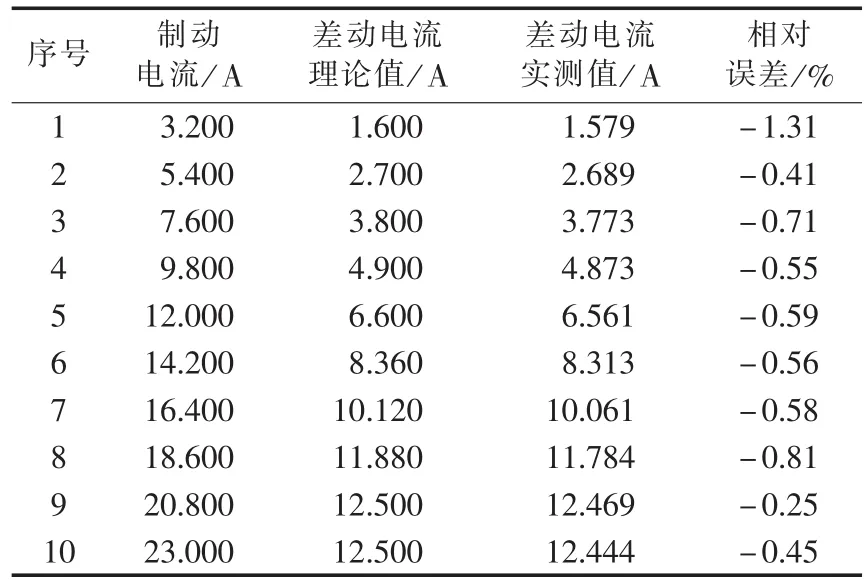

对采用本方案的某型号变压器保护装置分别进行静态实验和RTDS动模实验进行验证。静态实验中高压侧电流为合并单元输出的SV接入,低压侧电流为模拟量直接接入。实验设备采用博电PW366保护测试仪及积成电子研制的SAU型合并单元,表1为比率差动保护动作精度测试结果。

表1 比率差动保护动作精度测试结果Table 1 Results of operational accuracy test for proportional differential protection

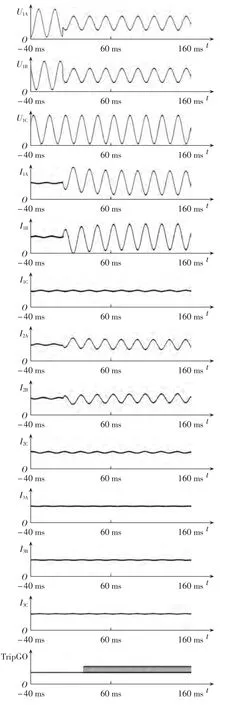

在开普实验室的三绕组变压器模型上进行RTDS实验,高、中压侧电流通过合并单元接入保护装置,低压侧电流由功放直接接入保护装置。图7为区内AB相金属性故障时录波图,TripGO接点为智能终端的硬接点开出信号。

图7 RTDS动模录波图Fig.7 Recorded waveform of RTDS dynamic simulation

通过上述测试数据和录波图可以看出,采用本方案的变压器保护装置,在同时接入多种数据源时动作误差远小于±2.5%国标要求;区内金属性故障时比率差动保护的GOOSE出口时间在25 ms左右。主要指标等均超过国标、行标的要求,表明本文设计方案在混合数据源接入情况下具有较高的采集精度和较小的时延。

为验证在SV采样异常情况下本文方案的适应性,利用博电PNF800数字式测试仪的SV异常模拟模块进行测试。在丢帧、抖动、飞点及数据无效等异常情况下,保护均能可靠闭锁,表明本方案有较强的适应性。

4 总结及展望

为了适应智能变电站同时存在多种类型的保护数据源接入等实际情况,研究了保护装置实现SV数字量和电磁式互感器模拟量同时接入方式下的同步采样方法。采用高性能的FPGA和浮点DSP为主处理器件,实现了设计方案,成功应用于变压器差动保护和备用电源自投等智能变电站保护控制设备,并已投入现场运行。该设计方案除了可以应用于保护设备外,对于有类似需求的级联合并单元、模拟量采集合并单元的设计都有一定的借鉴意义。

进一步地展望,该方法在保护设备中应用后,可以使数据应用者不必关心是电磁式互感器还是合并单元接入,并可实现装置内部点对点的高速数据传输,有利于提升智能变电站二次设备的软硬件平台的通用化和模块化。

致 谢

积成电子股份有限公司厂站部工程师林伟、王秀广、李波在方案研究及实验验证过程中给予了大力支持和帮助,开普实验室提供了故障录波图,在此致以诚挚感谢!