一种基于FPGA的硬件防火墙设计

唐泽坤+王修刚+宋伟+于珊珊+刘超

摘 要:本文提出了一种基于FPGA的硬件防火墙的实现方案,采用FPGA来实现百兆线速以上的防火墙设计。网络数据在建立连接跟踪后,由FPGA实现的快速处理板直接转发,实现了网络数据的线速处理,通用CPU在操作系统支持下,完成网络数据连接跟踪的创建、维护以及对网络规则表的维护等工作。

关键词:防火墙;FPGA;Verilog HDL;CPU

一、引言

防火墙是一种基本的网络防护设备。它是一种设置在内部网和外部网之间的安全网关,通过安全策略和规则来控制外部用户对内部资源的访问,使外部网和内部网之间既保持连通性,又根据规则间接交换信息。防火墙所采用的硬件设备必须满足网络处理性能的需求。在早期网络中,数据速率相对较低,协议也比较简单,因此网络设备通常以通用处理器配合分組处理软件实现。然而,随着数据速率的不断提高和协议的日益复杂,通用处理器处理能力的增长逐渐落后于数据速率的增长,因此,基于通用处理器平台的网络产品开发者遇到了性能上的障碍。

本文针对目前防火墙的设计方式提出了一种基于FPGA的硬件防火墙的实现方案,采用FPGA来实现百兆线速以上的防火墙设计。传统的基于x86等通用CPU的防火墙无法适应当前快速增长的网络速度,无法实现线速过滤与转发。本文采用FPGA结合通用CPU模式,可以快速处理网络数据,能够避免NP的不足。网络数据在建立连接跟踪后,由FPGA实现的快速处理板直接转发,实现了网络数据的线速处理。通用CPU在操作系统支持下,完成网络数据连接跟踪的创建、维护以及对网络规则表(端口黑名单、IP黑名单、端口白名单)的维护等工作。FPGA硬件板和CPU各司其职,实现快速转发的目的。实践证明,这是一种兼容性比较好的网络安全架构。

二、系统整体设计方案

硬件防火墙分为两个数据通道,FPGA硬件板承担网络数据的按规则高速收发与转发,并按指定规则要求通过PCI-E将数据上传至x86CPU;x86主控板承担慢速通道工作。

防火墙软件系统根据TCP、UDP、ICMP协议实现不同的连接跟踪、跟踪表项的匹配、跟踪表的动态维护;x86上防火墙软件系统通过硬件驱动程序和FPGA硬件板进行通讯。

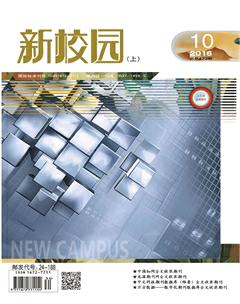

图1中所示为FPGA系统设计过程中网络抓包实验中所形成的硬件架构图。FPGA网络抓包的数据可以通过串口发送至上位机,实验可以清晰判断当前网络收发架构设计是否合理,能否准确地收发100Mbps的网络数据。

在实现了基本的数据收发后,确定防火墙系统整体架构和功能模块,如图2所示。

可以看出在这里主要由网络接口、网络控制、MAC、外网处理模块、PC处理模块、PCI-E与DDR控制模块几大部分构成。

三、系统HDL设计方案

系统使用Verilog HDL语言完成设计。下面介绍一些主要模块设计。

1.外网控制

本模块的主要功能如图3所示:

(1)存储接收到的外网报文;

(2)对接收到的外网报文进行关键字提取和识别;

(3)对提取的结果根据用户配置进行过滤;

(4)读取存储的本帧数据,根据本帧过滤的结果对其进行打包处理。

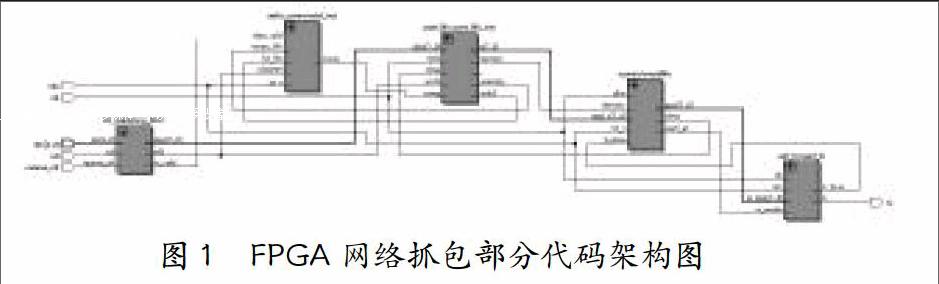

本模块时序图设计如图4所示。

2.子模块报文缓存功能设计

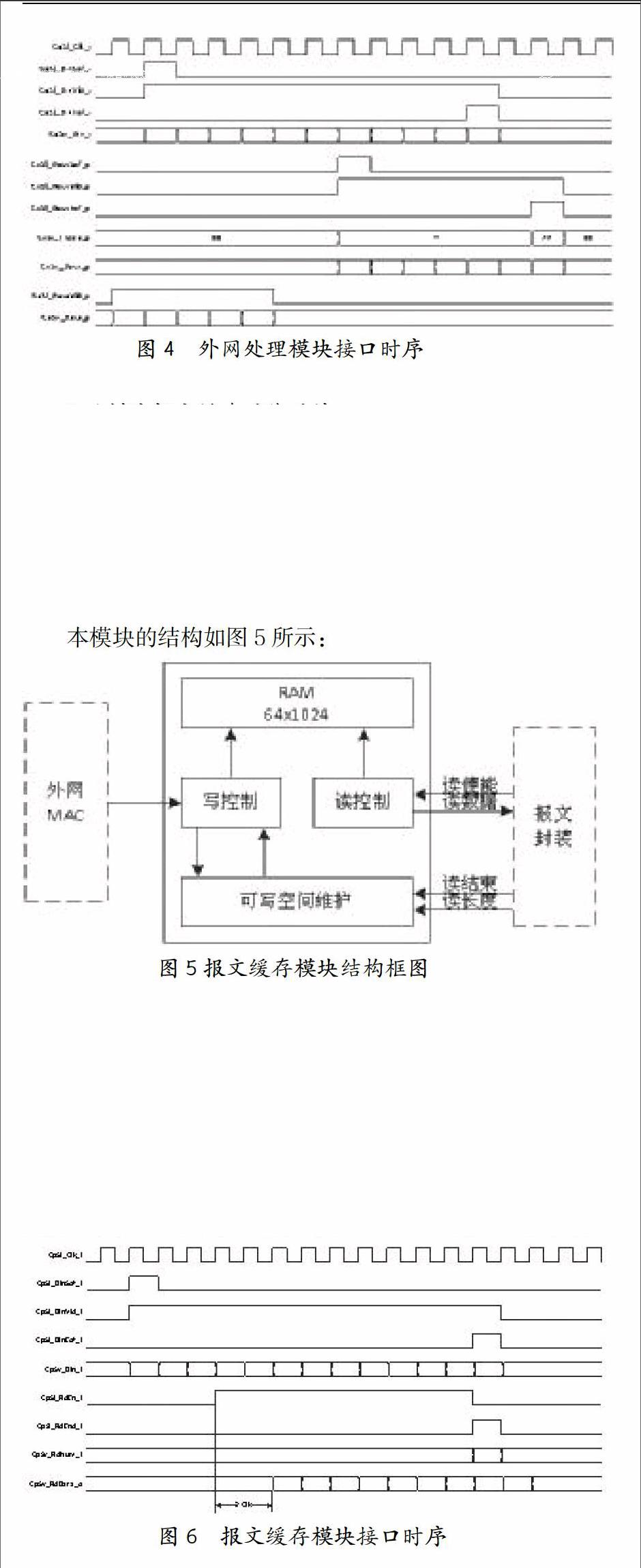

本模块的功能是:用于缓存接收到的报文,等待本报文的过滤结果,由报文封装模块读取此报文或者丢弃报文。本模块实质上是一个循环的buffer,其位宽是64,深度是1024,可以存储5个最大的1518Bytes报文。缓存模块内部维护读写地址和可写的空间,当可写的空间小于1518Bytes时,不再接收数据。

本模块的结构如图5所示:

处理流程为:

(1)当报文到达时,首先检查可写空间是否大于1518Bytes,如果大于则向RAM中存入次报文,写地址,循环累加,写完后将本次写入的数据量送给可写空间维护,如果小于1518Bytes丢弃本报文,写地址不变;

(2)写空间维护,维护一个Counter,累加写数据量,累减读数据量,用RAM的总空间减去这个Counter就是可写空间;

(3)当收到报文封装模块的读使能时,读地址累加,读取RAM送出读数据。

3.子模关键字提取功能设计

本模块的任务是:在报文中提取过滤规则的关键字,关键字为标准IP协议数据包。

通过Type识别是否为IP报文,如果是,继续提取Protocol、SIP、DIP;通过Protocol识别是否是TCP或者UDP报文,如果是,继续提取SPort与DPort。报文结构如图6所示,但是没有option域。另外需要获得本报文的长度(以Byte为单位)。

处理流程图如图7所示。

四、设计仿真测试

上述设计代码在综合后下载至硬件FPGA硬件板后,配合x86端测试软件进行测试。限于实际条件,采用自循环数据测试数据收发,以及指定IP地址和端口地址的过滤测试,测试模式如图8所示。经实际测试,系统能够完成百兆数据的线速收发和指定规则的过滤。

五、结束语

本文基于FPGA的防火墙设计完成了基本的设计目标,能够正常转发和过滤指定规则的数据,能够准确进行仿真和验证,但仍属于教学演示性设计,后续可以继续进行优化,使系统更加完善。

(通讯作者:刘超)

参考文献:

[1]夏宇闻.从算法设计到硬件逻辑的实现[M].北京:高等教育出版社,2001.

[2]王金明,杨吉斌. 数字系统设计与Verilog HDL[M]. 北京:电子工业出版社,2002.

[3]郑尧.硬件防火墙中多模式匹配算法的设计与实现[D].哈尔滨:哈尔滨工业大学,2009.

[4]唐正军,李建华.入侵检测技术[M].北京:清华大学出版社,2004.

[5]Wes Noonan, Ido Dubrawsky(美).防火墙基础[M].北京:人民邮电出版社,2007.

[6]胡道元.网络安全[M].北京:清华大学出版社,2004.

[7]石晶林,程胜,孙江明.网络处理器原理、设计与应用[M].北京:清华大学出版社,2003.

[8]肖晨阳.基于FPGA的硬件防火墙设计和实现[D].长沙:湖南师范大学,2009.

作者简介:唐泽坤(1994- ),男,山西长治人,大学本科在读,电子科学与技术专业;刘超(1981- ),男,辽宁凌源人,硕士,讲师,研究方向:嵌入式系统。