Verilog HDL 主题—案例组合式实验教学实施

柳 欣

(山西大学商务学院 信息学院,山西太原 030031)

0 引 言

一体化数字集成电路IC(Integrated Circuit)是各种控制/智能终端系统的核心部分。掌握数字IC 设计可以为特定领域做出贡献,如老年护理和独立生活的生物电位监测,护理人员远程监测多项生命体征参数,以识别老人移动、行走状态,监测是否跌倒等。目前EDA(Electronics Design Automation)发展已经使数字IC 设计方法从图形转向硬件描述语言HDL(Hardware Description Language),它意味着数字IC 设计变得更加抽象。成果导向教育(Outcome based education,OBE)倡导学生与教师精诚合作,共同完成学习过程,最后一起分享学习成果,享受学习乐趣[1]。为使学生能够较好地参与到课堂教学中来,基于Verilog HDL 的主题—案例组合式实验教学设计,意在通过基于IC 基本技术的典型设计实例回应到实际项目,为学生提供简便高效学习方法的同时,拓展学生在未来特定领域实现数字IC 设计并有效改进现有控制系统的能力。

教学依据的线上教学平台为推送资源及组织教学活动平台——学习通[2]、虚拟仿真实验室Quartus9.1、集中教学平台——腾讯会议;线下衔接教学平台为多媒体环境的现场实验室。OBE理念下线上线下可衔接的实验教学实施及学习效果导向如图1 所示。

1 基于案例的分层推进式目标设计规划

1.1 数字IC 设计课程的主要目标

培养学生掌握数字IC 设计的能力,包括编写Verilog HDL,运行EDA 工具来模拟、综合和测试及验证FPGA 设计[3]。

(1)了解数字IC 设计方法。①设计流程;②设计仿真,综合和验证。

(2)能够编写Verilog HDL 代码。①理解Verilog HDL 的结构、数据流和行为描述;②理解Verilog HDL 与硬件架构的关系。

(3)能够使用EDA 工具和FPGA 测试板。①使用EDA 工具完成数字IC 设计的能力;②通过EDA 开发工具和FPGA 测试板验证数字IC 设计的能力。

(4)能够反思已有设计并通过组讨论持续推进设计方法的优化。①了解自顶向下、分层和并行设计方法;②了解流水线、多循环和硬件共享先进的设计技巧。

1.2 IC 设计课程的预期学习成果

图1 OBE 理念下线上线下可衔接的实验教学实施及学习效果导向图

学习者完成课程应达到学习成果:①理解Verilog HDL 语法、编码、语法和语义;②理解物理硬件架构与Verilog HDL 之间的关系;③掌握IC设计流程,包括Verilog HDL 代码模拟、单元库、综合、时序分析和设计验证;④具备通过分析现有案例来组织实施项目的能力;⑤具备通过FPGA测试板,运用知识验证数字IC 设计的能力;⑥能够拓展运用数字IC 设计能力到特定应用领域。

1.3 学习成果的能力更新和升级

采取以案例为核心、讲座和实验同步组合实施的一套完整教学设计,组织的学习方式将支持学习者学习能力的自我更新和持续发展。

(1)知识理解。①利用本课程知识,理解与案例直接相关问题;②分析梳理实际项目与现有案例之间的知识点关系;③思考和应对新项目、新课题的考察和挑战。

(2)智力技能。①分析案例实施中成功或失败的原因;②总结小组经验基础上优化原有实验设计;③小组间讨论和经验分享,获得新思维启迪;④拓展应用案例做更进一步研究,尝试解决新问题或完成新项目。

(3)实践技能。①编写Verilog HDL 开发特定数字IC;②利用数字IC 实现既定算法;③使用FPGA 验证数字IC 设计。

(4)整合技能。①应用真实案例来帮助理解抽象问题;②关联问题到其他项目;③建立起独特的个人知识和能力集合。

2 基于案例的同步组合式数字IC内容组织

2.1 课程内容形式的设计组织

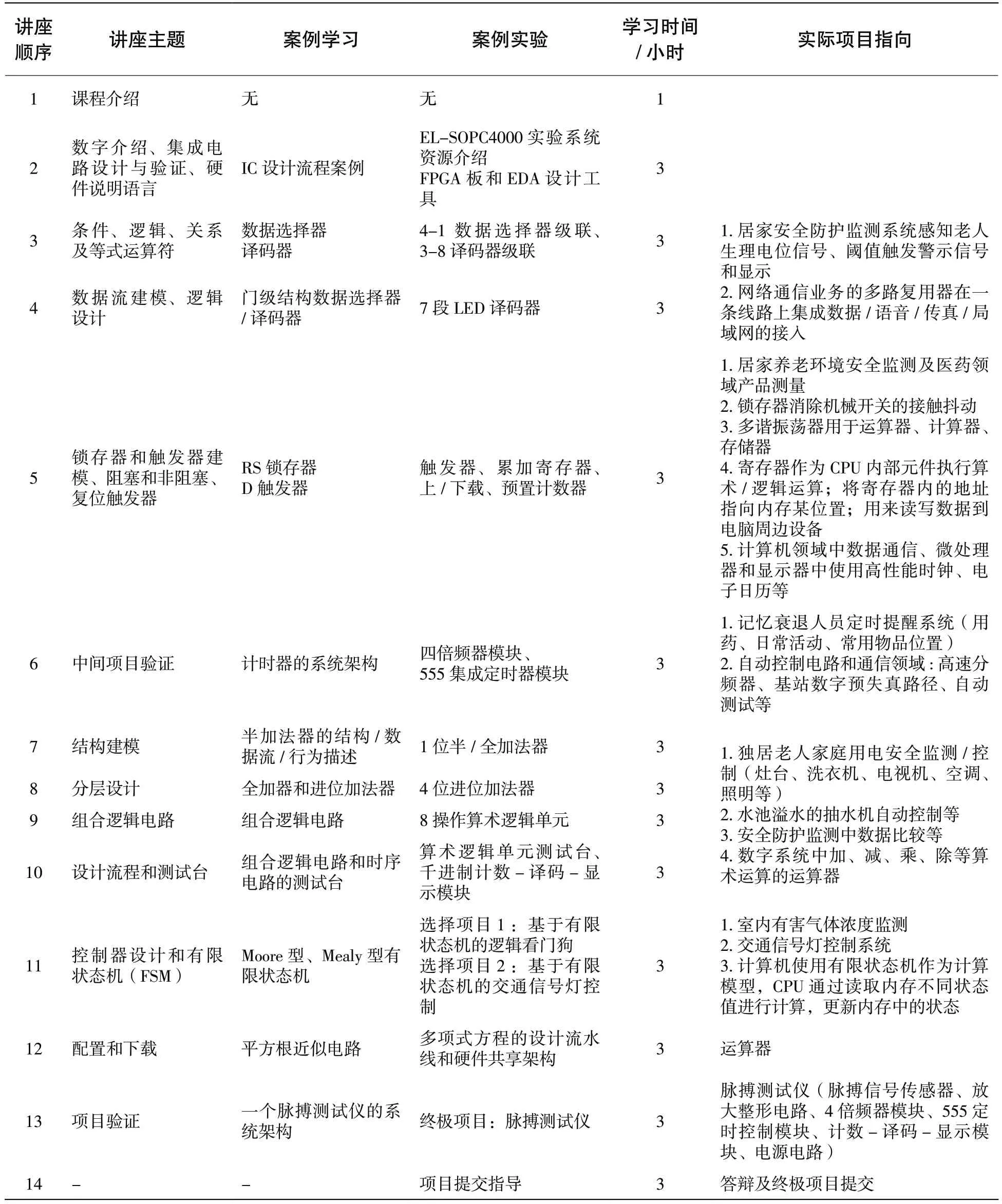

由于所提出的数字IC 设计课程是基于案例的教学,因此在实践教学实施中最好安排主题讲座和实验任务为同步进行。课程包括10 个讲座主题和2 个项目。每个讲座由讲座主题和实验室的代表性案例组成,每个案例包括Verilog HDL代码中的物理结构、注释、真值表和各种描述的说明等内容。学生可以通过参考原理图和Verilog HDL代码,学习Verilog HDL代码的语法、语义,不再是纯粹面对那些抽象术语。案例集合的最终指向是终极项目,目的在于引导学生学习如何完成数字IC 设计。2 个项目为脉搏测试仪和选择项目逻辑看门狗或交通信号灯控制。以终极项目脉搏测试仪为例,分别在第6 次、第10 次讲座指导学生设计完成四倍频器模块、555 集成定时器模块和千进制计数—译码—显示器3 个核心子模块。第13 次讲座完成终极项目脉搏测试仪的设计验证。按时间顺序列出主题讲座、案例、案例实验、实验室学习时间、实际项目指向,见表1。课程除了表1 第/3 栏所示的1、6 和13 课外,分为10 个主题。

2.2 实践教学实施的用时安排

课程设计安排共13 次讲座,除第1 个讲座为1 小时外,其余都设计为3 个小时。每周需3个小时,分14 周完成。此外需为每次实验教学实施留出以下时间:①根据课前教学活动的分组任务制定小组实验方案并虚拟仿真初步测试的时间;②学生在实验室以分组形式按既定实验方案自主实验和模块项目操作的时间;③实验教学人员检查和验证由学生完成的实例、中间项目和终极项目的时间;④教师根据现场操作实例解释模块实验、模块和项目之间关系的时间;⑤学生小组间讨论、分享实践经验、组间互相指导的时间;⑥教师对实施结果分析和说明,提炼新方

法、新思维和新设计,推动组内和组间实验能力整体提升的时间;⑦实验后的反思总结,进一步优化实验设计、实验流程和问题解决的时间。

表1 基于案例的数字IC 设计课程的讲座和实验组织

3 基于VerilogHDL的课程案例实践教学实施

3.1 累加寄存器案例描述

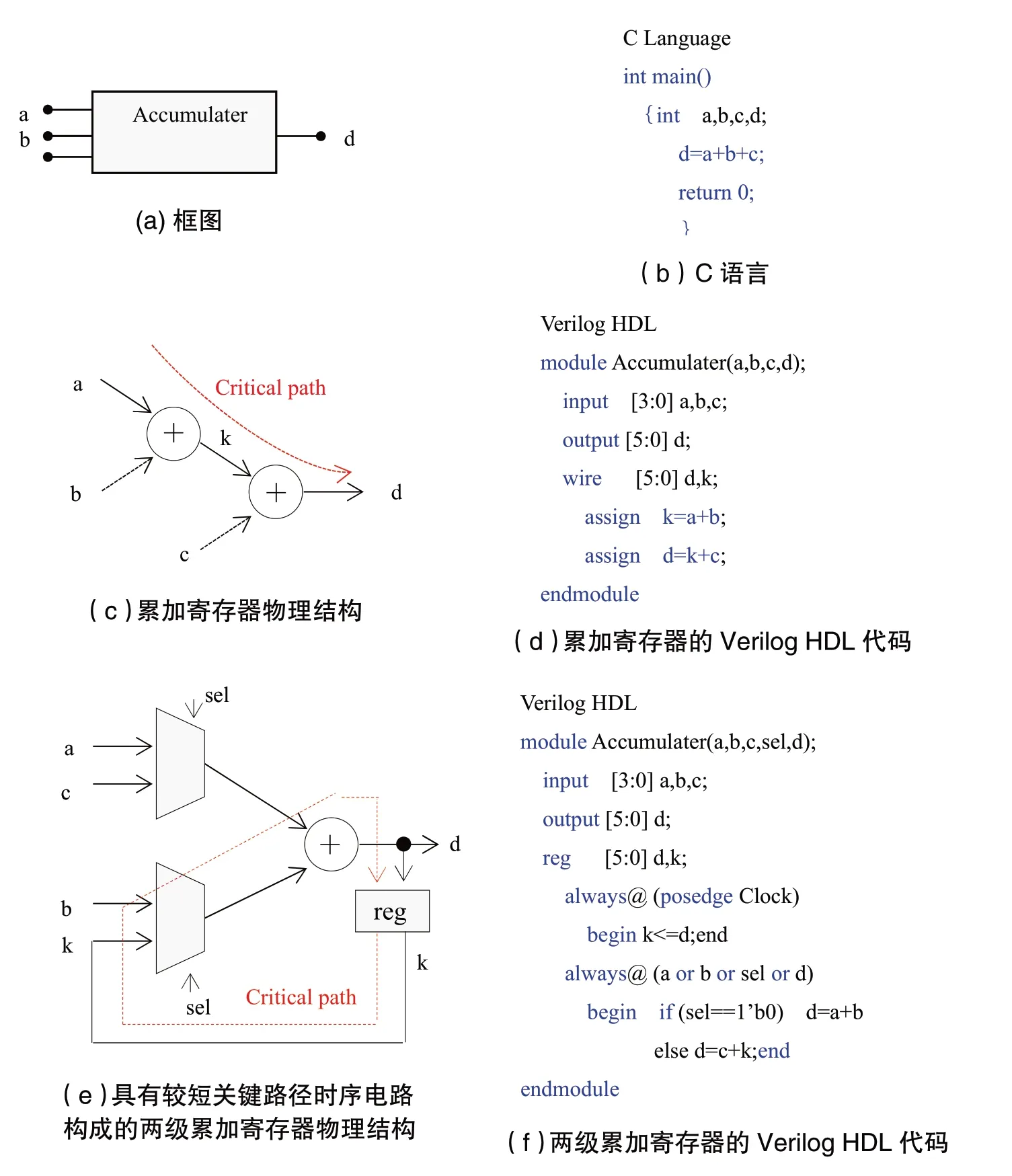

如图2 所示为讲座5 的一部分,显示一个累加寄存器案例,用于说明指令库软件和Verilog HDL 代码之间的区别。这个阶段学生已经了解了课程前期内容的关键路径的含义。图2(a)显示累加寄存器的框图,由三个输入和一个输出组成。图2(b)显示的是C 语言中累加寄存器的软件程序,其中有四个整数变量和一个语句来完成累加的操作。图2(c)显示累加寄存器的物理结构,说明实际硬件和输入/输出部分的细节。此外,该图还显示两个加法器之间的寄存器连线k 以及从两个加法器的输入到输出的关键路径。

图2(d)给 出 累 加寄存器的Verilog HDL 代码。参考图2(c),学生可以通过将输入/输出和线声明映射到电路物理结构中的输入/输出端口和实际连接线来理解Verilog HDL 代码。算术和逻辑运算可以以相同的方式映射到实际组合电路中。它有助于学生了解Verilog HDL代码与物理结构之间的关系,进而更好地理解抽象Verilog HDL 代码中关键路径的含义。

图2(e)显示使用了两个数据选择器、一个加法器和一个寄存器的两级累加寄存器物理结构。该累加寄存器通过数据选择器和加法器设计的关键路径是从寄存器k 到输出d。图2(f)描述两级累加寄存器的Verilog HDL 代码。教师通过比较图2(c)和2(e)的物理结构来解释组合和时序电路的变化,有助于学生了解关键路径的含义,在Verilog HDL 语言和物理结构对比中更好地理解关键字“assign”和“always”之间的区别,此外还可以引导学生学习如何在设计中声明和使用寄存器。

3.2 累加寄存器案例的类组合展示方式

图2 解释C 语言和Verilog HDL 区别的累加寄存器案例

实际教学中把相关内容按类组合,以类组合方式呈现给学生。如该案例中,讲座ppt 显示的第一个类组合是图2(a)、2(b)、2(c)和2(d)的组合,用于说明选择器的第一个结构设计。为了在有限的一张幻灯片中呈现组合内容,可采用Focuksky 软件在同一张幻灯片的不同区域添加4个帧,将a、b、c、d 的内容分别放在4 个帧上。演示时即可同时呈现4 帧内容,也可通过光标指向来控制某帧放大到全屏幕展示。类似地,第二张幻灯片展示的是图2(a)、2(b)、2(e)和2(f)的类组合,用于解释累加器去符号的第二结构。最后一张幻灯片显示图2(c)、2(d)、2(e)和2(f)的类组合,用以比较两种不同的累加寄存器的描述和结构。通过这种分类组合的展示方式,学生不仅可以同时获取框图、语言、物理结构和Verilog HDL 描述的信息,还可以了解两种不同描述和结构之间的区别。

3.3 累加寄存器案例的拓展

图2 是基于案例的Verilog HDL 课程两级累计寄存器的教学示例。如在更多级寄存器组设计的情况下,设计中的声明和寄存器使用可以根据案例特点进行节点和线路的拓展修改。

4 IC设计课程实践教学设计实施的反馈评估

为取得实践教学实施效果反馈信息,针对性构建反馈评估方式,从学生学习本课程的背景知识和基于案例的数字IC 设计课程的回应两个方向做出相关调查。调查问卷由教学助手于终极项目审查后发放。第一类表列出学生背景包括性别、年级、专业、编程语言背景、FPGA 板和其他虚拟仿真实验平台使用经验等信息,意在了解数字IC 课程实践教学设计的实效发挥对相关专业课程体系中前导知识能力及第二课堂实践教学活动的依赖程度,发现存在的短板问题,以便从整个专业实践教学人才培养方案中予以调整。

第二类表是学生对基于案例的数字IC 设计课程回应的评估问卷信息,见表2。意在了解对基于案例式的实践教学设计的喜欢程度;学生对课程实际学习成果是否达到预期教学目标;这种学习Verilog HDL 的方法是否比抽象学习更见成效;教学设计的讲座部分所起作用是否达到预期设计效果;教学设计中的案例代表性和数量是否与课程匹配;讲座和实验同步组合的教学设计较非同步方式是否更佳;该教学设计是否值得在其他工程类课程中推广等。

5 结 语

Verilog HDL 语言的抽象性质对熟悉传统原理图输入法设计流程的学生来说是很大的挑战。基于主题讲座和实验案例组合式实验教学设计的实施方法,在推进学生学习效果的同时,持续提高了学生对更具复杂性案例项目的设计开发能力。希望这种实践教学方法可以帮助到其他具有与数字IC 设计课程相同特点的工程类课程。

表2 学生对主题-案例组合式的数字IC 设计课程的回馈信息调查