基于FPGA的Camera Link接口设计

任丽晔,汪 晨

(长春大学 电子信息工程学院,长春 130022)

随着工业相机的发展,为了配合高速、实时数据量的处理与传输,其对图像接口的要求也变得越来越高。目前,最快的一种工业相机输出接口是Camera Link接口[1]。Camera Link协议是一种专门针对机器视觉应用领域的串行通信协议,Camera Link标准中有6对差分信号线,其中4对用于并行传输相机控制信号,另外2对用于相机和图像采集卡之间的串行通信[2]。

FPGA开发所使用的硬件描述语言为Verilog HDL/VHDL,其独特的硬件结构和并行处理优势可以大大加强传输系统的实时性[3]。本研究基于FPGA实现了Camera Link接口的方法,通过Camera Link接口把实时图像传输到FPGA图像采集卡中进行数据实时处理,并实现采集卡和计算机之间的通信。

1 Camera Link设计方案

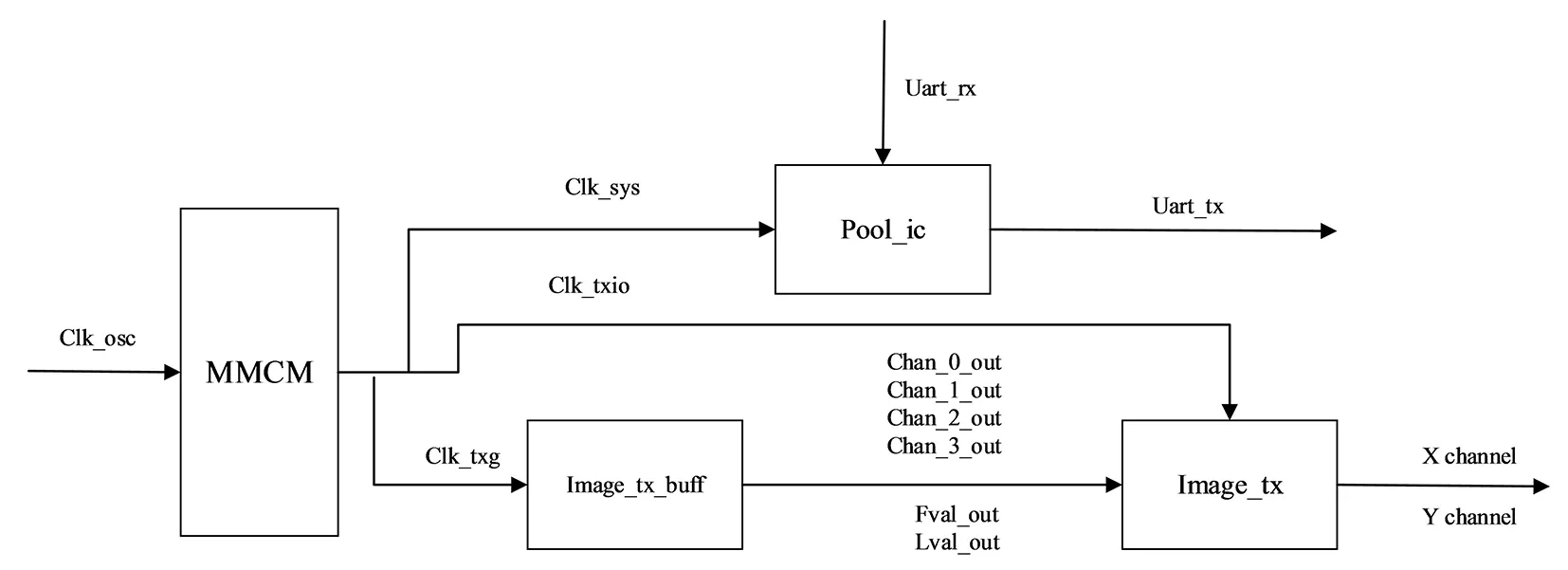

设计基于主控芯片Spartan-7系列的FPGA芯片。相较于之前的芯片,Spartan-7有更高逻辑与IO比,性能更强,也降低了功耗。使用MMCM原语对时钟进行分频和倍频,分别作为图像传输和通信串口的时钟输入。设置图像传输模块,分为4个通道进行传输,像素为3 000*3 000,在每一次的行信号lval_out下,传输1 250个。最后由图像的发送端接收信号后,发送两个通道的信号。设置串口通信的模块,由PC端发送5个不同的16进制数,通过串口返回另外5个16进制数。最后实现所有的功能,其具体的流程FPGA模块框图如图1所示。

图1 FPGA模块框图

根据传输的位数,选择使用Camera Link基本模式,即Base模式。总线发送端将28位并行数据转换为4对LVDS串行差分数据传送出去,运用 LVDS 串行差分数据线传输图像数据输出同步时钟;总线接收端将串行差分数据转换成28位并行数据,同时转换出同步时钟。由于采用串行差分传输方式,既减少传输线的使用量,又减少传输过程中的电磁干扰。

2 逻辑设计

2.1 时钟分频

MMCM是混合模拟时钟管理器,有强大的时钟管理功能,其具体功能分别为时钟去歪斜、基于整数分频器的数字效率合成、基于小数分频器的数字频率合成、抖动滤波器和相移。MMCM_BASE是基本时钟管理模块的原语,例化原语可以实现MMCM的基本功能,调用全局时钟资源[4]。

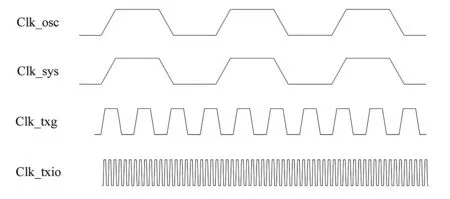

由于FPGA输入的系统时钟clk_osc为50 MHz,所以,MMCM_BASE原语的逻辑功能是以50 MHz时钟信号为基数进行分频和倍频,考虑整个模块的时序与逻辑,对串口通信选择使用50 MHz的时钟输入clk_sys,图像传输选择使用210 MHz的时钟输入clk_txg。图像输出的模块需要2个时钟,其中clk_txio时钟的大小是clk_txg时钟的7倍。像素时钟 clk_txg首先经过延时模块平衡7位数据深度的延时后输入MMCM,通过数据和时钟解串输出clk_txio,所以时钟大小为1 470 MHz。这种时钟输入的方式可以保持其相位相同,以便于更好的分析。MMCM时钟的时序图如图2所示。

图2 MMCM时钟时序图

2.2 图像传输

图像的传输是Camera Link接口中最重要的部分。Camera Link标准使用4对LVDS线缆用来实现相机的控制,它们被定义为相机的输入信号和图像采集卡的输出信号,完整的Camera Link接口包含着发送端和接收端[5-6]。

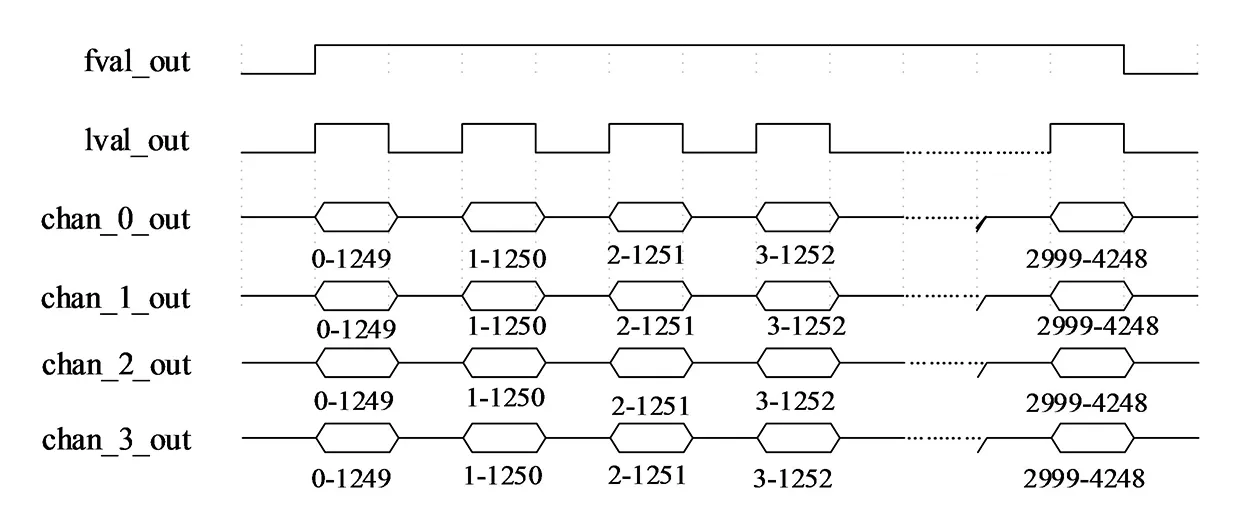

利用image_tx_buff模块发送相机的有效数据,共有4个通道chan_0_out、chan_1_out、chan_2_out、chan_3_out同时发送像素。当发送新的一帧数据时拉高fval_out场信号,代表一帧数据的开始;拉低fval_out场信号即代表一帧数据的结束。lval_out行信号代表一行的有效数据,一行的有效数据为1 250个,为了不互相干扰,设置每行信号之间间隔50个时钟周期。当所有像素传输完后,同时拉低场信号和行信号,继续等待500个时钟周期后进行下一幅图的传输。为了间隔时钟周期的正确性,分别添加计数器进行计数,每次计数完毕后对计数器进行清零,否则会造成程序的混乱。图像发送数据的时序图如图3所示,0~1 249代表的是一行中传输的数据,下一行则从1开始。对于Camera Link标准中的数据有效信号DVAL,只有当场信号和行信号都为高电平时,拉高DVAL信号则代表数据是有效的。利用FPGA直接生成信号,输出图像这种方式,考虑到了FPGA的现场可编程特性,使用灵活方便,并且能够降低硬件电路设计难度。

图3 图像数据时序图

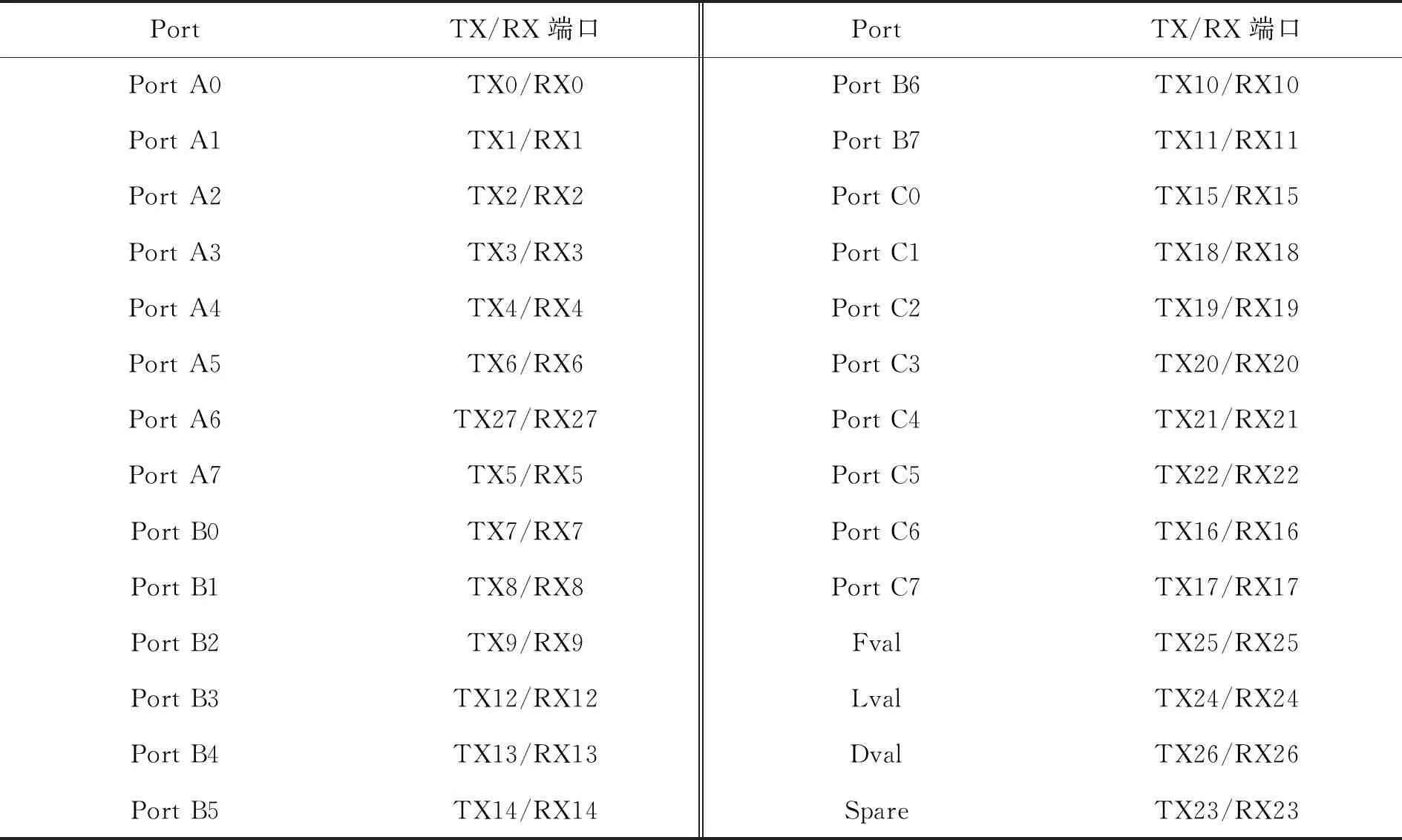

在Camera Link标准中,选择使用Base基本模式对TX/RX端口的28位数据信号以抽象化的形式分为Port A、Port B、Port C。具体分配如表1所示。采用Port A和Port B的16位数据为图像的有效数据,4位Fval、Lval、Dval、Spare为图像传输的同步信号。

表1 Camera Link接口的端口分配

当检测到image_tx_buff模块中的图像信号,image_tx模块会对图像信号进行发送,Camera Link 标准中并行数据在进行发送时是按照一定的映射方式将数据顺序打乱后进行传输,这个过程定义为位编码[7]。位编码后的数据使用OSERDESE原语可以将7bit并行数据转换成1bit串行数据。OSERDESE原语可以实现的并转串转换比率包括3种:2∶1、3∶1和4∶1[8]。单个IOB 模块最高可以被配置为4∶1串并转换比率,因此,使用两个OSERDESE串联进行,分组后实现像素数据7∶1的串并转换比率。OSERDESE数据比率转换需要使用2个时钟:clk_txg 和 clk_txio,分别是高度的串行时钟和分频并行时钟,且2个时钟必须相位对齐。

因此,image_tx模块中Camera Link接口的发送端主要分为两个部分:第一部分为输出编码部分,首先根据表1数据位对应关系,将需要发送的数据映射到16bit数据输出端TX;第二部分为串并转换部分,主要目的是完成由16bit数据到两组并行7位数据的转换,同时完成两组并行7位数据到串行差分数据的转换;最后通过2个通道X channel和Y channel进行输出。

2.3 串口通信

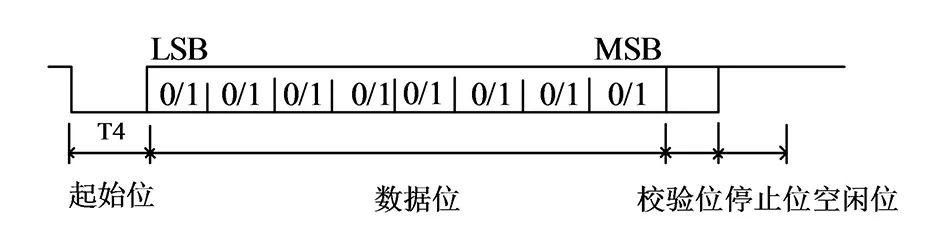

串口数据的接收相对于PC机而言,FPGA扮演从机角色,在固定的波特率下,捕获主机发送的数据,根据 UART串口发送时序,串转并得到发送的8位数据[9]。UART传输时序如图4所示。从波形上可以看出起始位是低电平,停止位和空闲位都是高电平,利用这个特点可以准确接收数据,当一个下降沿事件发生时,会将进行一次数据传输。

图4 UART传输时序图

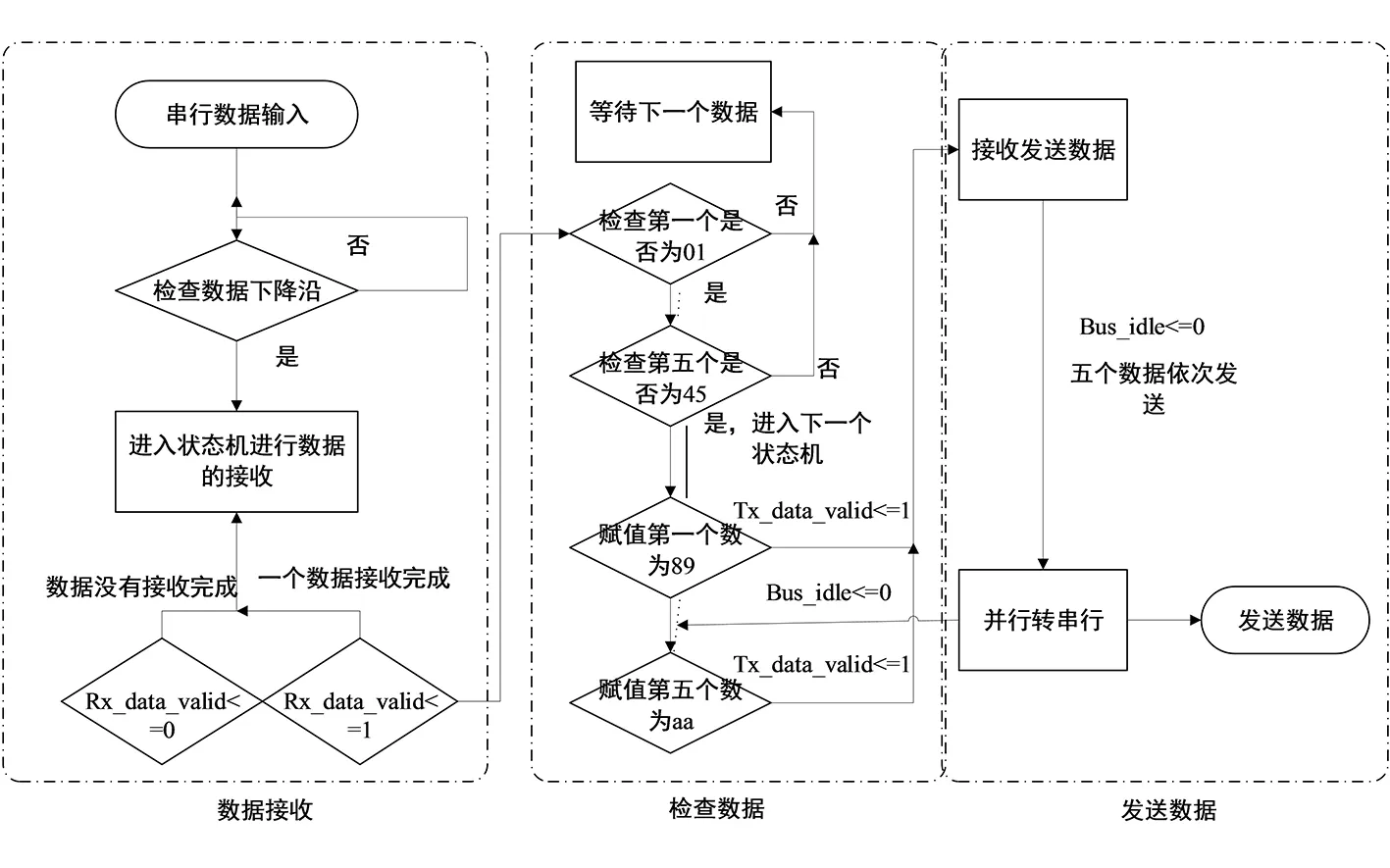

通信串口pool_ic模块主要分成3个部分:接收数据、检查核实接收的数据是否正确、发送数据。当接收模块检测到数据的下降沿时会进入状态机,这是串口的起始位置,等起始位结束后进入数据位的接收状态。状态机的作用是接收数据,并将串行数据转为并行数据送入下个模块进行使用。为避免数据出错并满足采样定理,设置一个关于波特率的计数器cycle_cnt,保证在接受数据时每个数据都在波特率计数器的时间中点进行采样。当检查数据的模块检测到使能信号rx_data_valid的值为1时,开始接收上一个模块的数据。检查传来的数据值是否为01,直到接收到5个正确的数据就进入下一个状态机。将要发送的第一个数据赋值为89,并且拉高使能信号tx_data_valid,将数据传入发送模块。发送模块的逻辑设计和接收模块一样。其具体流程框图如图5所示。

图5 通信串口流程框图

常见的串口通信波特率有2 400 bps 、9 600 bps、115 200 bps 等,发送和接收波特率必须保持一致才能正确通信,波特率的大小会影响数据的传输速率。本研究使用115 200 bps的波特率,代表一个数据位的时间长度是1/115 200 s。且不设置奇偶校验位,发送端发送数据分别是01、02、03、56、45,接收端返还的数据为89、67、55、23、aa。如果发送其他的数据和顺序时,FPGA将不返还数据。

3 仿真结果与分析

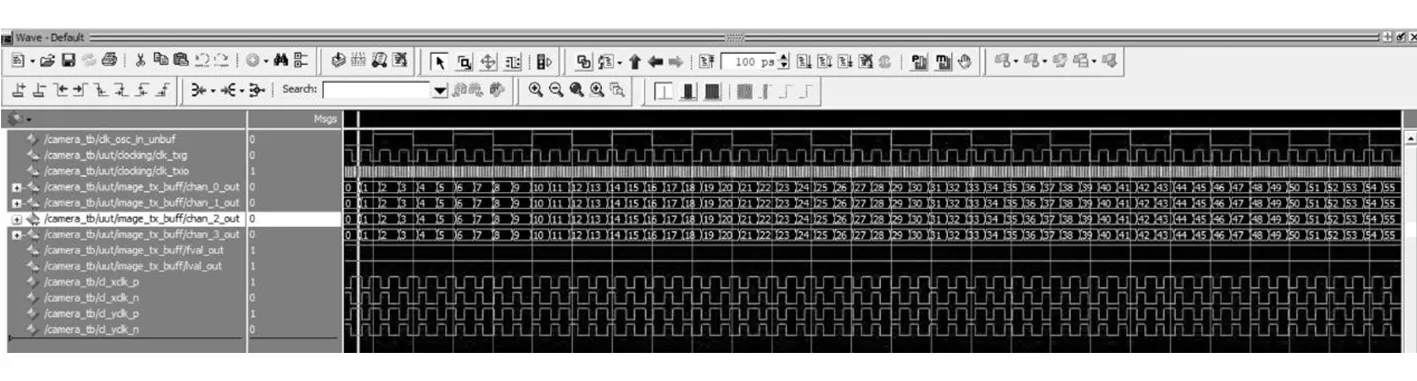

调用Modelsim仿真软件进行测试,其仿真结果如图6所示。由仿真结果可以看出,时钟分频和倍频的结果符合设计要求,clk_txg和clk_txio是同相位,且clk_txio是clk_txg的7倍。串口通信模块接收到了测试文件发送的01、02、03、56、45这5个数据,并且不存在缺少数据和错误数据的情况,其输入的方式是串行输入。并且经过检查后,输出89、67、55、23、aa这五个数,并没有出现顺序上的错误。根据串口的协议,最后并不是8位数据并行发送,而是串行的形式传输出去,说明UART串口的收发模块通信正常。图像传输模块由于数据过于庞大,会有折叠,但可以清晰地看出与上述逻辑相同。传输一行有效数据需要25 μs,每一行包含1 250个像素点。传输一幅图所需要的时间为78 ms,在1 s中可以传输12幅图。过程中均无缺少像素点的情况发生,每一行之间时钟周期的间隔较大,不会产生干扰。且并转串的过程中没有发生错误,说明图像传输收发模块正常。

图6 仿真结果图

4 结语

本研究主要根据Camera Link标准协议,基于FPGA设计了3个模块来实现Camera Link接口设计,分别为时钟模块、图像传输模块、通信串口模块。根据所设计的方案,FPGA设计的图像信号结构简单,实现方便,而且具有很强的可扩展性。通过Camera Link接口和相机连接,可以从相机获得高分辨率的实时图像,并传输到FPGA中进行实时图像处理并输出,实现采集卡和计算机之间的通信,用于相机功能参数的设置。这种简单可靠的设计对FPGA在的Camera Link开发中具有较强的可操作性和应用价值,为正在研制的实时高速图像采集卡奠定了基础。