深槽介质工艺制作高密度电容技术

黄 蕴,高向东

(中国电子科技集团公司第58研究所,江苏 无锡214035)

1 引言

由于微电子技术领域的不断创新,使半导体器件能够以每三年集成度翻两番、特征尺寸成倍缩小的速度持续发展几十年。集成电路工艺中的特征尺寸更小,集成密度更高,集成电路材料趋于多元化,集成的元件种类更多,集成的系统更为复杂、庞大,集成电路的功能更为完善和强大,集成系统的功耗更低,成为微电子工业基本发展趋势。目前微电子技术已经发展到了一个关键的时期,系统芯片(System On A Chip)是21世纪微电子技术发展的重点。SOC是从整个系统的角度出发,把处理机制、模型算法、芯片结构、各层次电路直至器件的设计紧密结合起来,在单个(或少数几个)芯片上完成整个系统的功能,它的设计必须是从系统行为级开始的自顶向下(Top-Down)的。很多研究表明,与IC组成的系统相比,由于SOC设计能够综合并全盘考虑整个系统的各种情况,可以在同样的工艺技术条件下实现更高性能的系统指标。与采用常规IC方法设计的芯片相比,采用SOC设计方法完成同样功能所需要的晶体管数目约可以降低l~2个数量级。虽然SOC将带来许多市场新契机,不过,随着晶片集成度的提高与系统架构落实于晶片层次,不论在设计方法学、晶圆制程、封装、测试等方面,都面临着极大的挑战。SOC制造设计必须克服不同电路区块不同制程兼容性的问题,其中较简单的是逻辑电路间的整合,难度较高的是模拟电路与逻辑电路间的整合,最难的是逻辑电路与记忆体间的整合,特别是嵌入D RA M的情况。动态随机存取记忆体(DRAM)的核心记忆单位是1T1C(1个电晶体搭配1个电容器),DRAM的元件设计在市场激烈竞争之下正快速地向高密度、高容量方向发展。

在元件面积快速缩小的趋势下,每一个记忆体单位工作所需的电容却大致维持不变。如何能够在单位元件面积不断减小的同时,设计出电容相当的电容器(即提高电容密度)是DRAM技术中最重要的挑战之一。在百万位元(Mega Bit)记忆体之前的电容器大多是属于平面式设计,基板面积受限于元件平面面积。进入4Mb之后,传统的平面式电容器已无法储存足够的电荷,电容器的设计进入三维立体时代。其中最主要的两股主流是堆迭式电容器及深槽式电容器。前者以增加基板单位面积的表面积及高介电系数材料(Ta2O5、BST、Al2O3)的研发为主,后者则直接在底材下方挖掘深槽以增加元件面积。两种不同的技术各有其优缺点,并且都已证实可以应用在十亿位元(Giga Bit)以后的记忆体制造。

本文介绍了一种基于深槽介质工艺制作高密度电容的技术,制作流程完善,电容耐压性能优良。对于深宽比约为20、介质层结构为ONO的深槽电容,其电容密度是相同平面面积的平面电容的20倍。同时改变深宽比、介质层结构还可以得到不同的电容密度。

2 工艺概述与实验

通过DRIE(Deep Reactive Ion Etching)方式直接腐蚀到Si衬底,以物理方式形成深槽。技术重点与难点是深槽的形貌和介质的填充效果。本文采用深槽介质工艺的主要流程如下:硅片→清洗→PESiO2淀积→Hard Mask光刻/腐蚀→深槽刻蚀→全剥SiO2→N+下电极形成→ONO生长→上电极淀积→光刻/腐蚀→电性能测试(电容、击穿等)。完成后的电镜照片如图1所示。

2.1 深槽刻蚀

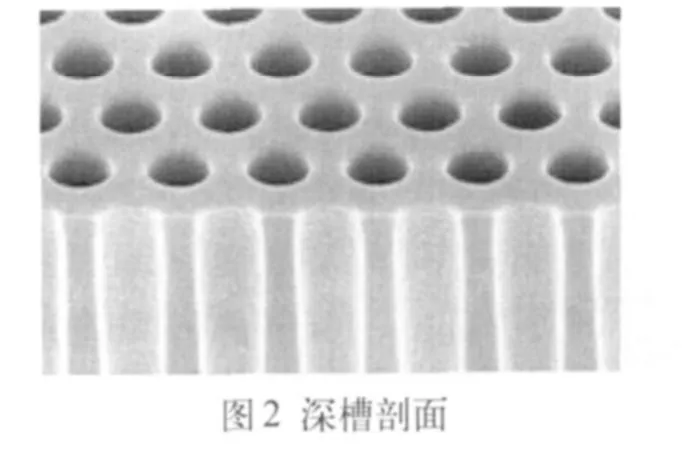

深槽刻蚀技术以hard mask(SiO2)作为刻蚀的掩蔽层,以硅刻蚀和聚合物淀积周期性交替进行为基础,对硅进行各向异性刻蚀。由于其工艺自身特点,所以工艺过程中需要刻蚀性气体和Polymer淀积性气体周期性交替通入反应腔中。其剖面形貌陡直,侧壁光滑,与晶体表面的夹角小于85°,且沟槽底部是圆弧形的。如有尖角形状则可能导致氧化期间产生过度的应力并使氧化层产生重要缺陷导致击穿电压低和漏电等问题。深槽剖面见图2。

2.2 电容介质的生长

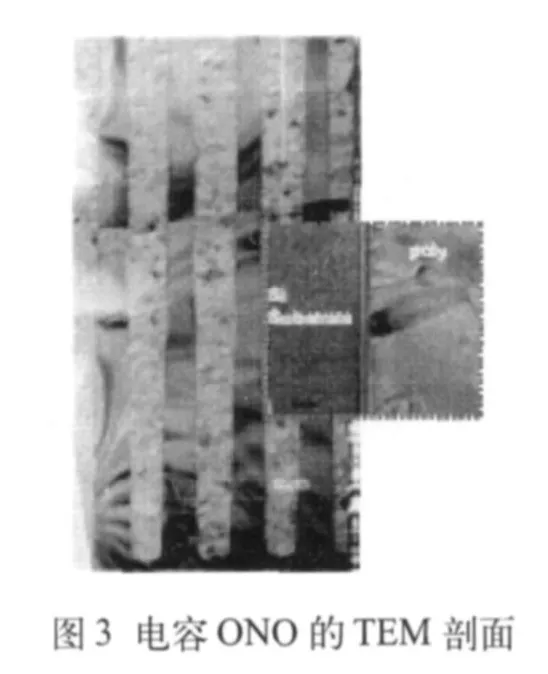

介质层的质量直接影响电容的性能。由于深槽刻蚀后其槽的深/宽比特别大,给介质的形成带来了难度。既要有和侧壁良好黏附性的要求,又必须满足均匀性的要求。实验采用低温掺氮氧化+LPSIN+TEOS 形成ONO的介质层。图3是该ONO结构的TEM 结果。

2.3 电容上电极填充

由于深槽的深/宽比特别大,所以上电极的选择非常重要,必须满足良好的黏附性,淀积时不产生空洞。因为空洞可能会带来沾污,从而影响器件的性能;同时,空洞可能会在后续的工艺中暴露出来,引起金属的断条。

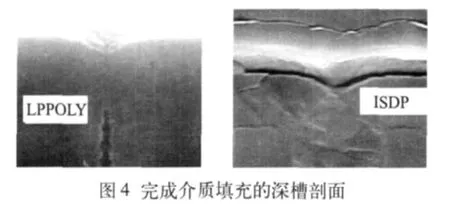

从理论上讲选用低温低压工艺有利于填充狭窄的深槽,有助于消除任何可能的应力以及由高温带来的形变问题。故选用LPPOLY和In Situ Doping Poly(ISDP)进行填充实验对比。图4 是不同填充结果的比较,可以看到选用ISDP填充完好,而且ISDP 淀积与掺杂同步完成。

3 实验结果

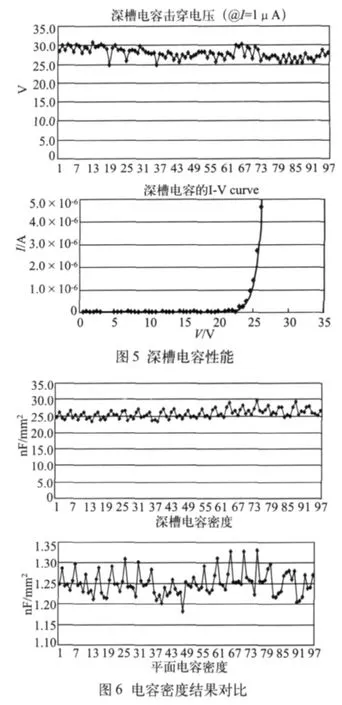

图5、图6 是采用上述方法制作的深槽介质电容的耐压与电容值。从图中可以看到深槽电容耐压大于25V且稳定,漏电极低。其电容密度是相同面积的平面电容的20倍。

4 结论

本文介绍了一种基于深槽介质工艺制作高密度电容的技术。采用特殊的深槽刻蚀、ONO介质、ISDP填充工艺制作的深槽电容,其电容密度高,是相同面积平面电容的20倍;性能优异,电容耐压达25V,漏电极低。

本文所介绍的高密度深槽电容重复性、稳定性好,采用这种电容结构的SOC芯片良率可以达到90%以上。

[1]Sugawara M, Stansfield B L. Plasma Etching Fundamentals and Applications [M]. Oxford University Press,1998

[2]H. Koyanagi. N.ovel High Density, Stacked Capacitor MOS RAM[J].IEDM Tech,1978:348-351.