基于FPGA的脉冲发生器波形模块设计

张孝飞, 赵孔新, 张赛男

(长春工业大学计算机科学与工程学院,吉林长春 130012)

0 引 言

高速脉冲发生器作为现在测试领域中一种重要的测试工具,能够产生脉冲宽度、脉冲幅度、信号延迟等脉冲参数充分可控的脉冲信号,以满足特定的测试要求。脉冲频率、信号延迟调整的精度及分辨率、参数可编程能力和信号功率、脉冲宽度调整的精度和分辨率等方面的因素决定了高速脉冲发生技术的先进性。为了使之具有高速灵活、高精度及高分辨率的特点,文中用Altera公司可编程FPGA芯片以及安森美公司可编程延时芯片和高性能D触发器来设计。

1 总体设计思路

脉冲发生器的波形模块设计是由FPGA内部的脉冲/群脉冲产生电路产生脉宽、占空比、脉冲周期、脉冲个数可调的脉冲[1]。考虑到如果只用FPGA内的时序做脉宽调整,而FPGA内部的脉宽调整是通过计数器计数来调整的,调整的频率是根据当前的周期调整的,这样就不能满足高精度的要求,所以考虑用内部计数粗调加外部芯片细调的方法来达到高精度。

通过FPGA内产生上升沿触发信号和经过粗调加微调产生的下降沿触发信号送入高性能D触发器[2]来产生所需要的信号。此方案可以满足100 MHz脉冲的产生。

2 脉冲/群脉冲产生电路

2.1 设计方法

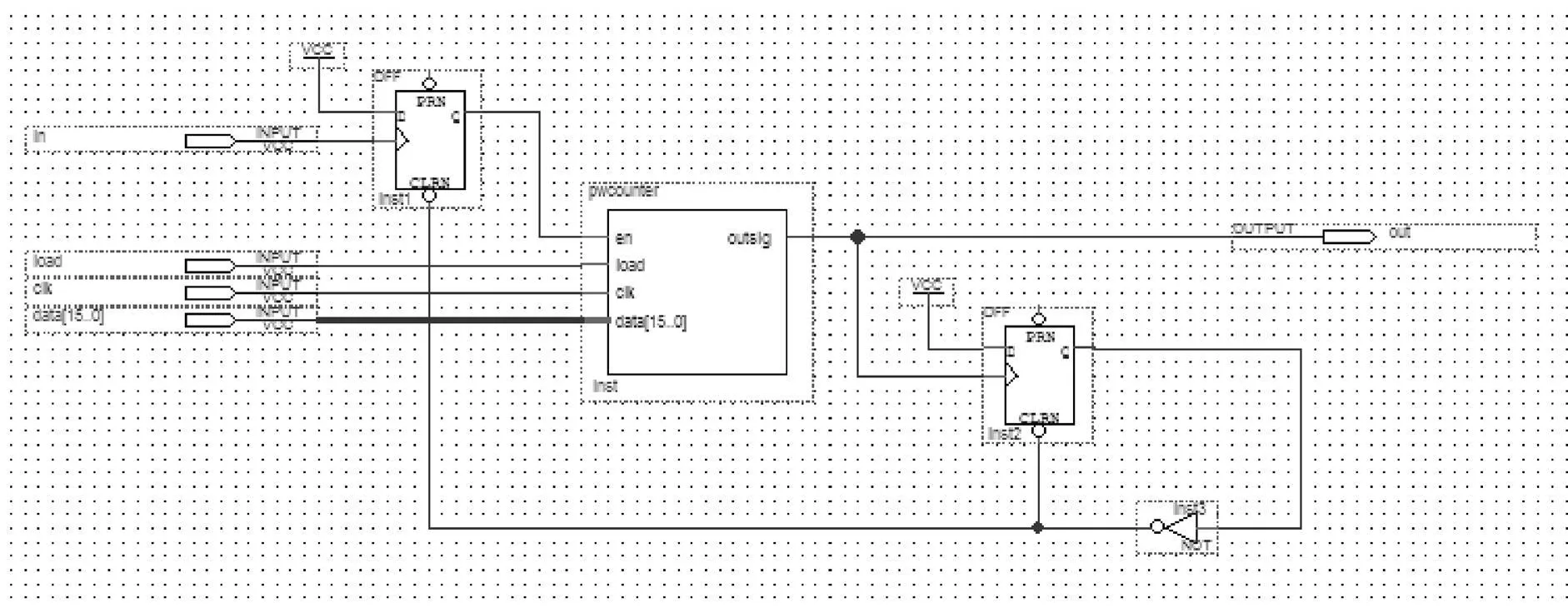

为了产生所需要的脉冲,可以利用Verilog HDL语言在FPGA内部编写单脉冲/群脉冲计数器。在其后面加上一个门控时钟电路和窄脉冲产生电路,门控时钟电路能够抑制毛刺的产生,窄脉冲产生电路能够是上升沿触发信号和下降沿触发信号是窄脉冲,满足设计的最小脉宽要求。原理框图如图1所示。

图1 单/群脉冲产生电路

2.2 工作原理

图1中,period[15..0]端是输入的群脉冲周期;num[15..0]是输入的群脉冲个数;clk是当前的时钟输入端;load是复位端,高电平有效;gate信号是经过模式选择的使能信号;out是脉冲/群脉冲输出端[3-5]。

单脉冲的产生是群脉冲产生的一种特殊情况,将群脉冲周期值period[15..0]和脉冲个数num[15:0]值设置成同样的值时就可以实现。

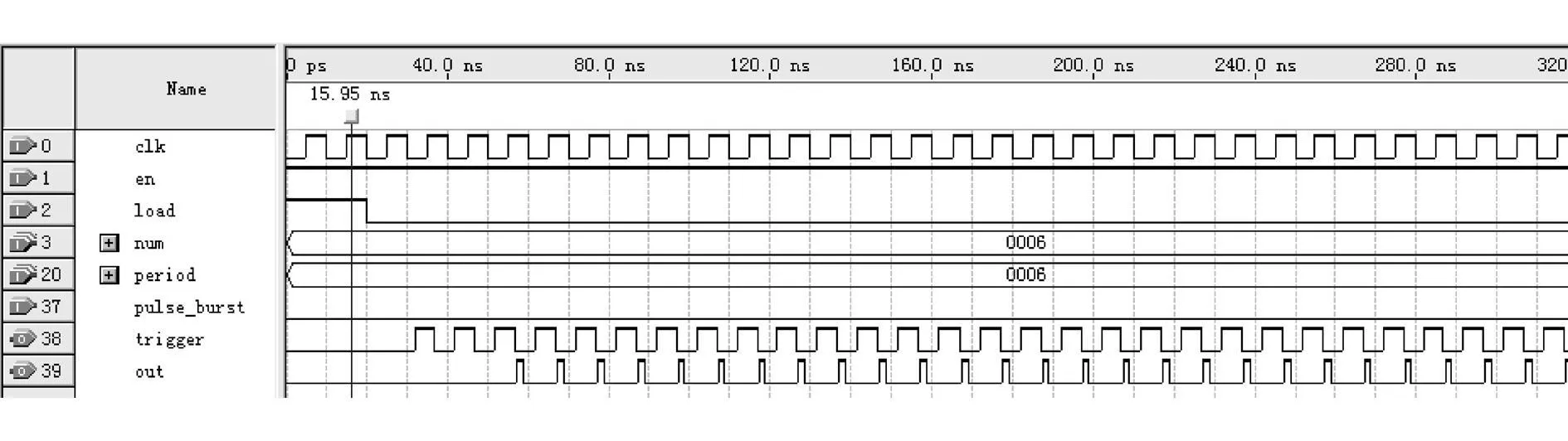

下面以群脉冲为例介绍单脉冲/群脉冲计数器模块的工作原理:设置num[15..0]和period[15..0]分别为6和10,gate(en)为1,在pulse模块的out将会连续输出6个时钟周期(clk)的高电平,然后连续输出4个时钟周期(clk)的低电平,这样计数器就计数完一个群脉冲输出周期,输出的高低电平通过后面的门控和窄脉冲电路产生窄脉冲信号。仿真结果[6]如图2所示。

图2 群脉冲时序仿真图

图中,pulse_burst和trigger是设计中触发模块的数据输入,pulse_bursr控制是单脉冲还是群脉冲输出,trigger是标志脉冲何时开始的。如果把num和period设置相同的数值,则是单脉冲输出,仿真结果如图3所示。

图3 单脉冲时序仿真图

3 脉宽参数的调整方法及电路设计

3.1 设计方法

如果只利用FPGA内的时序逻辑做脉宽调整,而FPGA内部脉宽调整是通过计数器计数的方式实现的,因此,其调整的分辨率就是当前时钟的周期,例如时钟频率为100 MHz[7],此时钟周期也就是当前时钟频率下的分辨率为10 ns,这不能满足高精度的要求。为了满足要求,选取安森美公司的可编程延时芯片MC100EP196,MC100EP196的分辨率是10 ps,单片延时最大10 ns,这可以满足大多数要求。如果仅仅使用可编程延时芯片的话,设计的脉冲是100 MHz,要求脉宽是5 ns~995 μ s[8],这个范围要求用大量的可编程延时芯片,因此,提出用FPGA+可编程延时芯片来设计脉宽的调整。整体方案如图4所示。

图4 脉宽参数调整及电路设计

3.2 设计原理

在设计100 MHz脉冲发生器时,当脉冲高于50 MHz时,脉宽的范围是10~20 ns。而选用的芯片范围是10 ns,所以,可以不用FPGA内部编程粗调,直接用两个延时芯片串联来调节脉宽的范围。而当低于50 MHz时,可以用FPGA+可编程延时芯片。粗调部分的编程模块电路和微调部分电路分别如图5和图6所示。

图5 粗调部分电路图

图6 微调部分电路图

4 数字脉冲合成电路

4.1 设计方法

数字脉冲合成电路是通过一个D触发器实现的,是前面脉冲产生电路产生的经过脉宽粗调、微调产生的上升沿触发信号和下降沿触发信号送入到数字合成电路合成最终的数字脉冲信号。数字脉冲合成电路如图7所示。

图7 数字脉冲合成电路

4.2 设计原理

数字脉冲合成电路的核心原器件是MC100EP51,具体设计是将MC100EP51的数据端D接LVPECL逻辑高电平,而MC100EP51的差分时钟输入端接由前端脉冲产生电路产生的上升沿触发信号LE+和LE-,其清零端RESET是接由经过脉宽粗调和脉宽微调后的下降沿触发信号TE+,这样D触发器就会在上升沿触发信号到来时形成数字脉冲的高电平,而在下降沿触发信号到达清零端时,触发信号会重新清零形成数字脉冲输出的低电平,即实现了最终数字脉冲的产成。

5 结 语

目前,脉冲发生器在测试领域占据着主要地位,然而,我国的这项技术比起国外来落后太多,多年来占据这个领域的产品都是国外的产品。所以对此技术的研究具有重大的意义。

[1] 何绪芃,曾发祚.脉冲与数字电路[M].成都:电子科技大学出版社,1995.

[2] 刘勇.数字电路[M].2版.北京:电子工业出版社,2008.

[3] 巴斯克.Verilog HDL入门[M].3版.夏宇闻,译.北京:北京航空航天大学出版社,2008.

[4] 杨恒.零起点学习单片机与CPLD/FPGA[M].北京:北京航空航天大学出版社,2007.

[5] 陈满.基于FPGA的高速可变周期脉冲发生器的设计与实现[J].国外电子元器件,2007(3):35-37.

[6] EDA先锋工作室,吴继华,王诚,等.Altera FPGA/CPLD设计[J].北京:人民邮电出版社,2005.

[7] 奚俊.脉冲发生器高速时钟模块设计[D]:[硕士学位论文].成都:电子科技大学,2008.

[8] 郑义.高速脉冲发生器信号合成与控制电路设计[D]:[硕士学位论文].成都:电子科技大学,2008.