一种高灵敏度测控应答机捕获算法设计与实现

唐 亮,王敏琪,王亚鸣,邹永忠

(1.上海宇航系统工程研究所,上海 201109;2.上海航天电子技术研究所,上海 201109)

0 引言

近年来,中低轨卫星数量逐渐增加,测控应答机的需求越来越大,指标要求也不断提高。捕获是扩频通信的核心技术,其优劣直接影响应答机的技术指标,研究高性能的捕获技术是扩频通信中的热点。捕获灵敏度和捕获时间是捕获技术中的两大重要参数,但两者存在矛盾,应答机设计一般需在两者间折中,在一定的捕获时间内(通常为10s)提高捕获灵敏度[1-2]。在该捕获时间内,目前国内测控应答机捕获灵敏度一般能达到-122dBm。此外,匹配滤波器捕获的原理研究已相对成熟,但其硬件实现难度较大,故还未用于工程实践。随着近年来硬件工艺的进步和计算机技术的高速发展,应用匹配滤波器进行捕获算法硬件实现可成为现实。

本文对在一定的捕获时间(10s)内一种捕获灵敏度优于传统指标的捕获算法的设计和实现进行了研究。

1 捕获算法

1.1 基本原理

在扩频通信中,常采用直接序列扩频方式对调制数据进行扩频。测控应答机为接收地面站发送的上行遥控和测距数据,就必须复现调制该数据的伪随机码,将复现的伪码与输入伪码在不同相位差上作相关运算使两者同步,从而实现对遥控和测距数据的解扩,此即伪码捕获。另外,因高速运动的中继卫星与用户星的中继终端间存在径向移动,故载波会出现多普勒频移效应。测控应答机接收信号时,经过射频部分模拟下变频和中频部分数字下变频后,其频率值并不为零,而是在零频的基础上增加了一个多普勒频移。为完成对遥控和测距数据的解调,必须搜索到相应多普勒频移的数值,此为载波捕获。因此,扩频信号捕获是一个二维捕获过程,捕获目的是使本地复现码和接收扩频信号的码保持同步(相位差小于1个码元宽度),且收发码的时钟频率基本一致,同时使载波相互对准,实现输入信号与本地信号的粗同步[3]。其中,完成伪码捕获主要是将本地复现码与接收扩频信号做相关运算,利用伪随机码的自相关和互相关特性实现码同步;载波捕获可采用FFT运算估计频率,也可采用频率扫描方式。

1.2 多段匹配滤波器捕获算法数学模型

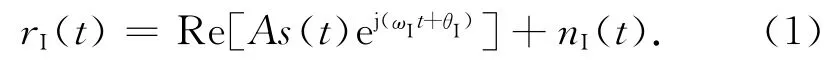

在直接序列扩频系统中,考虑单用户工作时,可将其他用户的扩频信号视作多址干扰,等效为高斯噪声的累加。则理想高斯信道中,接收机接收的中频信号可表示为

式中:s(t)为基带信号波形;A为信号幅值;ωI,θI分别为发送信号的载波频率和相位;nI(t)为单边功率谱密度为N0的加性高斯白噪声[4]。接收信号正交下变频后可得

式中:Δω,θ分别为载波剩余频差和剩余相差;n(t)为复高斯噪声。双边功率谱密度为N0/2,且E[n(τ1)n(τ2)]=N0δ(τ1-τ2)。

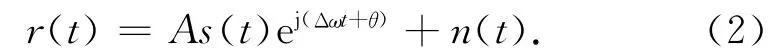

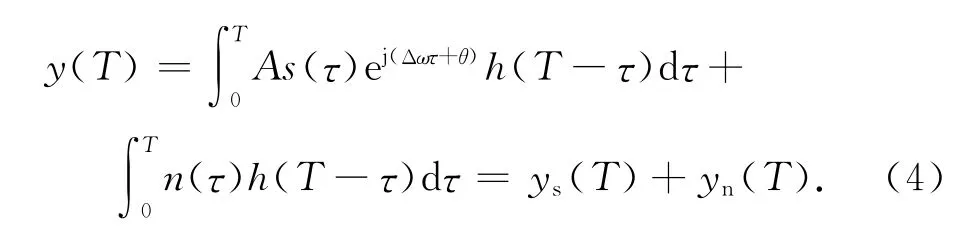

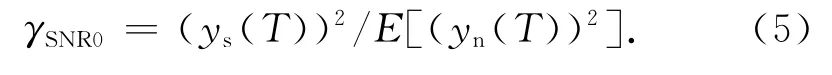

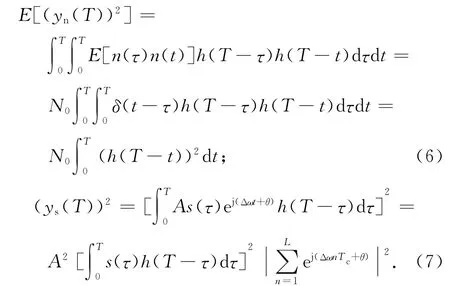

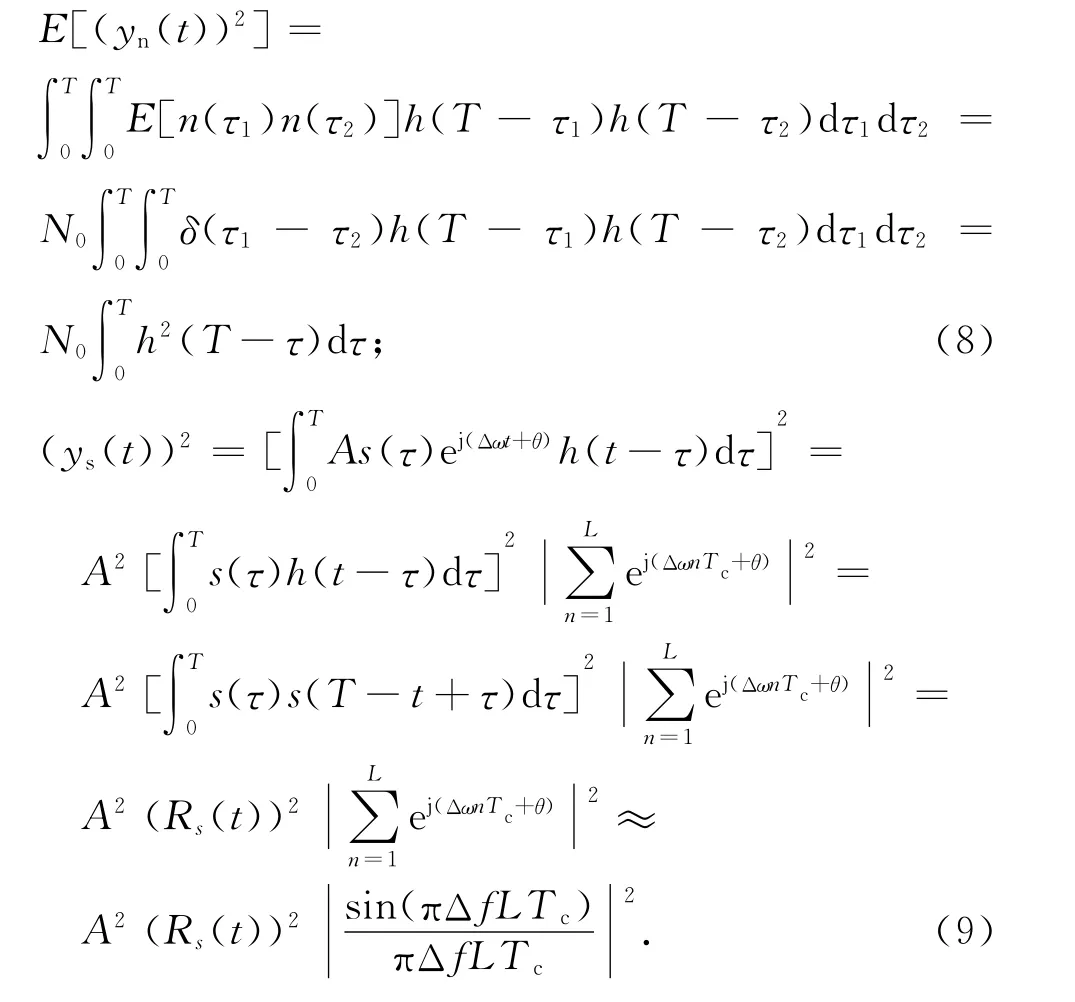

对式(2)信号进行匹配滤波,可得

式中:h(t)为匹配滤波器的传递函数;ys(t),yn(t)分别为信号和噪声分量。在抽样的瞬时t=T,信号和噪声的分量为

定义匹配滤波器输出的信噪比

式中:

此处:T=LTc。其中:L为系数;Tc为扩频码周期。γSNR0的分母取决于h(t)的能量,在分母保持常数的前提下使分子最大化可获得匹配滤波器输出最大信噪比。不考虑载波频偏,由柯西-施瓦茨不等式可知,当h(t)=Cs(T-t)(此处:C为比例系数)时,匹配滤波器可获得最大信噪比。因此,匹配滤波器在时刻t输出的平均噪声功率和信号功率分别为

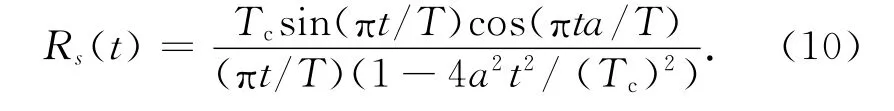

式中:Δf为载波剩余频差;Rs(t)为信号s(t)的自相关函数,其波形可用升余弦函数近似为

由式(9)、(10)可知:当扩频码和载波均取得同步时,匹配滤波器输出的信号功率为最大值。匹配滤波器捕获算法的基本原理是输出功率作为检测判决量,将其与某一门限作比较判断扩频码是否被捕获。

1.3 微弱信号捕获设计

在复杂环境中,信号严重衰落,需提高接收机的灵敏度,以弥补信号强度的损失。接收机灵敏度为式中:Rb为比特速率;Eb/N0为译码器前端的门限信噪比;NF为接收机前端的噪声系数。

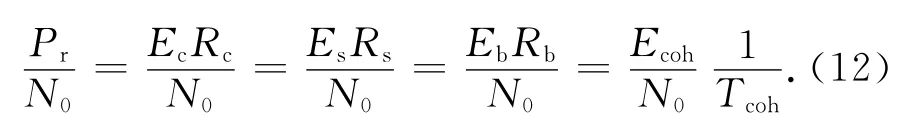

工程设计中提高接收机灵敏度的途径主要有硬件优化和算法优化两种。其中:硬件优化是在射频前端加入低噪声放大器。低噪声放大器能在射频电路中放大天线接收的微弱信号,提高电路的整体增益,因此噪声系数NF一般为2.5~3.5;算法优化时,接收机的灵敏度包括捕获灵敏度和跟踪灵敏度两方面。本文考虑提高捕获灵敏度,有

影响捕获灵敏度的因素主要有相干积分时间Tcoh、非相干累加次数和采用的捕获算法。

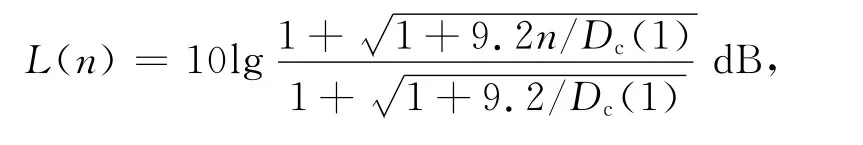

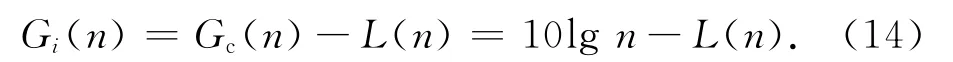

a)相干积分 有效利用了信号和噪声的独立性,对相同的判决符号,可得最大的检测信噪比。一般,相对1ms,nms的附加相干积分增益因此适当增加相关积分时间可得较大的增益。但因存在比特跳变和多普勒频偏,相干积分的长度受限。

b)非相干积分 由相干积分产生的输出获得额外信噪比增益,但非相干积分存在平方损耗

故非相干积分的增益

通常是将两种方法混合使用,即将一组长输入数据分成多个块,并对每块进行相干积分操作。相干积分后,每个输出频率分量均为复数,计算其幅值,将同一频率的所有相干积分的幅值相加,结果是弱信号被增强,由此可获得较高的信噪比。

c)差分相干积分 相干-非相干积分方法存在平方衰减,而差分相干积分在一定程度上抑制了噪声的放大。其基本原理为:相干积分输出的复基带信号经同一相干时间的延迟,取其共轭,与下次相干积分输出相乘;由长时间的累加,输出积分功率。该差分相干积分算法利用了前后不同时段采样数据的噪声独立性,及信号受差分相干积分的影响较小的特性,一定程度抑制了传统非相干积分的平方衰减[5]。

2 捕获算法设计与仿真

2.1 捕获流程

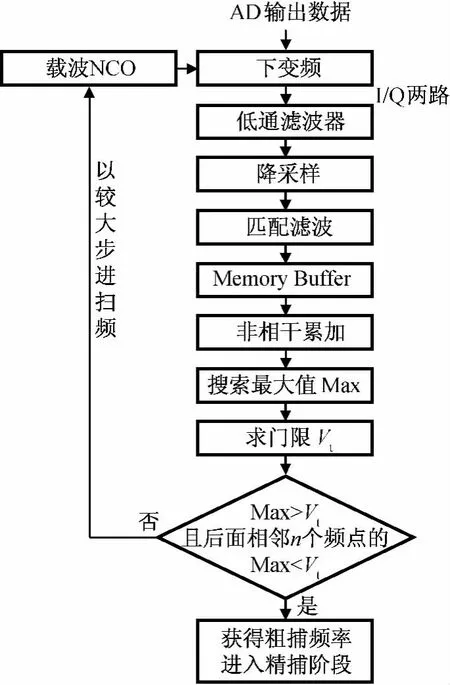

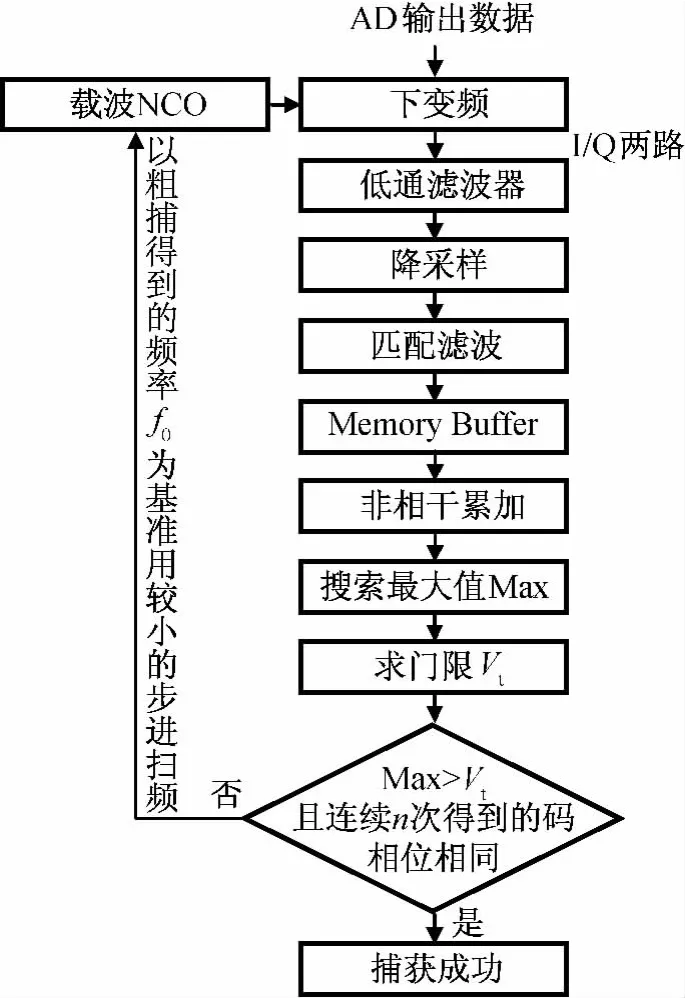

基于相干-非相干的匹配滤波器捕获算法整体流程是:将接收到的中频信号经AD变换后进行下变频处理,变成基带信号;基带信号通过低通滤波器,滤掉信号频谱外的噪声,并进行降采样、匹配滤波、非相关累加、峰值搜索、判决;根据最大值对应的位置得到对应的码相位与载波频率,交跟踪模块,完成捕获。捕获基本流程包括粗捕和精捕两部分,采用粗捕+精捕的扫频方式,以不同的步进对频域进行搜索,这样虽会增加少许捕获时间,但可提高捕获的灵敏度。具体步骤如下:若扫到某个频点时得到的最大值大于粗捕门限,且该频点后相邻的数个频点(实验中选为3个)得到的最大值均未超过门限,则认为该频点即为粗捕频率,以该频点为基准进入精捕阶段。在精捕阶段,以更小的步进在粗捕频率左右扫频,若扫到某频点时连续数次(实验中定为3次)得到的最大值均大于精捕门限,且这数次得到的码相位相同,则认为该频点即为多普勒频偏,捕获成功;否则转入粗捕阶段,继续进行扫频。粗捕和精捕的流程分别如图1、2所示。

2.2 仿真结果

通过射频部分模拟下变频得到中频信号为9.548MHz(不考虑多普勒频偏),多普勒频偏范围14kHz,扩频码速率1.023Mc/s,码周期长1 023,经AD对其进行采样量化,采样频率38.192MHz,将得到的数据作为算法仿真的初值。分别用基于非相干累加的FFT捕获算法、基于差分相干的FFT捕获算法、基于差分非相干的FFT捕获算法和基于相干-非相干的多段匹配滤波器捕获算法进行仿真。

a)基于非相干累加的FFT捕获算法

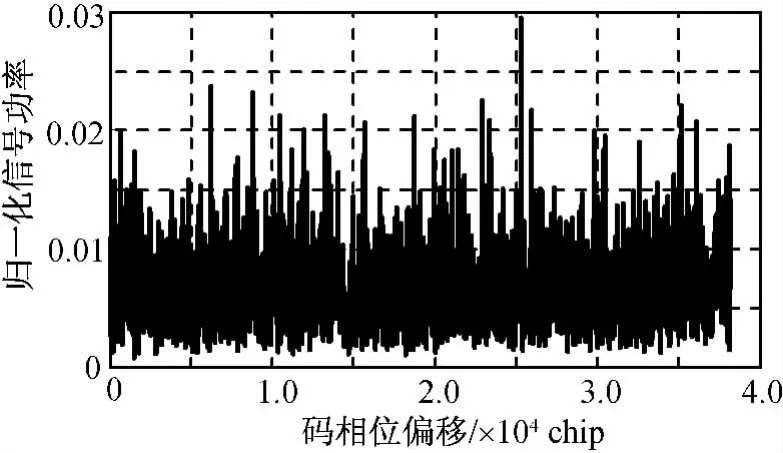

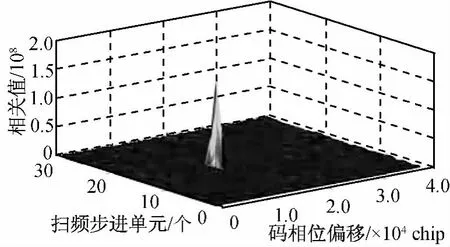

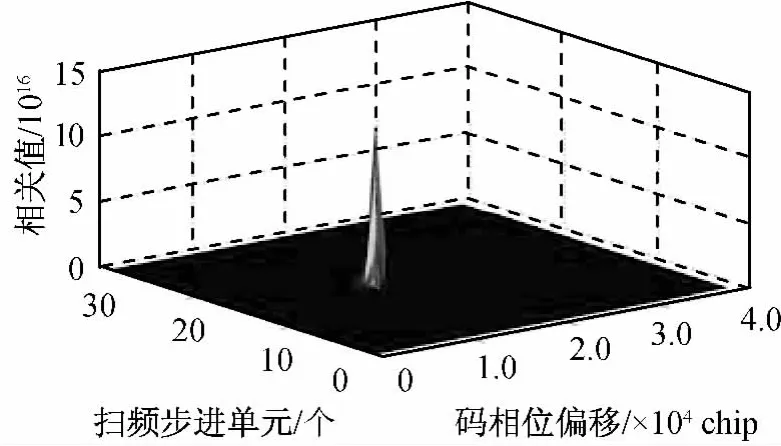

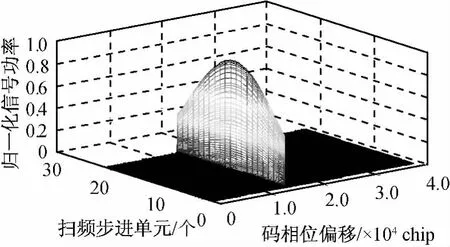

扫频步进0.5kHz,非相干累加7次,仿真结果如图3~5所示。

图1 粗捕基本流程Fig.1 Flowchart of coarse-acquisition

图2 精捕基本流程Fig.2 Flowchart of fine-acquisition

由图3可知:在扩频码和载波均取得同步(码偏13 404个码片,多普勒频偏500Hz)时,能量有最大峰值。由图4、5可知:在扫频频点为9.547 5MHz时,利用扩频码的相关特性,本地码和接收数据对齐时能量有最大值,而在码未对齐或多普勒频偏没有得到补偿时能量值均很小。

图3 FFT捕获算法非相干累加7次所得相关值Fig.3 Correlation value by incoherent accumulate 7times with FFT acquisition algorithm

图4f=9.547 5MHz时非相关累加7次所得相关值Fig.4 Correlation value of incoherent accumulate 7times atf=9.547 5MHz

图5f=9.544 5MHz时非相关累加7次所得相关值Fig.5 Correlation value of incoherent accumulate 7times atf=9.544 5MHz

b)基于差分相干/差分非相干的FFT捕获算法

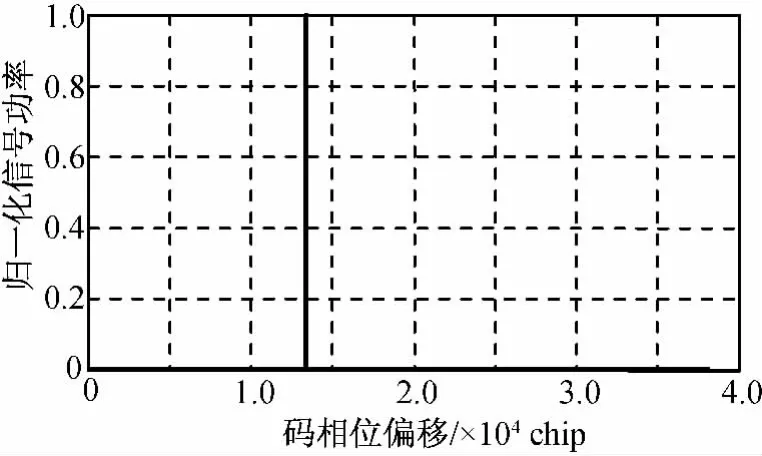

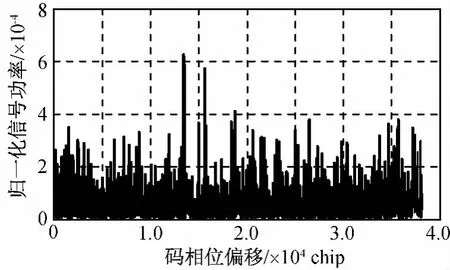

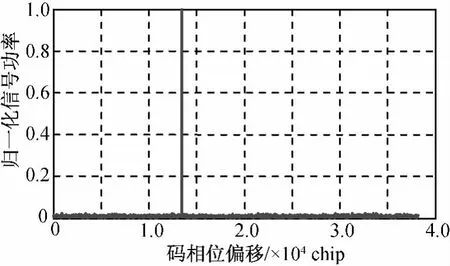

扫频步进0.5kHz,取8个码周期的数据进行差分相干计算,结果如图6~8所示。

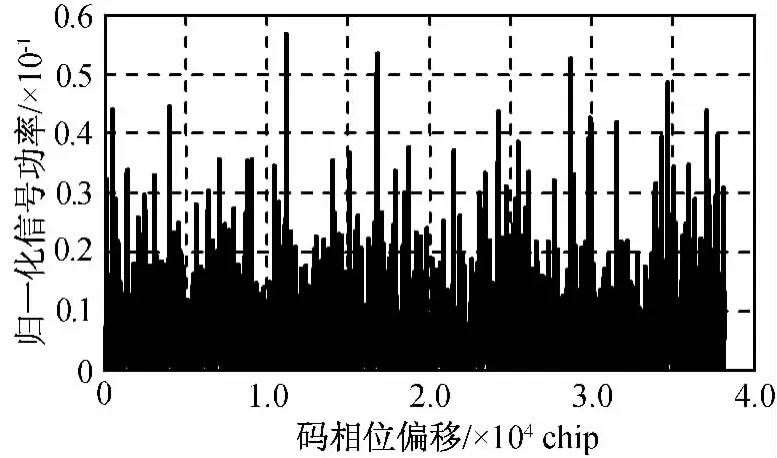

扫频步进为0.5kHz,取8个码周期的数据进行差分非相干计算,结果如图9~11所示。

图6~11验证了基于差分相干和差分非相干的FFT捕获算法可行性。

c)基于相干-非相干的多段匹配滤波器捕获算法

图6 FFT差分相干捕获算法所得相关值Fig.6 Correlation value of differential coherent with FFT acquisition algorithm

图7f=9.547 5MHz时差分相干所得相关值Fig.7 Correlation value of differential coherent atf=9.547 5MHz

图8f=9.544 5MHz时差分相干所得相关值Fig.8 Correlation value of differential coherent atf=9.544 5MHz

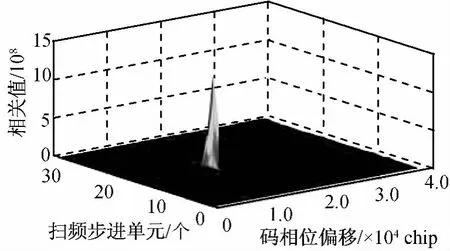

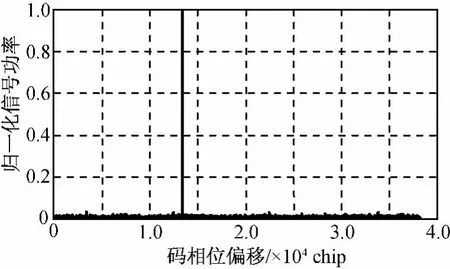

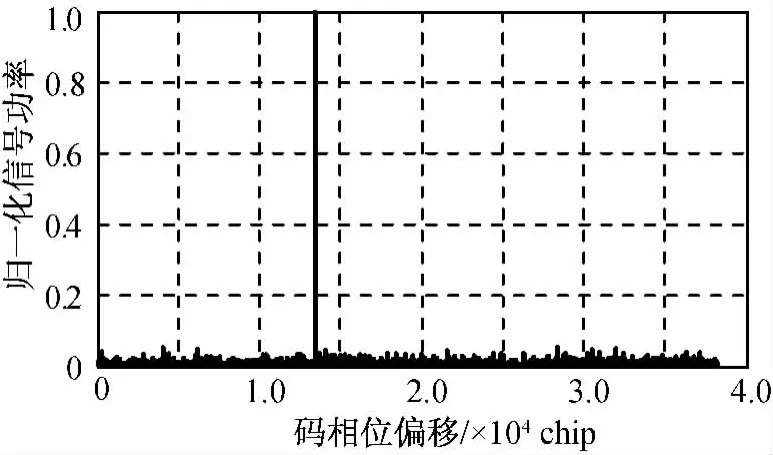

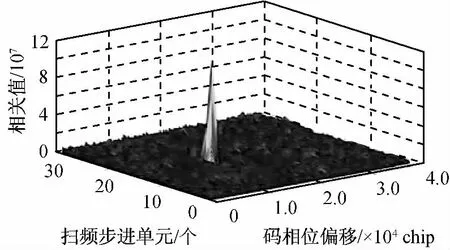

每个码周期(1ms)的采样点数38 192,将匹配滤波器分为8段,每段有数据4 774个,扫频粗捕步进0.5kHz,精捕步进50Hz,非相干累加7次,仿真结果如图12~14所示。

图12~14可验证基于非相干累加的多段匹配滤波器捕获算法的可行性,该算法可较好地抑制噪声,提高信噪比。

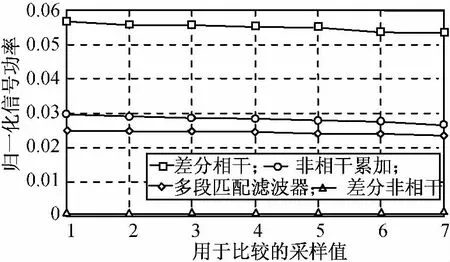

归一化各种算法所得的能量值,分别在各种算法得到的噪声能量中取7个较大值比较噪声抑制情况,结果如图15所示。

图9 FFT差分非相干捕获算法所得相关值Fig.9 Correlation value of differential incoherent with FFT acquisition algorithm

图10f=9.547 5MHz时差分非相干所得相关值Fig.10 Correlation value of differential incoherent atf=9.547 5MHz

图11f=9.554 5MHz时差分非相干所得相关值Fig.11 Correlation value of differential incoherent atf=9.554 5MHz

由图15可知:在相同条件下,基于非相干累加的FFT捕获算法可将噪声的能量抑制在0.03以下;基于差分相干的FFT捕获算法可抑制在0.06以下;基于差分非相干的FFT捕获算法性能优于前两者,可将噪声能量抑制在0.000 7以下,该方法更适于用于微弱信号的捕获,但其硬件设计较复杂;基于多段匹配滤波器的捕获算法抑制能力介于差分非相干和非相干累加的FFT捕获算法间,但该算法的硬件实现相对简单,且使用折叠匹配滤波器实现捕获算法可节约较多的硬件资源,因此综合考虑各种算法的性能和硬件实现的可行性,选用该算法较理想[6]。

图12 基于多段匹配滤波器捕获算法粗捕所得相关值Fig.12 Correlation value of incoherent accumulate 7times with multi-bank matched filter coarse-acquisition

图13 基于多段匹配滤波器捕获算法精捕所得相关值Fig.13 Correlation value of incoherent accumulate 7times with multi-bank matched filter fine-acquisition

图14 精捕所得相关值(精捕频率f=9.547 5MHz)Fig.14 Correlation value of fine-acquisition atf=9.547 5MHz

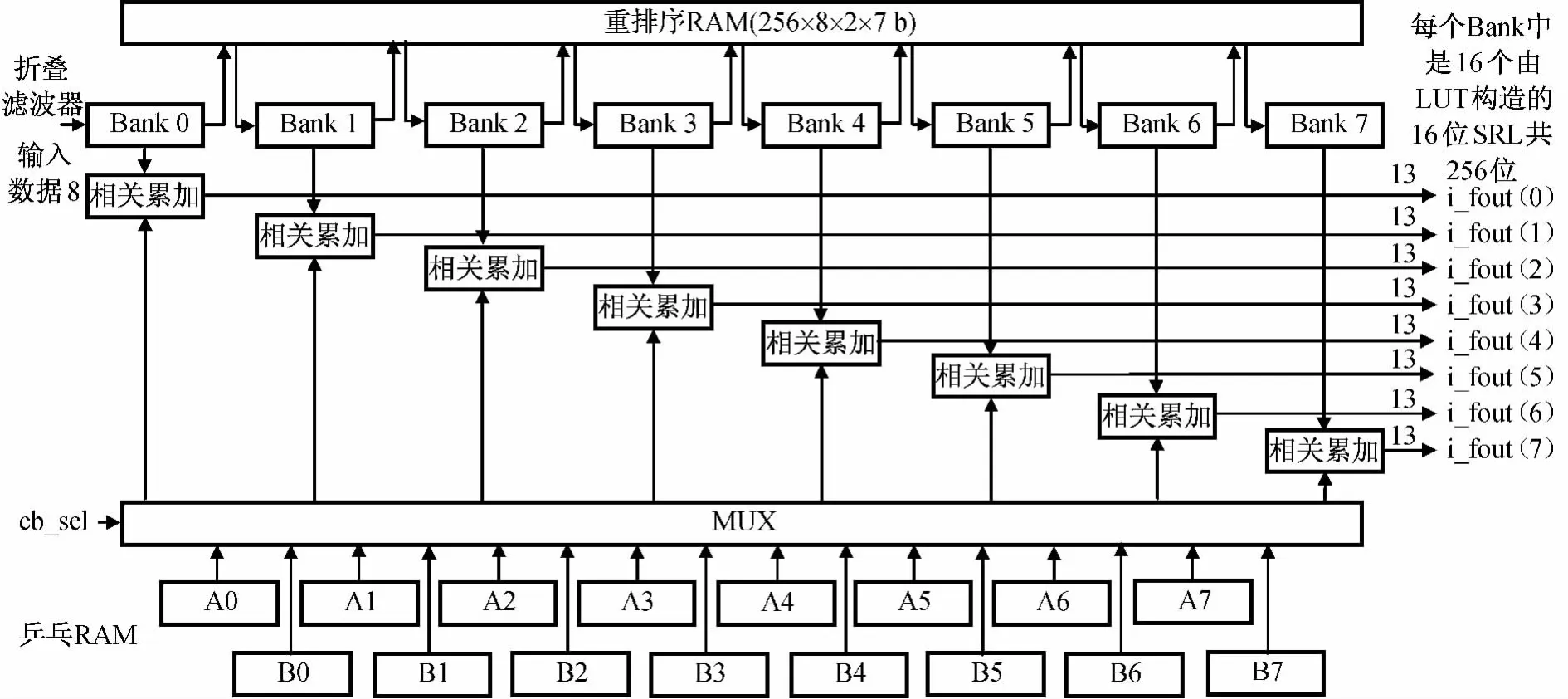

3 多段匹配滤波器硬件实现

多段匹配滤波器是该算法的核心模块,它用于将经降采样的I/Q两路数据与本地码进行分段相关累加。多段匹配滤波器的设计主要包括输入数据缓存、数据处理、输出数据缓存和控制模块四部分。

图15 四种捕获算法的噪声抑制比较Fig.15 Noise suppression of four acquisition algorithms

3.1 硬件设计

3.1.1 控制模块

输入和输出数据缓存模块中,因折叠滤波器工作的时钟要求为输入数据速率的16倍,导致FPGA中存在多时钟域;数据处理模块中,利用折叠滤波器装载接收到的降采样数据,用分布式RAM装载本地码。因数据在折叠滤波器中流过的过程中,本地码也会流入,需要被保存,故本地码的装载需做成乒乓RAM的形式。又由于有序的数据经过折叠滤波器后,顺序会被打乱,如将上个滤波器的输出数据直接输入下个折叠滤波器会导致数据与本地码的码相位不匹配,因此需在各折叠滤波器间构造重排序RAM。

由上述分析可知:多段匹配滤波器设计需解决多时钟域、乒乓RAM、折叠滤波器,以及重排序RAM。控制模块功能是产生相关信号以控制输入数据缓存中的异步FIFO、数据处理模块中的乒乓RAM对本地码的装载和读取、折叠滤波器的移位、相关累加、重排序RAM的存取,以及对相关累加结果输出的时序调整。

3.1.2 输入数据缓存

在前处理中使用半码片标志作为降采样的使能信号,降采样后的数据传输速率为10.23×2=20.46Mb/s。因折叠滤波器工作时钟要求为输入数据速率的16倍,故匹配滤波器的工作时钟为20.46×16=327.36MHz,在实际设计中通过DCM产生频率为334.238MHz的时钟信号供给匹配滤波器正常工作,但同时就会导致多时钟域问题。为此,需利用异步FIFO对数据进行缓存,具体设计如下。

a)因输入I/Q两路数据为8位,本地码为1位,将3路数据组合输入,此外每个bank需数据256个,故需创建一个256×(8+8+1)bit的RAM。

b)输入数据以input_en_fi(mf_en)为时钟存储入RAM,当数据写满RAM时产生sect_st信号,通知匹配滤波器,开始对RAM中的数据读取。

c)数据读取以334.238MHz的时钟为基准,每个时钟上升沿读取1次,而地址是每16个时钟增加1,故每16个334.238MHz的时钟输出1个新数据,以满足匹配滤波器正常工作对输入数据的要求。

在异步FIFO设计中,由于读和写的时钟频率确定,只有选取合适的时间产生sect_st才可使RAM不会被读空或写满。实际设计中,选取当写地址为244时触发产生sect_st信号,即可保证异步FIFO的正常工作。

3.1.3 数据处理

数据处理模块是多段匹配滤波器的核心,是硬件设计中最难实现的模块,主要完成本地码和接收数据的相关累加,其中涉及数折叠滤波器、本地码的装载和读取、重排序RAM,以及相关运算。数据处理模块的内部实现框图如图16所示。

图16 数据处理模块内部实现框图Fig.16 Block diagram of data processing module

3.1.4 输出数据缓存

与输入缓存模块作用相反,输出缓存模块是将在匹配滤波器工作时钟(334.238MHz)作用下数据处理的结果以外部时钟为基准输出至下一模块,并对应调整使能信号的时序。

3.2 硬件调试结果

FPGA选用Xilinx公司的Virtex4芯片,由CORTEX产生70MHz信号,经上变频得到射频信号作为接收机的输入,对基于相干-非相干的多段匹配滤波器捕获算法进行调试验证,结果为在5s(<10s)的捕获时间内,捕获灵敏度可达-126dBm,较传统指标提高了4dB。

4 结束语

本文通过对几种捕获算法进行性能仿真,综合考虑性能和硬件实现的可行性,对基于相干-非相干的多段匹配滤波器捕获算法的核心模块进行硬件设计与实现。这种时域并行频域串行的捕获算法,利用分段匹配滤波器来消除比特跳变的影响,此外,通过“扫频”的方式来进行频率搜索,经过“精捕”可提高捕获的灵敏度。硬件调试结果证明了该算法的实用性。

[1] ZHUANG W.Noncoherent hybrid parallel PN code acquisition for CDMA mobile communications[J].IEEE Transactions on Vehicular Technology,1996,45(4):643-656.

[2] KWON H M,TARAFDER M R.Noncoherent PN code acquisition with data modulation-on under static and fading environments[C]//:Military Communications Conference.[s.l.]:IEEE,1996(3):998-1002.

[3] 田日才.扩频通信[M].北京:清华大学出版社,2007:177-178.

[4] 张爱民.直扩系统中基于DMF的伪码捕获和窄带干扰技术研究[D].长沙:国防科学技术大学,2008.

[5] 刘海涛.高灵敏度GPS/Galileo双模导航接收机的研究与开发[D].长沙:国防科学技术大学,2006.

[6] CHAPMAN K, HARDY P, MILLER A.XAPP212:CDMA matched filter implementation in virtex devices[EB/OL].[2011-10-22].www.xilinx.com/support/documentation/application_notes/xapp212.pdf.