基于FPGA的高精度正弦波信号源设计

朱 枫,陈跃东,舒圣焱

基于FPGA的高精度正弦波信号源设计

朱 枫,*陈跃东,舒圣焱

(安徽工程大学,电气传动与控制重点实验室,安徽,芜湖 241000)

提出了一种基于FPGA的高精度正弦波信号源设计方案。该信号源采用直接数字合成的方式(DDS),以及使用FPGA、D/A芯片和滤波器等来实现。该设计的信号源输出频率范围为200 Hz-100 kHz,幅值范围为0-5 V。实验结果表明,该信号源相位、幅值、频率均可调,具有精度高、灵活性好等优点。

FPGA;正弦波;DDS;可调;精度高

0 引言

高分辨率、高精度的信号源一直广泛地应用于通信、电子等领域,大多数检测工作更是需要信号源作为激励。信号源设计一般均采用直接数字频率合成(DDS)的方式。现阶段,波形产生技术已进入DDS集成芯片阶段[1],但现有市场的DDS专用芯片可能会出现输出频率单一,幅值大小不可调等局限性,无法灵活使用。

本文提出一种基于FPGA的正弦波信号源设计方案。该方案以FPGA作为主控制芯片,设计的信号源输出频率范围为200 Hz-100 KHz,幅值范围为0-5 V,信号源相位、幅值、频率均可调。该信号源的幅值精度为0.024%,可用作各种高精度要求的输入激励信号。

1 正弦波信号源设计整体框图

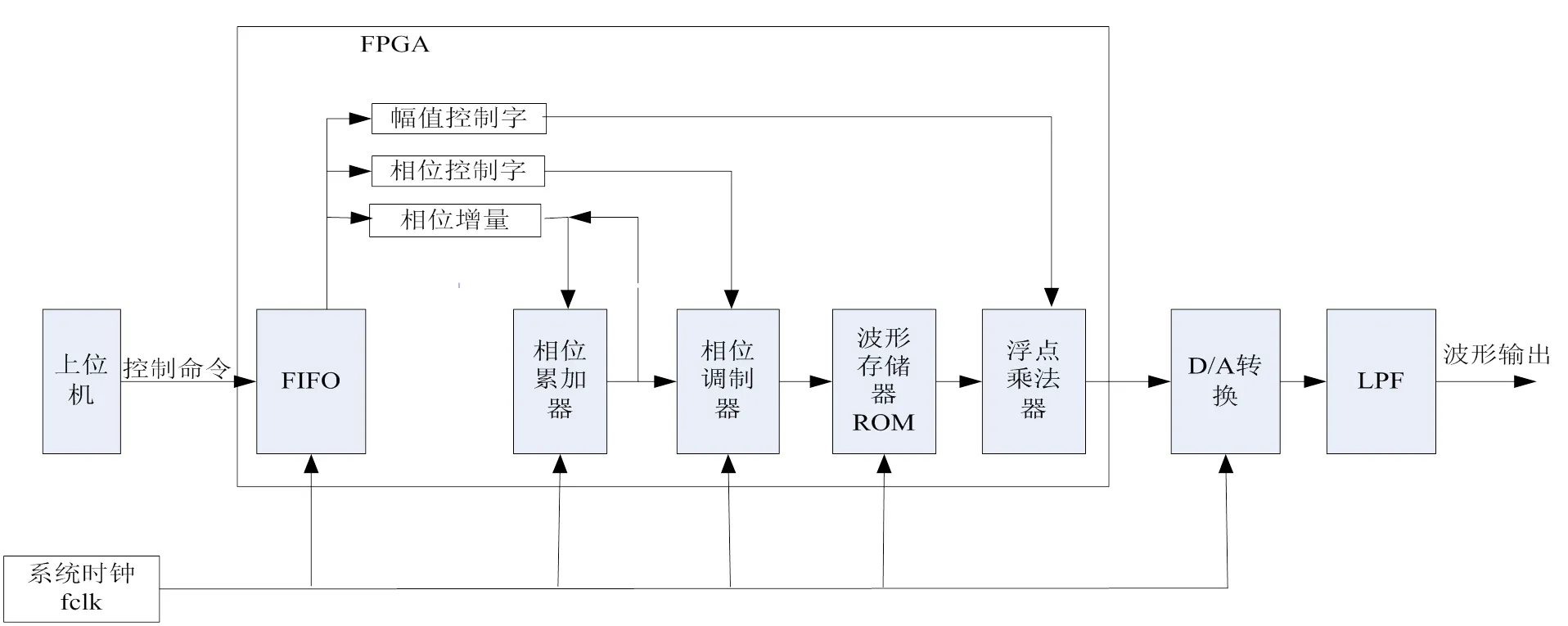

本设计的信号源采用直接数字频率合成的方式[2-3],主要结构由上位机、FIFO、相位增量K、相位控制字、幅值控制字、相位累加器、相位调制器、波形存储器、浮点乘法器、D/A转换器、低通滤波器LPF实现功能。其中FIFO、相位增量K、相位控制字、幅值控制字、相位累加器、相位调制器、波形存储器、除法器均由FPGA芯片实现,具体连接实现关系如图1所示。本设计对各模块的参数进行优化,保证信号源的高精度性。各模块的具体功能将在设计原理中介绍。

图1 正弦波信号源系统框图

2 正弦波信号源软硬件设计

2.1 正弦波信号源设计原理

本信号源利用FPGA的IP生成先进先出队列FIFO[4](First Input First Output)用于设计需要。FIFO采用同步逻辑,使系统稳定性更高。FIFO可缓存数据,本设计采用FIFO缓存解码命令,其中FIFO通过设置空满标志位,来提示何时需要读写数据。FIFO还可以用于不同接口的不同数据位的转换,以及减少亚稳态概率。

对于N位相位累加器[5]来说,直接数字频率合成是将一个时钟周期的正弦波分为2N量值,相位增量K也即是相位步进量,是相位累加器的增量;相位累加器在系统时钟fclk下,每个时钟的都会累增一个相位增量K;输入的相位控制字可以调整正弦波信号源的初始相位;相位累加器的累加值加上相位控制字可作为波形存储器的访问地址,从而读取波形的数字值,读取的波形数字值,相位累加器的累加值在一个正弦波周期后会重新从0开始,如此反复。而通过一个浮点乘法器,数字波形信号乘以幅值控制字AP,即可达到改变幅值的作用。继续输出经过D/A转换器再经过低通滤波器即可变为高精度的、平滑的正弦波信号。

2.2 FPGA实现模块

本设计的FPGA芯片选择ALTERA公司的ep4ce6e22c8n,作为ALTERA的Cyclone iv系列的产品,ep4ce6e22c8n以极为低廉的价格实现了高精度信号源设计的要求,而且功耗更低,处理速率更快。

该信号源设计的波形存储器ROM储存的是正弦波信号的采样值,本设计共选择14位采样点数值,即为214个采样值放入波形存储器ROM空间,以查找表的形式来读取相应的采样值,从来达到输出正弦波数字采样值的要求。具体存储方法是可以用mif文件存储正弦波采样数值,在工程中直接查找调用。

DDS的参数有:相位增量K、相位控制字PW、输出频率out以及频率分辨率△,其中有out=·/2,△=/2,fclk为系统时钟,系统时钟由50M晶振产生,N为相位累加器的位宽,本设计N取值28,则该信号源的分辨率为:

△=/2=50·106/228=0.186Hz

一般来说,△越小,频率精度越高,理论上△和N成反比,和fclk成正比[6],但考虑系统的复杂度以及成本,相位累加器位宽N不宜过大,而系统时钟太小也会导致系统整体效率变低。综合考虑,将系统时钟定为50MHz,将相位累加器位宽定为28bit。

由out=·/2,可推出,=out·2/。本设计的信号源输出频率为200 Hz-100 KHz,则最大步进量max的值为:

max=out·2/=100·103·228/50·106=0X83126;

最大输出频率的波形采样点个数为:228/max=500,可以满足基本要求。

由上述介绍可知相位增量K的位宽为20 bit,可以达到输出频率为200 Hz-100 KHz的要求。ROM位宽为14位,相位控制字PW的位宽可以和ROM的位宽相同为14位。由上述介绍可知,ROM内存的限制,存储的容量定为214个值,为此28位相位累加器选择高14位作为地址输出,配合相位控制字即可实现寻址要求。

FPGA模块的设计采用原理图设计方式,在quartus II 11.0下实现。图2为FPGA原理图设计图,其中datain[63..0]为控制信号,rst为复位,clk为系统时钟,DA_datain[11..0]为FPGA输出,inst为FIFO,inst1为相位累加器,inst2为波形存储器ROM,inst3为相位调制器,inst4为浮点乘法器。本设计波形存储器的ROM存储为DA输出电压最大值即5V的正弦波采样点。这样处理的优点是幅值调节均为缩减操作,从而使浮点乘法器的原理更为简单。本信号源的浮点乘法器实现幅值调节的原理是:查找ROM后的数值乘以16位幅值控制字后,右移16位,最后输出即为DA转换的输入数值。

图2 FPGA原理图设计

为了验证系统的可行性,本设计在modelsim软件下进行仿真,图3为控制信号仿真图形,该仿真对应为频率6250 Hz的正弦波。其中,fk为相位增量、addr为ROM地址、clk为时钟、dataout为波形存储器ROM查找表数据输出,pw为相位控制字,仿真结果符合上述所述DDS相关参数计算结果。

图3 modelsim下控制信号仿真图形

2.3 D/A转换器

D/A转换是将数字信号转为模拟信号[7],本设计D/A芯片选择的是高速并行12位芯片的TLV5619。TLV5619工作电压为2.7~5.5 V,位数为12,电压输出类型,单输出通道,接口方式是并行基准,外部功耗4.300MV,并行接口12位D/A转换器。TLV5619的输出电压为0~5.1 V,因而12位的D/A转换,幅值分辨率为△h=5.1/212=1.24×10-3V,可以达到高精度的要求。

该D/A转换器的电路连接图如图4所示。

图4 D/A转换电路

2.4 低通滤波器

为了得到更为平滑的正弦波信号,需要采用滤波处理,本设计的滤波器采用巴特沃斯二阶滤波器,电路连接如图5所示,低通滤波截止频率满足:,其中n为滤波器阶数,计算得到截止频率为:

满足设计要求。

图5 滤波电路

Fig.5 Filter circuit

3 无杂散动态分析

系统的时钟频率为50 MHz,输出频率范围为200 Hz-100 kHz,相位累加器的位数N为28位,频率分辨率为0.186 Hz。本设计为了节约资源,相位累加器用高A位寻址,从而会导致相位截断误差[8],无杂散动态范围的SFDR[9]满足:

同时满足的条件还有:

4 实验结果分析

本设计信号源硬件为实验室制作的信号源电路板。本次设计测试仪器为台湾固纬GWINSTEK GDS2102数字示波器,该示波器频宽为100 MHz,2输入通道,1 GSa/s即时取样率以及25 GSa/s等效取样率25000点之记忆体长度5.6寸TFT彩色荧幕,支持USB HOST/DEVICE:支持USB存储卡(U盘),USB印表机等。信号源电路板输出信号接至示波器CH1接口,通过示波器显示波形和频率等参数。硬件测试平台如图6所示。

图6 信号源测试平台

将实验输出的正弦波形信号接入示波器的CH1口,观察波形和相关数据。如图7中a和b所示,示波器显示的波形分别是正弦波信号源产生的200 Hz、2 V信号和90 KHz、3 V信号,图中的波形均十分平滑、稳定。

a) 200Hz,2V正弦波

b) 90KHz,3V正弦波

图7 正弦波信号源示波器观测图

Fig.7 Oscilloscope observation figure of the sine wave signal source

为了进一步分析硬件输出波形频率的误差,做了频率测量数据统计,如表1所示,本设计误差率计算公式为。表中数据为控制命令要求的频率和实际示波器输出的频率对比。

表1 测量频率数据误差统计

由表1的数据统计可以得出结论:本设计的信号源在频率低于200 Hz时,误差较大,这是因为分辨率固定为0.186,误差频率为其倍数,根据误差计算公式,低频时,分母较小,数据误差及外界影响很容易让误差率偏大;在频段200 Hz-1 KHz,误差递减,这是因为频率设定值较小,前述频率分辨率计算值固定,采样点递增,从而误差率递减;在中频5 KHz-10 KHz,输出波形的误差最低,误差率小于0.05%;在较高频20 KHz-100 KHz误差递增,但均小于0.5%,这是由于步进值变大,采样点依次变少,从而精度受到影响。同时需要指出的是,测量值为数字示波器通过采样检测得到,测量过程中数据小幅度变更,本次测量值为出现概率较大的数据;还需指出的是由于外界等干扰,所测得数据可能存在一定测量误差,但对实际应用无较大影响。从数据上可知,设计的信号源基本符合高精度的标准,可以作为高精度的信号输入源进行应用。

4 小结

随着现代电子科技不断发展,电子产品尤其是高精度开发产品的检测对信号源的要求越发严格。为了迎合市场要求,设计了一种基于FPGA的正弦波信号源,该信号源设计采用最为常用的直接数字频率合成(DDS)的方法。信号源的主控芯片是FPGA,FPGA具有高速运行速率,且具有集成度高、逻辑单元灵活等特点[10],相关功能设计是在ALTERA公司的quartus II 11.0软件下完成。

设计的信号源频率范围为200 Hz-100 KHz。精度高:幅值精度为0.0124 V;实际波形测量频率误差小于0.5%;无杂散动态范围大于84.28 dB。信号源基本达到较高精度的要求,可以作为高精度的激励源,具有较高的实际应用价值。

参考文献:

[1] Cordesses L. Direct digital synthesis: A tool for periodic wave generation (Part 2)[J]. Signal Processing Magazine, IEEE, 2004, 21(5): 110-112.

[2] 张凯琳,苏淑靖,刘利生,等.基于FPGA的DDS多路信号源设计[J]. 电测与仪表,2011,48(543):63-65.

[3] 曹志锋,王小华,程欢. 基于FPGA+DDS的正弦信号发生器的设计[J]. 微型机与应用,2012,31(14):90-92.

[4] 张莹,阳璞琼. FIFO可靠性设计与研究[J]. 微处理机,2008(6):170-172.

[5] 刘韬. 基于DDS频率源的设计与实现[J]. 电子科技, 2013,26(1):56-58.

[6] 余勇,郑小林. 基于FPGA的DDS正弦信号发生器的设计和实现[J]. 电子器件,2005,28(3):596-599.

[7] 梁孟享,胡聪,盘书宝. 基于FPGA的高性能信号源模块设计[J]. 研究与开发,2012,31(4):64-67.

[8] 曹郑蛟,滕召胜,李华忠,等. 基于FPGA的DDS信号发生器设计[J].计算机测量与控制,2011,19(12): 3175-3177.

[9] 刘艳茄,田书林,王志刚,等. 一种基于Farrow滤波器的并行采样时间误差校正[J]. 电子测量与仪器学报,2010, 24(1):50-54.

[10] 高士友,胡学深,杜兴莉,等. 基于FPGA的DDS信号发生器设计[J]. 现代电子技术,2009,(343):35-37.

DESIGN OF HIGH-ACCURACY SINE WAVE SIGNAL GENERATOR BASED ON FPGA

ZHU Feng,*CHEN Yue-dong, SHU Sheng-yan

(Anhui Polytechnic University, Anhui Key Laboratory of Electric Drive and Control, Wuhu, Anhui 241000, China)

We propose a design of high-accuracy sine wave signal generator based on FPGA, which is completed by using direct digital synthesis (DDS), the FPGA, D/A chip, filter and etc. The output frequency of the designed signal source ranges from 1 Hz to 100 kHz and its amplitude ranges from 0V to 5 V. With its phase, amplitude and frequency adjustable, the signal source has the advantages of high accuracy and good flexibility.

FPGA; Sine wave; DDS; Adjustable; High-accuracy

1674-8085(2015)01-0056-05

TN98

A

10.3969/j.issn.1674-8085.2015.01.011

2014-03-10;修改日期:2014-10-12

国家重点基础研究发展计划(973计划)课题项目(2013CB733204);安徽高校省级自然科学研究重点项目(KJ2013A041);安徽省大学生创新创业训练计划项目(AH201310363005)

朱 枫(1990-),男,安徽合肥人,硕士生,主要从事先进传感与检测技术研究(E-mail:963317613@qq.com);

*陈跃东(1956-),男,湖北宜昌人,教授,硕士,硕士生导师,主要从事系统检测与信号处理研究(E-mail:ydchen@ahpu.edu.cn);

舒圣焱(1994-),男,安徽芜湖人,安徽工程大学电气工程学院2011级本科生(E-mail:1121077924@qq.com).