基于FPGA的红外遥控彩灯控制器的设计

严丰 陈学英

摘 要: 设计一种基于现场可编程逻辑器件FPGA的红外遥控彩灯多模式显示控制系统。具有成本低、性能可靠、扩展性好等优点。详细介绍了系统的电路结构,提出一种由SC9148B红外发射芯片及外围电路作为发送器,HS0038B红外一体化芯片作为接收器,FPGA作为核心控制器的红外遥控系统的构建方法。该系统通过时序仿真与FPGA逻辑验证,结果表明,该设计能很好地实现彩灯红外遥控信号的解码控制、键值信号存储及译码、彩灯多模式显示等功能。

关键词: 红外遥控; FPGA; 解码; 显示

中图分类号: TN929.1?34 文献标识码: A 文章编号: 1004?373X(2015)19?0040?03

Abstract: A multi?mode coloured?lantern display control system with infrared remote control based on FPGA was designed, which has the advantages of low?cost, reliable performance and excellent scalability. The circuit structure of the system is introduced in detail. A construction method of infrared remote control system is put forward, which takes the infrared emission chip SC9148B and peripheral circuit as the transmitter, the integrated infrared chip HS0038B as the receiver, and FPGA as the core controller. This system was verified by time sequence simulation and FPGA logic validation. The actual results show that this design can realize the functions of decoding control of infrared remote control signal for the coloured lanterns, storage and decoding of the key value signal, and multi?mode coloured?lantern display.

Keywords: infrared remote control; FPGA; decoding; display

现代电子技术迅猛发展,传统的设计方法正逐步退出历史舞台,基于可编程[1]逻辑器件FPGA的芯片设计技术逐步成为电子系统设计的主流。传统的红外遥控彩灯控制系统的信号解码多采用单片机或ARM实现,其编码器和解码器的设计均为软件方式,实际应用中容易受到外界干扰而程序跑飞,且软件解码为串行运算,响应速度慢,CPU资源占用多,系统可靠性较低。相比之下,基于并行处理的FPGA具有非常显著的优势,其速度快、系统集成度高、抗干扰能力强、工作稳定可靠、设计更改方便。本文采用市场主流的FPGA技术实现彩灯的红外遥控,充分融合了通信技术、数字逻辑处理技术及FPGA技术[2]在工程实践中的一体化应用。

1 系统设计原理

红外遥控系统[3]一般主要由红外发射器、红外接收器和核心解码微控制器及其外围电路等四部分构成。本设计中,在数十米范围内,当按键被按下时,红外发射器产生与指令/按键对应的控制信号,并对控制信号进行识别/编码,经过调制后,通过红外发射管将串行数据以红外光的形式发送出去。接收器接收来自发送器的红外信号,并对接收到的信号进行检波、放大、滤波解调、整形等,最后从载波上恢复出基带信号。还原后的基带信号被送入核心解码控制器FPGA,转换为相应的控制信号完成彩灯控制。

2 红外发射电路设计

2.1 红外通信协议

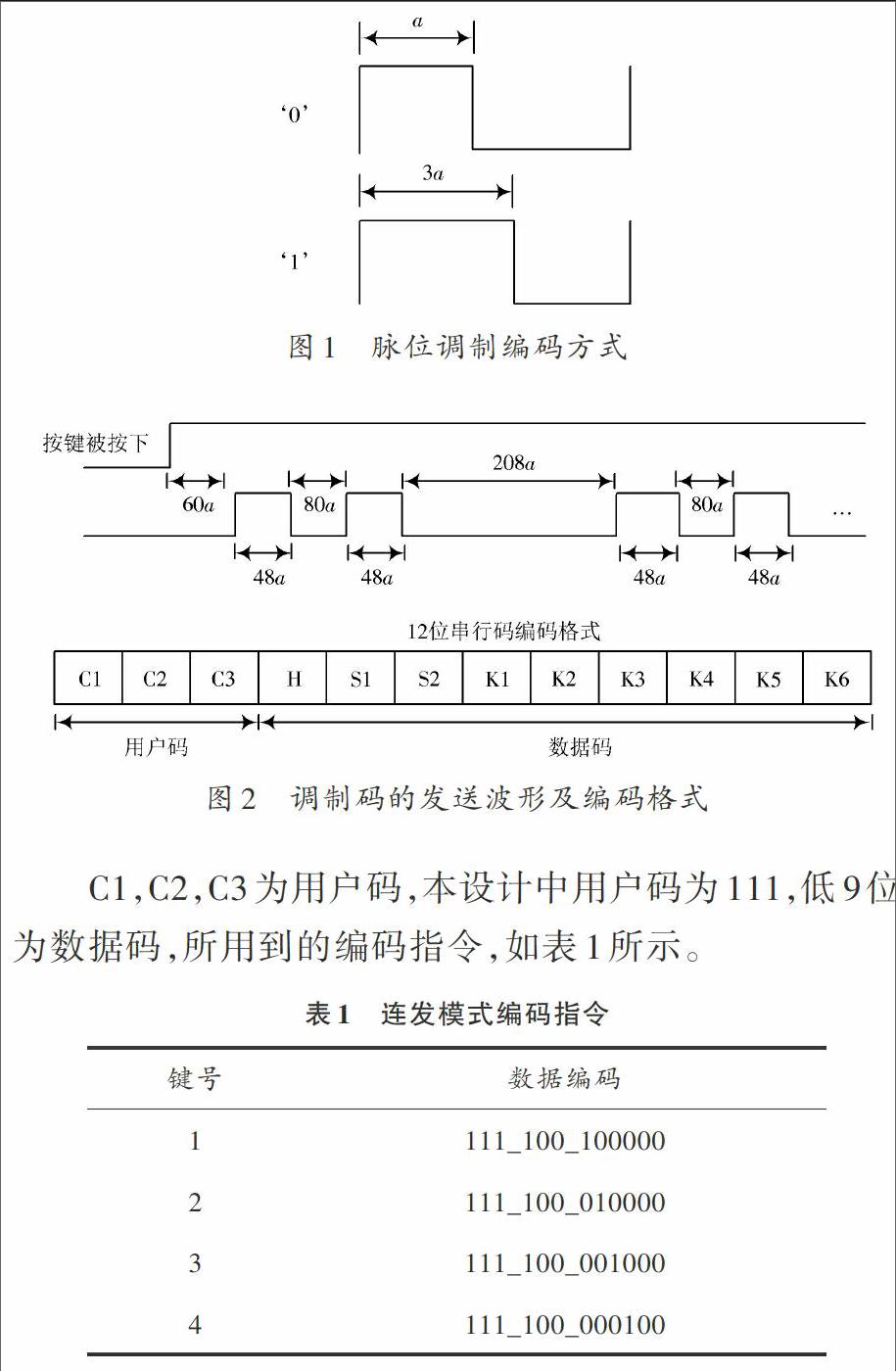

发射电路采用SC9148B为主芯片,其调制方式采用脉位调制(Pulse Position Modulation,PPM),将遥控指令编码成脉冲序列[4]。其遥控指令的‘1是以占空比为[34]的正脉冲表示,‘0则用占空比为[14]的正脉冲表示,[a=16(38 kHz)。]

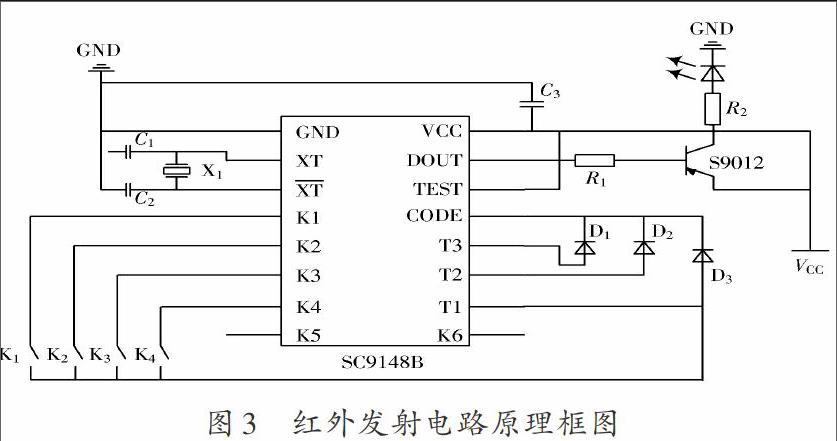

脉位调制编码方式如图1所示。编码协议由12位按键码组成,每一位均按照上述编码规则所代表的‘0,‘1构成,时间长度为[12×4a=48a。]当按键被按下时,发射电路将以12位码(48a)为一组发送两次编码,其中60a时间间隔为从按键按下到发送编码的延迟时间,80a为重复发送12位码(48a)的间隔时间,208a为重复发送两次编码的间隔时间。编码指令如图2所示格式连续发送。

电路工作原理为,当检测到按键按下时,DOUT端口输出38 kHz高频调制信号,经红外发射驱动电路放大后,通过红外发射管发送出去。

3 红外接收电路

采用通用红外接收头HS0038B完成对红外光信号的接收、放大、滤波与解调[5],解调后的逻辑电平信号通过扩展I/O口送入FPGA中,由FPGA编程实现接收信号的解码功能及相应的彩灯模式控制,从而实现彩灯多模式显示的红外遥控功能。设计解码器时应该注意,HS0038B内部集成有反相器以保证接收头有足够的灵敏度,从载波上恢复出来的基带信号与原调制发射前的基带信号是反相的。

4 FPGA解码电路与模式控制电路

FPGA解码控制器的核心思想是: 根据本设计的红外通信协议,12位发送数据命令中的位码‘1或者‘0的时间长度为[4a,]本设计将在每一个[4a]时间里,对每一位码元进行高电平脉冲采样[6?7],为方便计算采样脉冲个数,最大限度减少误差,故使用采样时钟频率为50 MHz。若采样后所得的脉冲数超过10 000而少于30 000,则判断为逻辑‘1;若所得脉冲数超过30 000而少于80 000,则判断为逻辑‘0;若脉冲数不满足条件,则视为无效。全局时钟脉冲采样数计算过程如下:endprint

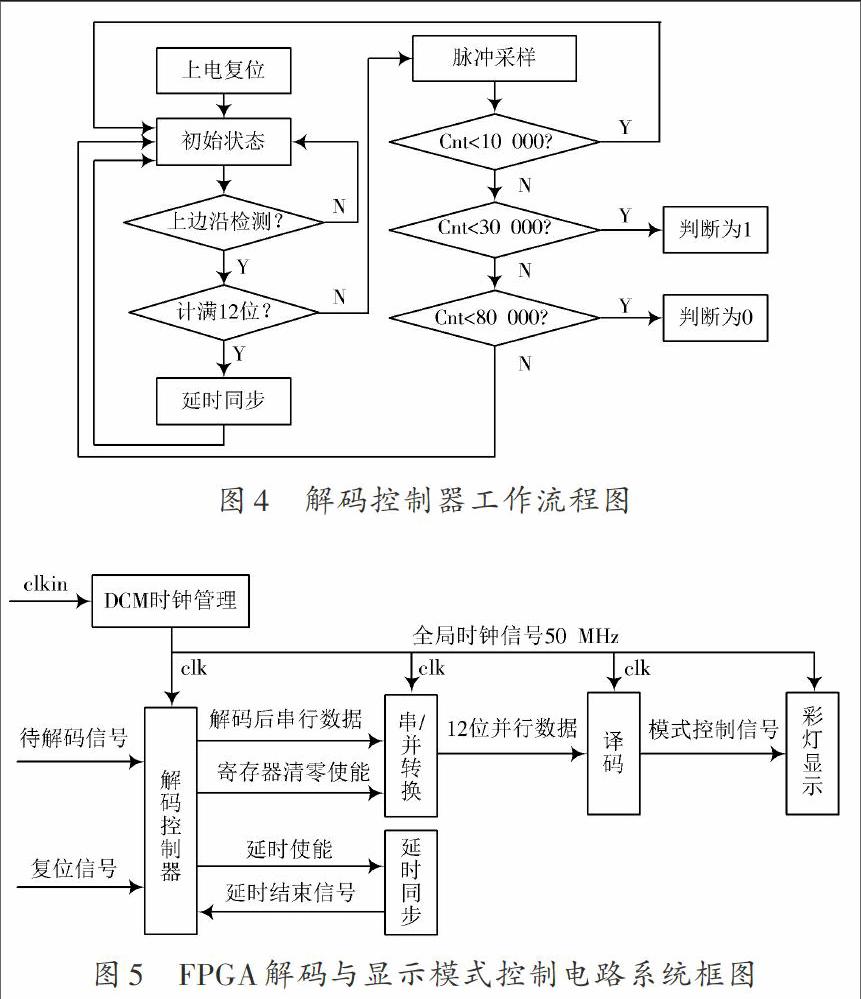

解码控制器工作流程图如图4所示。系统复位进入初始状态。首先进行输入上边沿检测,若上升沿有效,表示检测到红外基带信号,进而判断是否接收到完整12位数据编码,接收到则经延时同步(同步时间大于80a)后回到初始状态进行下一次12位编码数据检测,否则进入脉冲采样状态。当高电平采样脉冲数小于10 000,视为无效,回到初始状态;脉冲数大于10 000而小于30 000,视为接收到数据编码1;脉冲数大于30 000而小于80 000,视为接收到数据编码0;脉冲数大于80 000,视为无效,回到初始状态。解码控制器输出的串行码逐位进入后级串/并转换器。

解码核心FPGA控制器采样频率为50 MHz。FPGA设计部分主要包括三个模块,即时钟管理电路(Digital Clock Manager,DCM),解码控制电路,显示模式控制电路。其中解码电路包含解码控制器,信号同步延时器,串/并转换器三个模块;显示模式控制电路由译码器、彩灯循环显示电路组成。FPGA逻辑设计系统框图如图5所示。

DCM模块将输入时钟频率转换为50 MHz频率的全局时钟信号clk,给后续所有模块提供工作时钟。解码控制器对输入的基带信号进行采样,如图5所示,采样后的串行数据经过串/并转换器[8?9]后被并行输出,再由译码器转换为与按键指令对应的模式控制信号,控制彩灯进行多模式显示。为保证信号同步[10],移位寄存器的时钟周期为[4a,]由50 MHz全局时钟分频得到。

经实际测试系统工作正常,性能良好,FPGA解码模块实现了对红外编码的实时解码和显示。收发距离约为20 m。在Modesim仿真环境下,FPGA解码与模式控制电路系统时序仿真验证,如图6所示。

下面给出仿真结果的说明,为方便描述,图6(a)中的信号从上至下用[a1,][a2,][a3,…]表示;图6(b)中的信号从上至下用[b1,][b2,][b3,…]表示。[a1]为50 MHz时钟信号,[a3]为仿真选用的12位串行编码输入信号111100100000,[a10]为12位并行码数据;[b1]为2位模式控制信号,[b2]为彩灯循环显示数据码。由仿真图可以看到,每一个[a3]信号到来时,解码控制器准确无误地将其并行输出,并由译码器转换为模式控制信号11,在[b1]控制模式下,彩灯依次点亮(低电平代表灯亮),对应码型依次为01110111,10111011,11011101,11101110。

5 结 语

本文设计并实现了一种基于FPGA红外遥控彩灯控制电路,可根据红外发射器的编码格式,利用FPGA可编程特性灵活地对其进行相应的解码。本设计很好地实现了四路红外遥控彩灯显示模式的循环控制,用户可根据实际需求自由改变彩灯的循环模式。相比专业芯片或者单片机软件设计技术,FPGA逻辑器件并行处理方式使得电路响应时间更短,运算成本更小,即使在强干扰环境下也能可靠稳定的工作。同时,随着FPGA技术的迅猛发展,其成本的迅速降低,体积的不断减小,在未来工业、照明领域等有着广泛的应用前景。

参考文献

[1] 谭会生,张昌凡.EDA技术及应用[M].西安:西安电子科技大学出版社,2002.

[2] 丁跃华,陈艳峰,龙筝.红外遥控系统的一种设计方法[J].现代电子技术,2007,30(7):50?52.

[3] 牛戴楠.基于FPGA的红外图像预处理系统的研究与设计[D].武汉:武汉理工大学,2008.

[4] 侯继红.基于CPLD/VHDL语言的红外遥控解码器设计[J].通信技术,2010(7):193?194.

[5] 程明阳,陈锦莉,锁言鹏.一种基于FPGA的实时红外图像放大模块[J].现代电子技术,2011,34(16):146?148.

[6] 蔡勇.基于FPGA的多功能红外遥控器设计[D].成都:电子科技大学,2007.

[7] 刘潇婷.基于FPGA的红外遥控电子密码锁的实现[D].大连:大连海事大学,2008.

[8] 张亦华,延明.数字电路EDA入门:VHDL程序实例集[M].北京:北京邮电大学出版社,2003.

[9] 云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2009.

[10] 林宇航,施隆照.一种基于Verilog HDL的红外遥控解码电路的设计[J].科技创新导报,2012(32):24?25.endprint