频率计权网络的数字电路实现

赵丹 李丽 贺慧勇 刘嘉文 廖文平 王燕 商梅雪 魏明生

摘 要: 提出一种频率计权网络的数字电路实现方案,详细阐述由滤波器设计工具生成频率计权滤波器,然后采用HDL代码生成工具将其转换成可移植、可综合的能在FPGA上实现的HDL代码,分别在软件和硬件上进行仿真验证测试的过程。结果表明,设计的频率计权网络符合计权特性及允差标准,且采用此方法设计的频率计权网络简化了电路结构,操作简单,降低了功耗、成本,节省了资源,提高了效率,能快速得出信号的频率计权值。

关键词: 频率计权; HDL代码; 数字电路; FPGA仿真

中图分类号: TN711?34 文献标识码: A 文章编号: 1004?373X(2015)19?0094?04

Abstract: An implementation scheme of digital circuit for frequency weighting network is presented. The frequency weighting filter generated by the filter design tool is described in detail, which is converted into transplantable and synthesizable HDL code by using HDL code generation tool, and can be implemented on FPGA. The test process of the filter model was simulated and verified respectively by software and hardware. The test results show that the designed frequency weighting network conforms to weighting characteristic and tolerance standard, and can simplify circuit structure and operation, reduce power consumption and the cost, save resources and improve efficiency. The frequency weighting value of the signal can be obtained quickly.

Keywords: frequency weighting; HDL code; digital circuit; FPGA simulation

0 引 言

人的耳朵听到声音后的感觉,不仅与声的强度有关,而且与声音的频率有关。一般情况下,人耳对高频段的声音比较敏感,而对低频段的声音感觉不明显,即使是声压级相同的声音,频率不同也可能听起来不一样响[1?2]。为了正确认识声音的特性,进行噪声测量及分析,预防噪声对人耳产生危害,根据等响度曲线对接收到的声音信号进行频率计权滤波,以模拟人耳的响度感觉特性[3]。频率计权在噪声测量及分析中有很重要的作用,它是一种模拟人耳对不同频率的声音感觉不同的特性,使计算出的声压级与人耳所到的感觉一致的网络,其实质就是对声音信号进行滤波处理[4?6]。传统的办法是用模拟电路实现频率计权网络[7],这种方法采用了大量如电阻、电容等模拟器件,结构复杂、成本高、功耗大,其稳定性、可靠性、性能指标很难做好,而且不方便调试[8]。目前,很多是通过计算机,ARM,DSP等软件方法实现频率计权网络,该方法程序代码复杂,占用资源多[9?11]。

本文提出一种频率计权的电路级实现方案,以减少程序代码设计复杂和硬件电路调试不便等问题。该方法是数字化全电路实现,占用资源少、速度快、功耗低、可移植性好,适合FPGA以及ASIC实现。

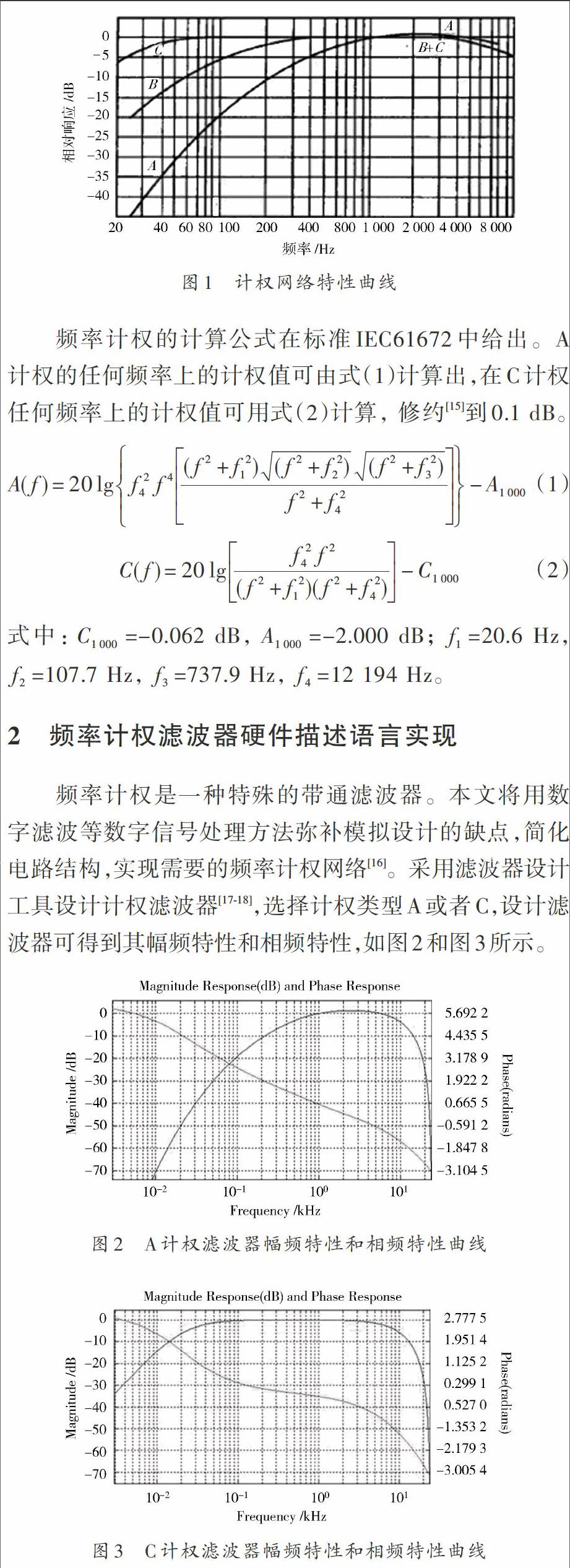

1 频率计权特性

频率计权的基本定义是指幅度稳定不变的输入信号级与实际测量输出信号级两者之间作为频率函数关系而规定的差值, 频率计权值用分贝(dB) 表示[12]。为了更好地模拟人耳听觉在不同频率处不同的灵敏度,声级计的频率计权主要有A和C计权[13?14]。

A计权网络是模拟人耳对55 dB以下低频噪声的响应,电信号在中、低频段(1 000 Hz以下)有较明显的衰减。C计权网络是模拟人耳对高强度噪声感应的频率特性[15]。

由幅频特性可以看出,A计权滤波器对其低频、中频段(1 000 Hz以下)有较大的衰减;在整个频率范围内C计权滤波器的响应近乎平直。将仿真出来的结果与频率计权允差表[15]比较可以得到,设计出的频率计权符合表中的允差标准,说明设计出来的结果符合要求。

将滤波器设计工具实现的频率计权滤波器算法转换成硬件在FPGA中实现,就需要设计HDL代码。滤波器代码生成工具利用已生成的代码和模型生成可移植和可综合的VHDL或Verilog HDL代码[19],且生成的代码可读性较高,可用于FPGA编程设计,并在开发板上进行验证[20?22]。

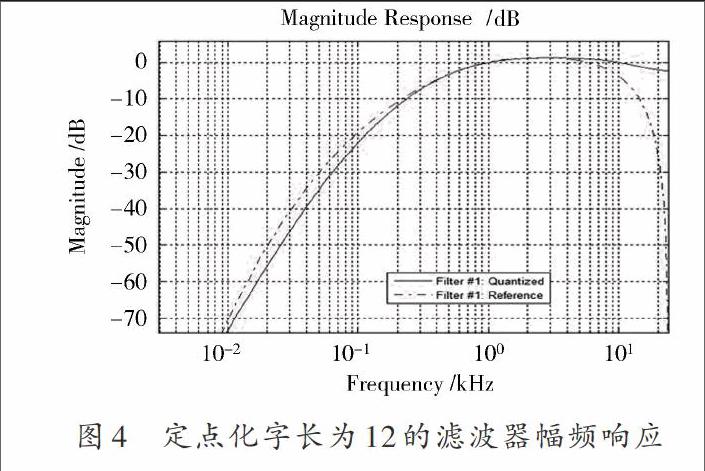

生成代码时在计权类型中分别选择A,C计权方式,在音频系统中抽样频率一般都是48 kHz。由于用于FPGA编译仿真的软件Quartus Ⅱ不支持浮点型数据,为了使滤波器在FPGA硬件上实现,就需要对生成的滤波器数据类型重新定义,使数据更符合FPGA的处理方式[23]。在设计中把数据进行量化,进行定点仿真。由滤波器设计工具得到滤波器的系数,根据频率计权精度要求将系数量化,得到定点型数据[24?25]。考虑到滤波器的精度以及节省资源的问题,选择合适的字长范围进行分析。如图4所示,滤波器系数的字长为12,可看出滤波器的系数定点化后,幅频响应与未定点化的响应相差很大,所以应当提高系数的字长以减小误差[25]。endprint

如图5所示为提高滤波器系数量化字长的过程,当字长提高到16位时,观察到定点化后和未定点化的滤波器幅频响应相差很小,已经符合要求。所以在滤波器系数定点化时选择定点字长为16位。

3 频率计权滤波器仿真测试

生成计权滤波器的HDL代码后将其在Quartus Ⅱ里进行仿真测试,将生成的Testbench代码进行测试[26?27]。Testbench产生阶跃响应、斜坡响应和Chirp响应,分别在信号级和电路级进行仿真。以A计权滤波器为例,比较以上信号的信号级仿真和电路级仿真[28],如图6~图11所示。

在QuartusⅡ中生成不同频率的正弦波,通过频率计权滤波器模块进行验证。在嵌入式逻辑分析仪SignalTapⅡ中提取输入及输出信号的幅值,如表1所示。考虑到滤波器数据定点化及抗溢出问题,需要将输出进行预衰减[29?30],所以设定输入信号为16位,输出信号为12位,则频率计权值=[输出峰峰值(输入峰峰值24)]。将对应的幅值进行计算处理后可得到信号的频率计权特性曲线,如图13所示。

将此频率计权特性曲线以及实际测量计算出的计权值与理论A频率计权特性比较,所设计的频率计权滤波器生成HDL代码仿真测试结果符合标准给出的频率计权特性及允差[15],但由于输入信号的幅度不同使得在低频的数据有一定的误差。

5 结 语

本文介绍的频率计权网络减少了采用模拟电路方法带来的复杂和不稳定,克服了软件算法设计占用过多资源等困难,将算法由信号级向电路级转换,实现全数字电路的计权滤波器,在信号级和电路级两个方面进行了仿真,在FPGA中实现并做了初步性能测试。这部分电路将实际用于“全数字化个体噪声暴露保护装置”中,但在硬件测试中对低频信号的频率计权存在误差,需继续改进。

参考文献

[1] 吴云.频率计权与声音的评价[J].江苏现代计量,2011(3):34?35.

[2] 金晖,何洁,钟晴红,等.频率计权的数字化实现[J].电子工程师,2005,31(1):11?12.

[3] 陈剑林,白滢,牛锋,等.声级计的频率计权特性[J].计量技术,2008(6):47?50.

[4] 钟波,孙庆生,王雪晶,等.声级计频率计权特性自动检定系统研究与实现[J].电声技术,2010(5):37?40.

[5] 张登攀,高志强.噪声[13]倍频程计权声级算法[J].河南理工大学学报:自然科学版,2013(6):709?712.

[6] 李淑芹.数字化环境噪声自动监测终端的研究[J].科技与企业,2014(11):141?142.

[7] 肖锋,李建锋.噪声测量中频率计权的实现[J].测试技术学报,1996(2):8?13.

[8] 陈品,陈心昭.A计权电路对p?p声强法测量精度的影响[J].合肥工业大学学报:自然科学版,2012(7):865?869.

[9] 罗自荣,陈章位,蔡德威,等.基于嵌入式系统的频率计权实现方法分析与对比[J].振动与冲击,2014(9):21?26.

[10] 金晖,何洁.频率计权的全数字实现[J].仪器仪表学报,2006(z2):1495?1496.

[11] 谭谦.数字化环境噪声自动监测终端的研究[D].天津:天津大学,2010.

[12] HAMPTON R D. Frequency?weighting filter selection for H2 control of microgravity isolation systems: A consideration of the "implicit frequency weighting" problem [J]. IEEE Transactions on Instrumentation and Measurement, 2000, 49(2): 265?269.

[13] 何岭松.频率计权网络的公式化表达[J].仪器仪表学报,1996(5):93?95.

[14] 周星,张晨,裴真,等.全数字式声级计系统的设计与实现[J].信号处理,2005(z1):609?612.

[15] 国家质量监督检验检疫总局.JJG 188?2002 声级计检定规程[S].北京:国家质量监督检验检疫总局,2002.

[16] 陈磊.数字信号处理技术在噪声频谱分析仪中的应用[D].西安:西安电子科技大学,2010.

[17] 王艳文,崔志娟,张静.基于Matlab/FDATool的数字滤波器设计[J].科技信息,2013(21):373?374.

[18] 郭海丽,王紫婷.基于Matlab/Simulink的FIR数字滤波器的设计与实现[J].电气应用,2008,27(1):73?75.

[19] OTHMAN N, JABBAR M H, MAHAMAD A K, et al. Luo rudy phase I excitation modeling towards HDL coder implementation for real?time simulation [C]// Proceedings of 2014 the 5th IEEE International Conference on Intelligent and Advanced Systems. Kuala Lumpur: IEEE, 2014: 510?515.

[20] 诸葛俊贵.基于Matlab模糊控制器HDL代码的自动生成[J].电子科技,2012,25(1):42?44.

[21] 胥京宇.消除隔阂,提升效率:MATHWORKS推出基于Matlab生成HDL代码的产品[J].世界电子元器件,2012(5):66?67.

[22] 王丽.基于Matlab/FDATool的语音信号滤波处理[J].德州学院学报,2013,29(4):27?30.

[23] 郝小江,黄昆.FIR数字滤波器设计及其FPGA实现[J].微型机与应用,2013(19):22?24.

[24] NAMIN A H, LEBOEUF K, HUAPENG W, et al. Artificial neural networks activation function HDL coder [C]// Proceedings of 2009 IEEE International Conference on Electro/Information Technology Windsor. Taibei, China: IEEE, 2009: 389?392.

[25] 高宇晨,戴居丰.改进的IIR滤波器避免运算溢出和定点DSP的实现[J].天津通信技术,2001(3):31?34.

[26] 张慧娟.HDL Coder和HDL Verifier支持HDL代码生成和验证[J].EDN CHINA 电子设计技术,2012,19(5):20?21.

[27] 程栋.关于HDL测试的研究[D].长沙:湖南大学,2003.

[28] 刘福泉.基于FPGA的FIR数字滤波器实现[D].北京:北京邮电大学,2012.

[29] 张家田,刘新英,严正国.DSP的定点溢出处理技术[J].中国科技信息,2008(24):83?85.

[30] 王新金,顾冬华.基于定点DSP的IIR滤波器溢出分析[J].自动化与仪器仪表,2008(5):69?70.endprint