基于FPGA和Matlab的FIR数字滤波器

曹振吉 何敏

摘 要: 为了满足信号处理快速和灵活的要求,基于FPGA实现的FIR滤波器有这两方面的优势,使用Matlab中的FDATool计算出滤波器系数并分析其幅频特性,利用FPGA分别设计实现串行结构、全并行结构以及基于IP核的FIR数字滤波器。利用Matlab软件进行FIR滤波器仿真,并与基于FPGA实现滤波器的Modelsim仿真输出数据进行比较,结果表明,设计的FIR滤波器功能正确、滤波性能良好。通过对不同结构滤波器的资源占用情况和数据处理速度进行分析,得出不同应用场合可选择不同的滤波器结构的结论。

关键词: FIR; FPGA; 串行结构; 并行结构; IP核

中图分类号: TN713?34 文献标识码: A 文章编号: 1004?373X(2015)19?0098?04

Abstract: Since the actual signal processing has the requirements of real?time response and flexibility, the implementation of FPGA?based FIR filter has the two advantages. The filter coefficient is calculated and the magnitude?frequency characteristic is analyzed by FDATool in Matlab. The FIR digital filters of serial structure, parallel structure and IP core based were designed and realized respectively by FPGA. FIR filters are simulated by Matlab, and compared with the data output by Modelsim simulation of the filter implemented by FPGA, the results show that functions of the designed FIR filters are correct, and filtering performance is better. The resource occupation situation and data processing speed of different structure filters are analyzed, and the conclusion of filters with different structures can be chosen to apply to suitable situation was obtained.

Keywords: FIR; FPGA; serial structure; parallel structure; IP core

0 引 言

数字滤波器是一个按预定的有限精度算法实现的、将输入的数字信号转换为所要求的输出数字信号的线性时不变系统[1?2]。由于FPGA的并行处理特性和自上到下的编程思想,所以其实现的数字滤波器能够兼顾系统实时性和灵活性的要求[3?4]。

根据系统时域性能,数字滤波器分为有限长单位脉冲响应(Finite Impulse Response,FIR)数字滤波器和无限长单位脉冲响应(Infinite Impulse Response,IIR)数字滤波器。相对于IIR数字滤波器,FIR滤波器有较大的优越性[5?6],所以本文将对FIR滤波器进行设计。FIR滤波器系数的设计方法主要有3种,包括窗函数法、频率采样法和最优化方法[5]。

本文借助Matlab中的FDATool工具,针对滤波要求设置合适的参数,可以方便地求解出滤波器系数和响应曲线,然后利用FPGA分别设计实现串行结构、全并行结构以及基于IP核的FIR数字滤波器,利用Matlab软件进行FIR滤波器仿真,并与基于FPGA实现滤波器的Modelsim输出数据进行对比,以此判断3种结构滤波器设计的正确性。

1 基于Matlab的FIR数字滤波器的设计

1.1 FIR滤波器基本原理及结构

根据FIR滤波器硬件实现结构的不同,可将其分为直接型、级联型、频率采样型和快速卷积型[6]等4种形式。本文主要讨论直接型结构。根据直接型FIR滤波器的原理,以长度[N]为例,输出一个滤波数据,需要完成[N]次乘法和[N-1]次加法运算。

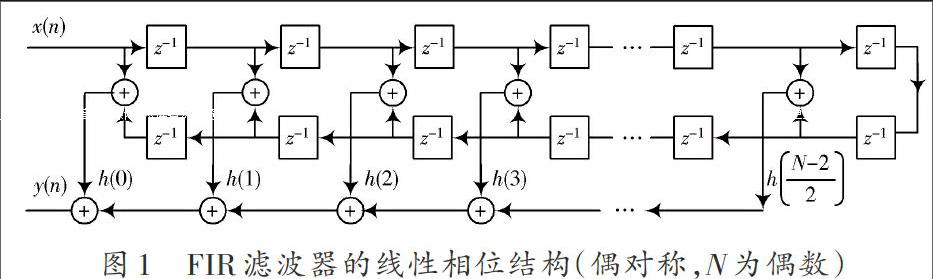

依据FIR滤波器严格的线性相位特点,得到滤波器系数具有对称性,因此能够采用线性相位结构,如图1所示[7],可以减少运算次数和节约硬件资源。因为[h(n)]关于[n=(N-1)2]对称[7],可以先将位置上对称的两个数据加起来,再与相应的滤波器系数相乘,然后经过累加得到最终的结果。采用这种结构,每得到一个输出数据,要完成[N2]次乘法和[N-1]次加法,与之前相比,可以减少[N2]次乘法运算。

1.2 基于Matlab的FIR数字滤波器的设计

调用Matlab软件中的FDATool工具,设置相应参数。求解滤波器系数时,FDATool可方便地选择系数的量化位数。完成滤波器设计参数设置后,可直接生成FPGA所需的滤波器系数配置文件。

本文要设计的FIR滤波器参数为:低通滤波器,采样频率为50 kHz;过渡带为12~15 kHz,通带纹波最大为0.1,阻带纹波最大为0.001。通过Matlab编程,分别对滤波器系数未量化、10位、12位、14位量化的滤波器幅频响应结果进行比较,如图2所示。从图2中可以看出,量化位数对滤波器的阻带纹波有较大的影响,且量化位数越高影响越小,故采用14位量化。endprint

2 基于FPGA的FIR数字滤波器的设计

以低通滤波器为例,本文分别对全串行结构、全并行结构以及基于FIR核的FIR数字滤波器进行设计和仿真。

2.1 全串行结构的FIR滤波器

全串行结构是指只用一个加法器串行实现滤波器对称系数的加法运算。设计一个低通FIR滤波器,采用凯塞窗函数,其他参数同上,长度为16,FPGA的系统时钟为50 MHz,输入12 b数据,输出29 b滤波结果。

首先采用Matlab软件求得14位量化后的滤波器系数,然后根据图1所示的结构采用VHDL语言完成滤波器的编程。在Matlab软件中仿真出由9.765 kHz和18 kHz两种频率信号叠加的输入信号,经Matlab编写的FIR滤波前后的频谱如图3所示。

从图3,图4可以看出,FPGA实现的滤波器输出信号频谱与Matlab直接仿真的结果几乎相同。从图5可以看出,叠加输入信号滤波后形成频率为9.765 kHz的单频信号,即将18 kHz的信号滤除掉了。因此,从仿真结果来看,通过FPGA设计实现的全串行结构的FIR滤波器满足滤波要求。

2.2 全并行结构的FIR滤波器

全并行结构滤波器的思想就是将一次滤波运算内的乘法同时执行,通过硬件资源换取运行速度。这种结构可以采用直接型、转置型和脉动方式实现[5,8?9]。

基于加法树直接型结构的全并行FIR低通滤波器的设计过程与串行结构滤波器相同,直接给出仿真结果。Matlab仿真的信号滤波前后的频谱如图6所示,FPGA仿真的信号滤波前后的频谱如图7所示,FPGA仿真的信号滤波前后的时域波形如图8所示。

从图6,图7可以看出,FPGA实现的滤波器输出信号频谱与Matlab仿真的结果几乎相同。从图8可以看出,合成单频信号滤波后,已经形成规则的频率为9.765 kHz的单频信号。从仿真结果来看,使用FPGA设计全并行结构的滤波器是正确有效的。

2.3 基于IP核的FIR滤波器

采用IP核设计一个低通最优FIR滤波器,过渡带为12~15 kHz,采样频率为50 kHz,通带纹波最大为0.1,阻带纹波最大为0.001。系统时钟频率为50 MHz,输入和输出数据位宽均为10 b。

从图9,图10可以看出,FPGA实现后的滤波器输出信号频谱与Matlab直接仿真的结果几乎相同。从图11可以看出,合成信号滤波后将18 kHz的高频信号滤除掉了。因此,从仿真结果来看,基于IP核实现的FIR滤波器功能正确,满足设计要求。

3 性能比较

从资源占用情况来看,为了便于对比,选用Xilinx公司的Spartan?6系列的XC6SLX45?CSG484?3芯片,从ISE的Design Summary获得3种结构FIR滤波器分别占用逻辑资源的数量,如表1所示。显然,全并行结构的滤波器使用的寄存器(Registers)、查找表(LUTs)和乘法器(DSP48A1s)的数量大于另外两种结构滤波器的使用数量,而全串行结构的滤波器是占用硬件资源最少的。

从数据处理速度来看,全并行结构具有很高的数据处理速度,其系统频率与数据速率相同;全串行结构的数据速率是系统频率的[1N](N为乘加运算的次数)[6],特别在乘加次数[N]较大时,与并行结构滤波器的数据速率有较大差距。

基于IP核实现的FIR滤波器比较灵活,可以根据参数设置选择合适的硬件资源占用数量与数据处理速率。所以,在速度作为最重要考量的因素时,选择全并行结构能收到较好的效果,比如可以将其应用于高速测量系统中;全串行结构滤波器占用硬件资源少,但是处理数据的速率较慢,可以用于速度要求不高且硬件成本较低的系统中。若是在一般应用场合,使用IP核设计滤波器方便灵活,可以兼顾占用资源与速度两方面的要求。

4 结 语

本文借助Matlab计算出滤波器系数,然后利用FPGA分别设计实现串行结构、全并行结构以及基于IP核的FIR数字滤波器。其中,串行结构和并行结构的FIR滤波器性能各有优势[10],串行结构滤波器占用资源少,但运算速度较并行结构慢,并行结构滤波器运算速度快,但占用资源多;而基于IP核的数字滤波器则能够兼具两者的优势,占用资源少,运算速度快,具有非常好的灵活性。利用Matlab软件进行FIR滤波器仿真,并与基于FPGA实现的滤波器的输出结果进行比较,仿真结果表明,本文设计的3种FIR滤波器功能正确,滤波性能良好,选择不同的结构设计滤波器可以满足不同的系统要求。

参考文献

[1] 江志红.深入浅出数字信号处理[M].北京:北京航空航天大学出版社,2012.

[2] 程佩清.数字信号处理教程[M].北京:清华大学出版社,2003.

[3] 孙耀奇,高火涛,熊超,等.基于Matlab和FPGA的FIR数字滤波器设计和实现[J].现代电子技术,2008,31(11):89?92.

[4] 高耀红.基于FPGA的FIR低通滤波器[D].长沙:湖南大学,2012.

[5] 高亚军.基于FPGA的数字信号处理[M].北京:电子工业出版社,2012.

[6] 杜勇,路建功,李元洲.数字滤波器的Matlab与FPGA实现[M].北京:电子工业出版社,2012.

[7] 蒋立平,谭雪琴,王建新.一种基于FPGA的高效FIR滤波器的设计与实现[J].南京理工大学学报,2007,31(1):125?128.

[8] 郑运冬.基于FPGA的FIR滤波器设计与实现[D].上海:复旦大学,2013.

[9] 谢海霞,孙志雄.可编程FIR滤波器的FPGA实现[J].电子器件,2012,35(2):232?235.

[10] 马骏,何敏,杨鸣.基于FPGA的电磁金属探伤系统及其微弱信号处理[J].测试技术学报,2014,28(5):425?430.

[11] 单文军,周雪纯,李文华.基于FPGA的FIR数字滤波器设计与实现[J].现代电子技术,2013,36(14):123?126.endprint