CPLD加Flash在线升级及配置FPGA

刘光文,李淯阳,成 亮(重庆金美通信有限责任公司,重庆 400030)

CPLD加Flash在线升级及配置FPGA

刘光文,李淯阳,成 亮

(重庆金美通信有限责任公司,重庆400030)

摘 要:基于Xilinx公司的Vertext4 FPGA嵌入式系统采用Flash作为BootLoader以及操作系统目标文件的存储介质。如果将FPGA的目标文件通过以太网接口发送给处理器,处理器接收到FPGA的目标文件后将其存储到Flash的空闲空间,然后利用CPLD模拟产生配置时序,将Flash中的FPGA目标文件按相应的时序送给FPGA配置管脚,即可实现FPGA的上电配置。其优势在于省去了专用的配置PROM,并且能够完美地支持FPGA目标文件在线升级。实践证明,该方法具有很强的通用性,在嵌入式系统中具有很强的实用价值。

关键词:嵌入式;系统;配置;处理器;目标文件;在线升级

1 引 言

基于FPGA的嵌入式系统技术已经得到了广泛、深入的应用,包括工业控制领域、网络应用、消费类电子产品、成像和安全产品等领域。

目前大规模FPGA均通过把设计生成的目标文件配置到芯片内部的SRAM完成其逻辑功能,具有可重复编程性,可灵活实现各种逻辑功能,FPGA的这种特性使其在现代电子系统设计中得到了广泛应用。但基于SRAM工艺的FPGA是易失性的,系统掉电后SRAM内的数据将全部丢失,需要外接ROM保存其配置数据,系统每次上电时必须重新配置数据才能正常工作。通常设计时采用两种方案保存FPGA的目标文件,一是使用专用的PROM,如Xilinx公司的XCFxx系列PROM来提供FPGA的配置时序[1],上电时自动加载PROM中的目标文件到FPGA的SRAM中;另一种是在含有微控制器的嵌入式系统中,采用其他非易失性存储器来存储目标文件,如EEPROM、Flash等,使用CPLD模拟FPGA的配置时序将ROM中的目标文件置入FPGA中。与前面一种方案相比,后者成本更低,并且可完美支持在线升级。

2 配置原理

2.1主串配置原理

Xilinx公司的Vertext4系列FPGA采用90nm工艺的,该芯片具有高性能、低功耗、可无限次编程等特点,并且内部嵌入了IBM公司的高性能PPC405 (Power PC)硬核处理器[2],可完美支持Vxworks操作系统[3]。芯片支持从串、主串、从并、主并、JTAG等方式进行配置[4],与主串配置相关的引脚功能及配置如下:

(1)M[2:0]:配置模式选择。M2,M1,M0均接下拉电阻,即M[2:0]=000时为主串模式。

(2)CCLK:配置时钟,由被配置FPGA提供时钟信号,上升沿有效。

(3)DIN:串行数据输入位。

(4)PROG_B:低电平异步复位FPGA内部逻辑位。内部配置逻辑复位后,等该引脚为高电平时才能配置FPGA。

(5)INIT_B:由低电平到高电平跳变时,采样配置模式选择管脚M[2:0],确定配置模式;配置过程中若出现配置错误,INIT_B将呈现低电平。

(6)DONE:复位及配置过程中为低电平,配置成功后为高电平。

2.2配置时序的捕获及确认

Xilinx公司的目标编程文件有“.bit”、“.bin”、“.mcs”等格式,其中.bit格式用作JTAG下载,其他2种格式用作专用PROM编程。系统产生配置文件时首先需生成专用PROM编程文件“.bin”文件,然后将该文件存储到FLASH或PROM中。

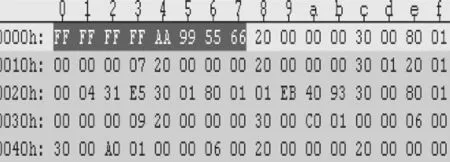

使用十六进制编辑程序例如“UltraEdit”将“.bin”文件打开查看其内容,可以发现其头部是以0xFFFFFFFF和0xAA995566开始,如图1所示。

图1 查看FPGA配置文件内容

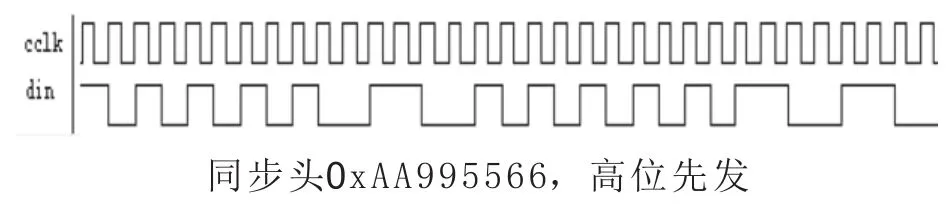

为了确认主串配置时是高位先发还是低位先发,通过示波器捕获配置时序,对比配置文件内容,可以确认使用的是高位先发顺序。如图2所示。

图2 串行数据为高位先发顺序

2.3在线升级原理

设计首先需要在嵌入式系统的软件程序中加入FTP服务器功能,对于使用VxWorks操作系统的嵌入式系统来说只需勾选相应的FTP服务器组件即可实现。然后使用计算机登入嵌入式系统的FTP服务器,将FPGA的目标文件按特定名称上传到FTP服务器。FTP服务器在检测到特定名称的文件后会通知处理器处理该文件,处理器随即开始读取该文件并将文件写入到Flash中指定的区域,写入后删除该文件,结束本次升级,为下一次在线升级做好准备[5]。

3 功能实现

3.1硬件框图

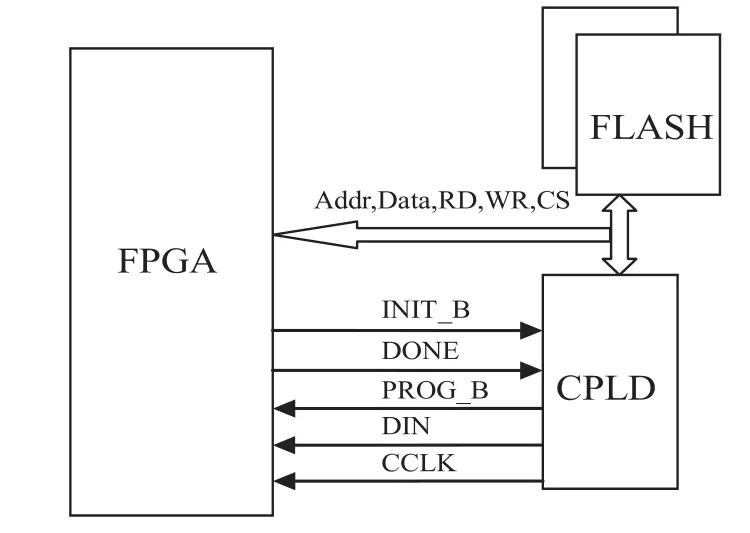

硬件上总体分为3个部分:Flash芯片、CPLD芯片及FPGA主芯片。Flash采用的是2片Intel公司的16位宽、16Mbyte容量的TE28F128J3C芯片[6],共同组成32位宽、32Mbyte容量的存储器;CPLD采用Xilinx公司的XC95144芯片[7];FPGA使用了Xilinx公司的XC4VFX60芯片。具体硬件框图如图3所示。

图3 硬件整体框图

3.2CPLD实现流程

CPLD配置FPGA的逻辑流程如下:

(1)系统上电后,CPLD将PROG_B置为低电平,复位FPGA内部逻辑重新配置FPGA,延时100μs充分复位内部逻辑后,再将PROG_B置为高电平。

(2)将PROG_B置高电平大于300ns后,FPGA会将INIT_B置为高电平,CPLD采样到INIT_B变为高电平后,CPLD根据FPGA送来的配置时钟CCLK的上升沿串行地将配置数据送给FPGA,在CCLK的每个上升沿,都有1个Bit的数据被传递给DIN。

(3)32个CCLK时钟后,CPLD将Flash地址加1,然后将Flash数据线上的数据采样加载到内部移位寄存器;然后再使用32个CCLK时钟周期将移位寄存器内的数据串行地传递给DIN,然后再将Flash地址加1,一直循环。

(4)所有配置数据传送完成,CRC校验无误,则DONE呈现高电平,否则为低电平。

(5)CPLD采样到DONE为高后,立即释放Flash控制信号,进入等待状态。FPGA则释放全局三态(GTS),激活IO管脚,释放全部置位复位(GSR)和全局写使能(GWE)有效,开始执行配置区里的逻辑,如果FPGA要重新配置,可由CPLD再次将PROG_B拉低,则DONE信号会由高变低,重新进入配置状态。

4 实验结果验证

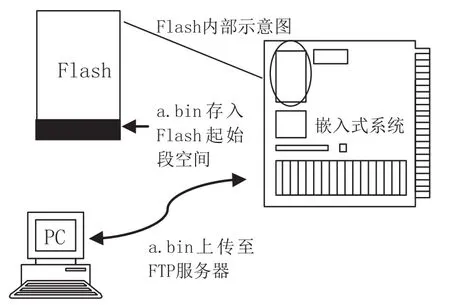

为了验证实验结果,在嵌入式系统正常运行的情况下,使用1台PC机作为FTP客户端,通过以太网接口登录嵌入式系统的FTP服务器,然后将FPGA目标文件“a.bin”上传到FTP服务器。处理器收到文件并解析出该文件后,将该文件从0地址开始写入到Flash的底层空间,如图4所示。

图4 在线升级示意图

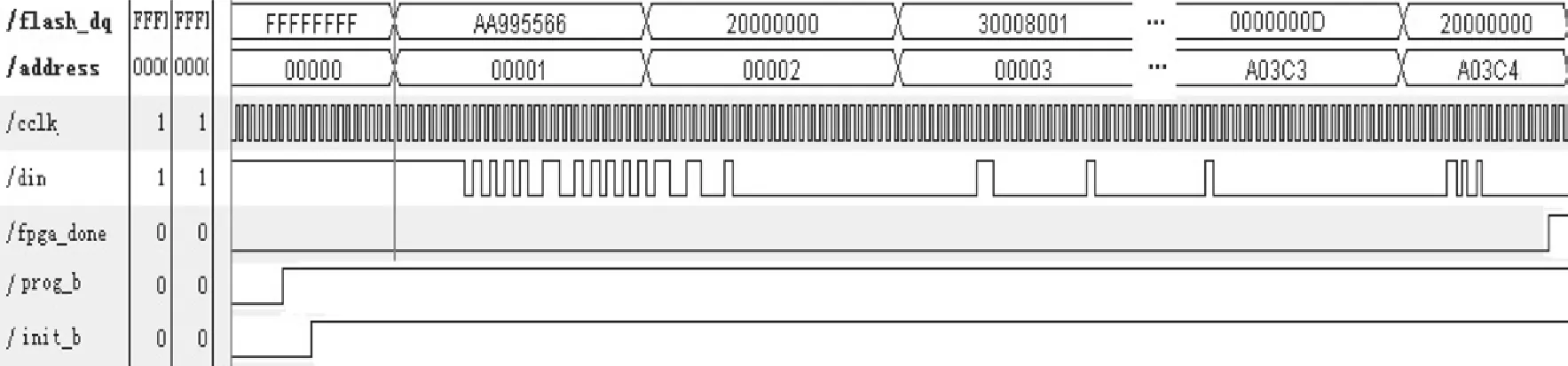

CPLD程序也设计为从0地址开始加载FPGA目标文件并配置FPGA。具体配置时序如图5所示。

图5 CPLD配置FPGA的波形

从图5左边部分可以看出,CPLD从0地址开始累加读取Flash数据,Flash前4个地址读出的数据依次为0xFFFFFFFF、0xAA995566、0x20000000、0x30008001,然后并行数据被转换为串行数据送到DIN。

图5右边部分,可以看到地址已经累加到0xA03C3,然后DONE信号变为高电平,CPLD在检测到DONE信号为高电平后,完成配置过程,进入等待状态。

5 结束语

基于CPLD加FLASH的FPGA主串配置方案原理简单易行[8],虽然举例是采用Xilinx公司Vertext4系列的XC4VFX60 FPGA,但稍加修改即可适用于其它系列的FPGA器件,具有很强的通用性和实用性。

另外,FPGA具有可重复配置的灵活性,在嵌入式系统中可以通过串口、网口远程烧写Flash重构系统功能,这种在线重构技术,为设备的智能化在线维护、功能重组和在线升级等提供了可能,具有广阔的应用前景。

参考文献:

[1]XILINX:Platform Flash In-System Programmable Configuration PROMS[EB/OL].2004/www.xilinx.com.

[2]XILINX:EDK PowerPC Tutorial Ver 3.0[EB/OL].2004/www.xilinx.com.

[3]XILINX:Getting Started with EDK and Wind River VxWorks[EB/OL].2004/www.xilinx.com.

[4]XILINX:Virtex-4 Configuration Guide[EB/OL].2004/www.xilinx.com.

[5]胡启道,张福洪,戴绍港.基于MCU的FPGA在线配置[J].电子器件,2007,30(3):1049-1056.Hu Qidao,Zhang Fuhong,Dai Shaogang.Online Configure FPGA Based on MCU[J].Electronic Devices,2007,30 (3):1049-1056.

[6]Intel:Intel StrataFlash?Memory(J3)28F256J3,28F128J3,28F640J3,28F320J3(x8/x16)Datasheet [EB/OL].2004/http://www.intel.com.

[7]XILINX:XC95144XLHighPerformanceCPLD [EB/OL].2007/www.xilinx.com.

[8]王小峰,周吉鹏.一种FPGA在线配置flash的方法[J].电子器件,2006,29(3):902-904.Wang Xiaofeng,Zhou Jipeng.Online Configure flash by FPGA[J].Electronic Devices,2006,29(3):902-904.

Online Update and Configure FPGA By CPLD and Flash

Liu Guangwen,Li Yuyang,Cheng Liang

(Chongqing Jinmei Communication Co.,Ltd.,Chongqing 400030,China)

Abstract:The embedded system,based on Xilinx Vertext4 FPGA,usually uses Flash as storage medium to save BootLoader and operating system object file.If the FPGA object file is sent to processor via Ethernet port,it will be saved to free space in Flash by processor,and the CPLD generates a time sequence and sends the FPGA object file to FPGA through the pin configuration,then the power-on configuration is simulated and realized.It has advantage of saving a dedicated configuration PROM and supporting FPGA object file online updating perfectly.The practice proves that it is a universal solution and has lots of practical utility in embedded system.

Key words:Embedded;System;Configuration;Processor;Object file;Online update

DOI:10.3969/j.issn.1002-2279.2016.02.001

中图分类号:TP317.4

文献标识码:A

文章编号:1002-2279(2016)02-0001-03

作者简介:刘光文(1982-),男,四川省遂宁市人,助理工程师,学士,主研方向:FPGA逻辑设计、硬件电路设计。

收稿日期:2015-05-29