基于SOC平台的XMC模块设计与实现

潘 波,李 彪(重庆金美通信有限责任公司,重庆 400030)

基于SOC平台的XMC模块设计与实现

潘 波,李 彪

(重庆金美通信有限责任公司,重庆400030)

摘 要:altera的cycloneV系列SOC FPGA内嵌了一个双核ARM Cotex-A9处理器,处理器部分与FPGA逻辑部分集成在一个芯片里面,提高了芯片的集成度,为设备的小型化设计提供了便利。XMC架构作为VITA组织推荐的模块架构,广泛使用在VPX板卡上。首先介绍了altera的SOC平台和基于VITA42标准的XMC模块架构,然后通过扩展处理器外设,在处理器平台上实现了linux操作系统并完成驱动设计,实现了基于该平台的数据处理模块,最后测试了模块搭载的CPU性能和FPGA扩展SerDes的性能。

关键词:SOC技术;XMC模块;CycloneV芯片;VITA42标准;Cotex-A9处理器;QuartusII工具

1 引 言

altera的cycloneV SOC FPGA是一个片上系统,包含了硬核处理器系统(HPS)和FPGA逻辑系统。SOC FPGA在cycloneV中有SX、SE、ST三种系列[1]。HPS包含了一个双核ARM Cotex-A9微处理器,FLASH存储器控制器,SDRAM控制器,片上缓存,外设接口,调试接口,锁相环等[2]。FPGA部分包含FPGA逻辑单元,控制单元,锁相环单元,高速收发器,PCIe控制器等。

在VPX计算机系统中,外围功能模块通常采用XMC载板与模块配合的方式实现,其中载板主要提供接口功能[3],XMC模块主要实现数据处理功能,不同功能的载板和XMC模块可以组合成具有不同功能的VPX板卡。本设计将SOC FPGA的处理器部分和逻辑处理做成公用的XMC模块提供给VPX系统使用。

2 原理框图

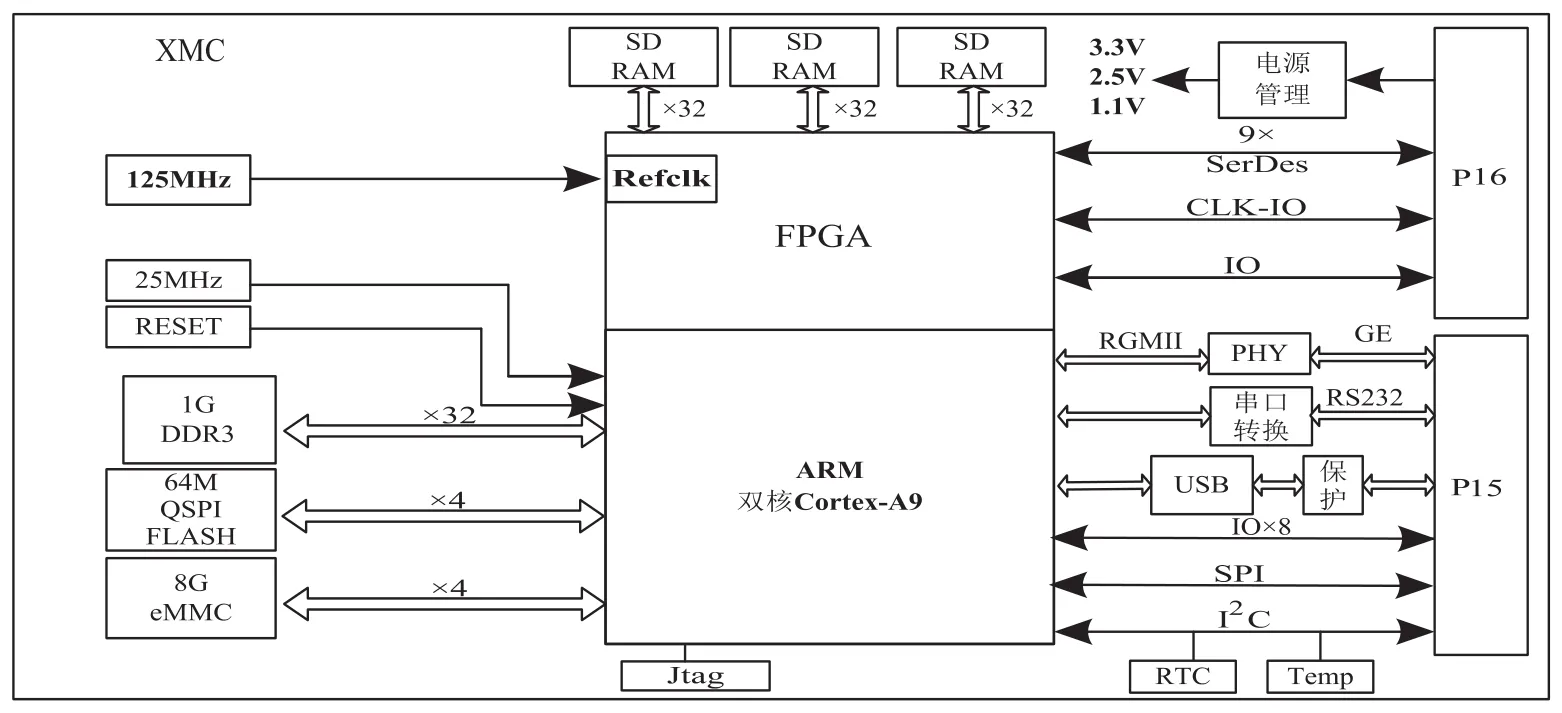

XMC模块的原理框图如图1所示。

图1 原理框图

HPS处理器系统,包含FPGA内嵌的一个Cortex-A9双核处理器核、1GByte DDR3内存、64MByte QSPI FLASH存储器、8G eMMC存储器、时钟、复位、调试接口等[4],并通过接口扩展了如下外设:

a)通过高通的AR8031以太网phy和以太网变压器扩展了1路10M/100M/1000M以太网接口;

b)通过MX3223扩展了2路RS232串口;

c)通过USB3300 USB phy芯片扩展了USB-OTG接口;

d)其他还扩展了SPI、I2C、温度测量、实时时钟等。

FPGA内嵌的ARM处理器情况如下:

a)Dual-core ARM 32bit Cortex-A9 MPCore processor;

b)4,000 MIPS(CPU频率:800MHz);

c)每个核32KB L1 data caches和32KB L1 data caches;

d)512KB共享L2 cache;

e)浮点协处理器(VFP)。

使用FPGA的高速收发器SerDes扩展4路千兆以太网接口对外,扩展4路SGMII接口通过背板与机内交换芯片连接,搭载三片32MByte的SDRAM用于以太网数据缓存,通过FPGA的I/O扩展槽位信息。

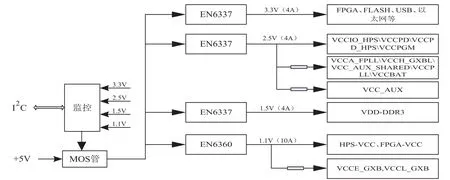

电源部分设计对该模块非常重要,选用三片EN6337模块产生3.3V、2.5V、1.5V,其中2.5V部分电源需要滤波后供电。使用电源模块EN6360产生1.1V给HPS和FPGA内核供电。其框图如图2所示。

图2 电源框图

3 启动过程

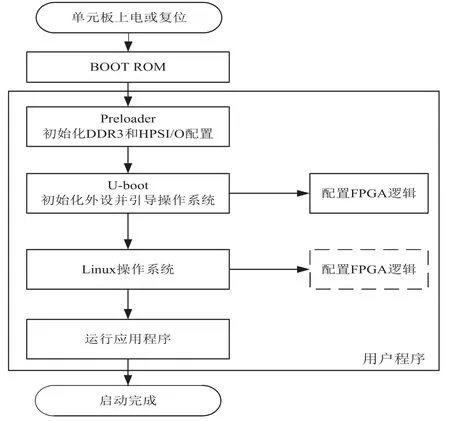

系统启动流程如图3所示,启动流程如下:

a)单元板上电或者CPU复位后处理器开始启动。

b)CPU从片上的BOOT ROM读取启动代码,这部分启动程序固化在芯片里面。启动代码主要完成读取启动模式管脚,然后从对应的存储器启动。

c)从QSPI FLASH的0x0地址启动Preloader程序,初始化DDR3内存和HPS的I/O配置。

d)从QSPI FLASH的0x4000地址启动U-boot,初始化CPU外设,比如:以太网接口、NAND FLASH、NOR FLASH等。

e)通过U-boot引导linux操作系统,操作系统采用Linux3.10。

f)系统启动完毕后,引导应用程序。

g)在Preloader、U-boot、linux操作系统里面都可以配置FPGA逻辑,第一次配置逻辑选择在U-boot里面进行,Linux操作系统用于动态配置FPGA逻辑。

图3 启动流程

4 XMC模块设计

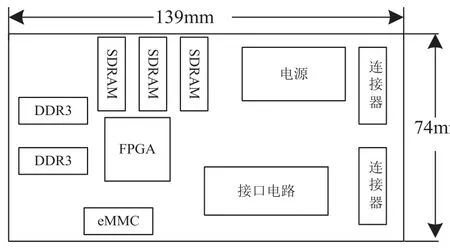

将上面所述的电路按照VITA42的标准制作成XMC模块,模块尺寸为:长×宽= 139mm× 74mm[5]。PCB布局如图4所示,FPGA在居中靠左的位置,它周边主要有2片DDR3存储器组合成1G内存,3片单片32M的SDRAM存储器,一个8G的eMMC大容量存储器,1片SPI FLASH。其他地方主要分布有电源转换,RS232接口转换,以太网接口电路,USB接口电路等。

图4 XMC模块框图

5 软件系统搭建

采用altera公司提供的quartus II 13.1与Qsys图形化开发工具配合使用,搭建了硬件架构与FPGA逻辑[6]。通过Qsys软件可以图形化设置DDR3内存参数,管理外设的管脚配置,处理器时钟频率设置等,根据设置,自动生成preloader用于引导系统。在系统中搭建了一个avalone总线桥,挂载到HPS 的AXI总线上,将AXI总线引到FPGA逻辑里面,这样CPU就可以方便的访问FPGA逻辑。

该平台采用Linux3.10操作系统,经过定制化裁剪后运用到模块上[7]。Linux系统里面主要包含了Linux内核,内存管理系统,FLASH驱动,千兆以太网驱动及TCP/IP协议栈,标准的USB驱动及协议栈,RS232驱动,SD卡驱动,SPI和I2C驱动等。挂载了基于BusyBox架构的嵌入式文件系统,管理模块上的QSPI FLASH和eMMC存储器。

6 性能测试分析

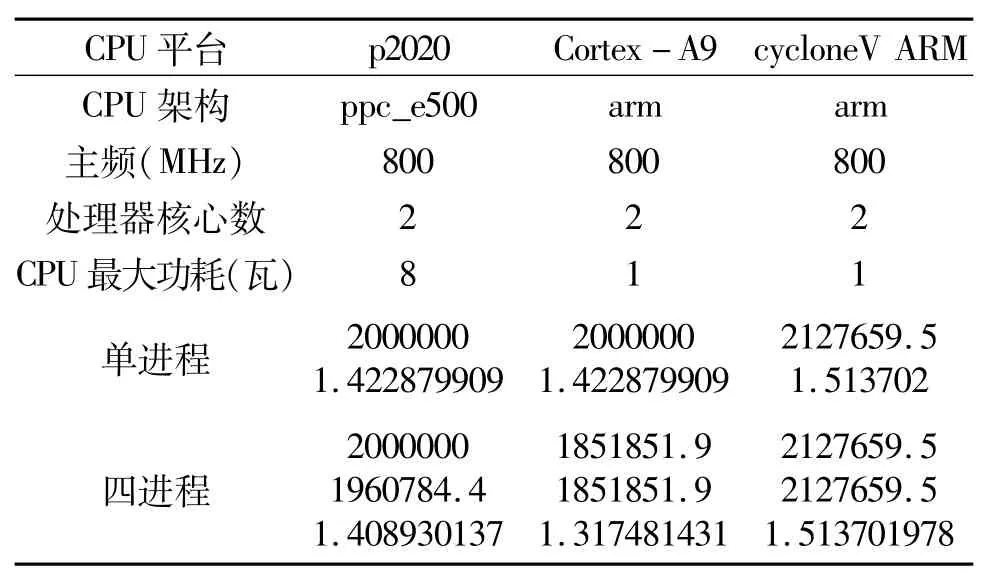

使用Dhrystone 2.1工具对处理器性能进行测试[8]。该工具主要包含赋值,基本运算(assignments),占总测试52(51%);控制语句(control statements),占总测试33(33%);函数(系统函数、用户函数)调用(procedure,function calls),占总测试17 (17%)。测试结果与常用的P2020和Cortex-A9处理器进行对比。测试了每秒执行的计算次数;单位时钟周期机器运行的速度对应“DMIPS/MHz”,计算方式为:机器运行值/1757/机器CPU速度。

使用存储器测试工具测试了eMMC和QSPI FLASH的写入速度。eMMC,write:4.76MB/s;QSPI FLASH,write:5.9MB/s。

经过上面的对比测试可以看到cylcone5内嵌的处理器与飞思卡尔的基于PowerPC架构的P2020和基于ARM架构的A9处理器处理性能相当。

表1 测试数据

7 结束语

基于cycloneV的平台既提供了较强的处理能力,也有丰富的FPGA处理资源,可以运用到各类对集成度要求较高的地方。

采用XMC模块架构,主要运用到VPX板卡上,也可以运用到其他板卡上,作为数据处理平台。

参考文献:

[1]Altera.Cyclone V Device Handbook[EB/OL].2013/www.alter.com.

[2]Altera.SoC FPGA ARM Cortex-A9 MPCore Processor Advance Information Brief[EB/OL].2013/www.alter.com.

[3]Ray Alderman.STANDARD FOR VITA 42.0[S].American:American National Standards,2008.

[4]李江涛.ARM Cortex-A9的NEON技术研究及应用[J].单片机与嵌入式系统应用,2013,13(3):46-49.LiJiangTao.Research and Utilization of NEON Technology Based on ARM Cortex-A9[J].Microcontrollers & Embedded Systems,2013,13(3):46-49.

[5]胡锦,彭成,谭明.基于VPX标准的PMC/XMC载板设计[J].计算机测量与控制,2010,18(8):1852-1855.HuJing,PengCheng,TanMing.Design of PMC/XMC Board Base on VPX Specification[J].COMPUTER MEASUREMENT & CONTROL,2010,18(8):1852-1855.

[6]王莹.Xilinx可扩展处理平台[J].电子产品世界,2012,19(2):40-44.Wang Ying.expanded processor platform of Xilinx[J].Electronic Engineering & Product World,2012,19(2):40-44.

[7]刘娟花,厉谨.基于FPGA的数字日历设计[J].现代电子技术,2014(3):15-18.LiuJuanHua,LiJing.Design of digital calendar based on FPGA[J].Modern Electronics Technique,2014,(3):15-18.

[8]张晓静,华更新,刘鸿瑾.处理器测试方法研究与实现[J].现代电子技术,2011,19(3):4-8.ZhangXiaoJing,HuaGengXin,LiuHongJing.Study and Implementation of Test Method[J].Practical Electronics,2014,(3):15-18.

Design and Implementation of XMC Module Based on SOC Platform

Pan Bo,Li Biao

(Chongqing Jinmei Communication Co.,Ltd.,Chongqing 400030,China)

Abstract:The dual-core ARM Cortex-A9 MPCore processor is integrated into the hard processor system of the Altera CycloneV FPGAs.Processor system is integrated with FPGA logic system on a chip so that the integration of chip can be enhanced,and it facilitates the design of miniaturization for equipment.As the recommended module structure of VITA,the XMC architecture is widely used in the VPX board.Firstly,this article introduces the Altera's SOC platform and the structure of XMC module based on the VITA42 standard.Then,the Linux operating system is realized and the driver design is accomplished on the processor platform by expanding processer peripherals.The data processing module based on the platform is realized.Finally,the performance of the CPU on module and SerDers interface extended by FPGA,is tested.

Key words:Technology of SOC;XMC module;CycloneV FPGA;Standard of VITA 42;ARM Cortex-A9 MPCore processor;Tools of quartus II

DOI:10.3969/j.issn.1002-2279.2016.02.006

中图分类号:TP274

文献标识码:A

文章编号:1002-2279(2016)02-0017-03

作者简介:潘波(1984-),男,重庆市人,硕士研究生,主研方向:主要从事有线通信设备整机架构研究。

收稿日期:2015-05-29