基于Nios II的导引头电子舱信号群高速采集系统

秦文姬,李 力(西安工程大学计算机科学学院,西安 710048)

基于Nios II的导引头电子舱信号群高速采集系统

秦文姬,李 力

(西安工程大学计算机科学学院,西安710048)

摘 要:导引头电子舱是导弹探测、跟踪目标的部件,是导弹系统的关键部分,因此电子舱产品使用前的调试和检测至关重要。介绍了一种基于Nios II的导引头电子舱信号群高速采集系统。该系统采用Cyclone II系列EP2C35芯片,以Nios II软核为核心处理器,完成了对A/D转换后的30路信号群的高速采集处理。与之前采用PCI总线方案相比,此方案简化了硬件电路、减小了设备体积、降低了成本,可以满足不同产品的各种逻辑电平、编码装定、参数预置及功能拓展升级的需求,提高了系统的可靠性和智能化分析处理实验数据的水平。

关键词:电子舱;Nios II软核;片上可编程系统;SPI核;A/D转换器ICL7135;数据采集

1 引 言

现有基于PCI总线的导引头电子检测台是集光学、结构支持、机械驱动、电子控制及计算机测量为一体的光机电一体化测控系统设备。它的主要功能是对现有激光类导引头产品进行生产调试和检测验收。但是,该类产品通常硬件电路设计复杂,设备体积大,成本较高。

本项目在原有基于PCI总线的导引头电子舱检测系统基础上,对其控制器部分进行技术改造。本检测系统的核心设计是在Altera公司Cyclone II系列FPGA芯片上,以Nios II软核处理器为核心设计一个片上可编程系统(SOPC),代替原核心控制器件-2片8位单片机和CPLD,完成整个检测系统的控制功能。介绍的基于Nios II的高速数据采集系统是该检测系统的重要组成部分,主要功能是采集电子舱的响应输出信号,以便检验电子舱是否满足技术条件规定的指标。

电子舱的响应输出模拟信号共30路,组成了一个庞大的信号群,数据采集系统需要对这30路信号群进行高速采集处理[1]。信息社会的发展,很大程度上取决于信息与信号处理技术的先进性[2]。一项很有发展前景的技术已经应用于电子产品的检测中,这就是基于Nios II的SOPC(System On Programmable Chip)技术。Nios II是在Altera公司的FPGA器件上实现的一种32位处理器。Nios II CPU是一种采用流水线技术、单指令流和可配置的通用RISC处理器,它可以与用户自定义逻辑结合成SOPC系统,被编译并下载到Altera的可编程器件中去[3]。本系统以Nios II软核CPU为核心,通过在FPGA上构建可编程片上系统SOPC,利用SOPC系统自定义外设接口,配合DMA技术,同时采用A/D转换器ICL7135、SOPC系统自带的FIFO芯片等器件,实现对电子舱信号群高速数据的采集工作。

2 系统结构与工作原理

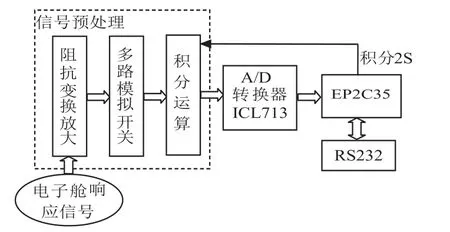

该系统包括信号预处理模块、A/D转换模块、Nios系统电路板等部分,其结构框图如图1所示。

图1 系统总体结构图

为了能同步采集到电子舱的30路模拟信号,系统需要对信号进行预处理。系统将响应信号经过阻抗变换放大电路、模拟开关阵列和积分运算等电路后,在Nios II CPU的控制下使其按时输出四组8路模拟信号。接下来将处理后的信号送给A/D转换器ICL7135,Nios II CPU通过SPI核控制外围A/D转换器ICL7135完成数据采集工作。使用Nios系统自定义FIFO缓冲模块将经过处理的数据缓存起来,DMA完成数据从FIFO到SDRAM的搬移工作,再通过RS-232接口将数据实时传输给上位机。

3 硬件电路设计

3.1基于Nios II的EP2C35电路板设计

3.1.1 Nios II处理器配置

选用的Cyclone II EP2C35是一款性能卓越、具有高速以太网接口而且可扩展性极强的优秀片上微控制器,片内集成了4个PLL、52 M4K RAM以及专用高速外设接口[4-5]。采用的Nios II CPU具有大容量窗口的寄存器堆、简单完备的指令集、强大的寻址模式、较强的可扩展性、硬件辅助等特点。

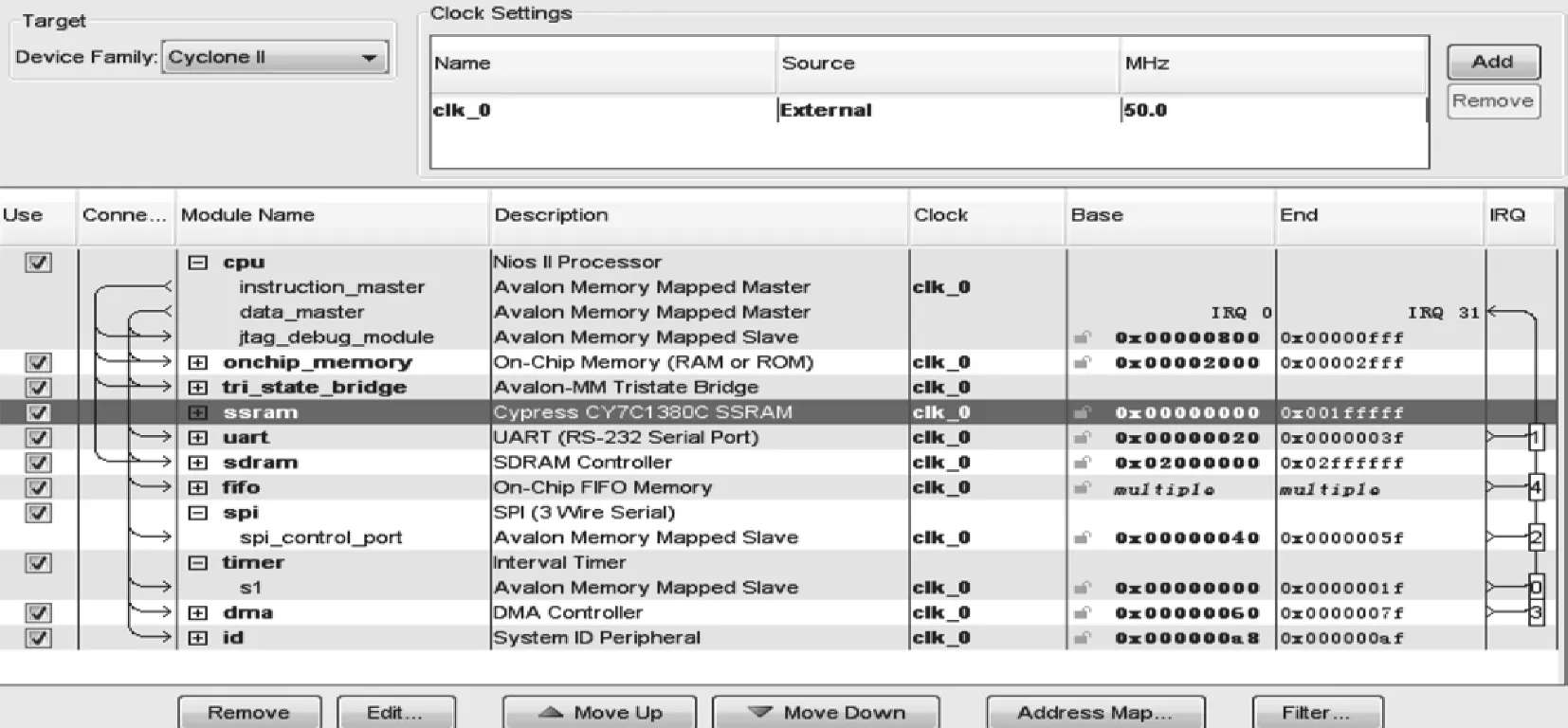

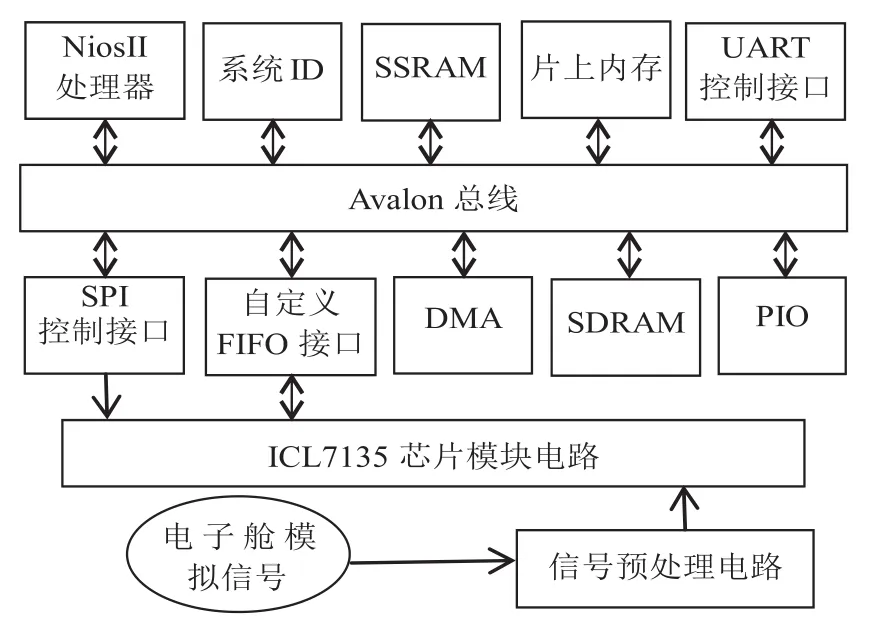

根据系统需求,SOPC系统需包括Nios II处理器、SSRAM、片上内存、SPI控制接口、自定义FIFO接口、用户PIO、DMA、SDRAM控制器、UART通信接口等。因此,选取Nios II 32bit CPU、On-chip_ Memory、Tri _ state _ bridge、SSRAM、SPI Controller、Communication UART、Timer、DMA、FIFO、PIO和System ID等模块,通过Quartus II自带的SOPC Builder工具构成片上系统。Nios II CPU可以灵活地进行任务调度,配合Nios II IDE软件编程环境,可以方便的对A/D采集芯片进行SPI总线配置。电子舱信号经过隔离放大等预处理后,在Nios CPU的控制下送入A/D转换电路模块完成采集工作,将经过处理的数据缓存到FIFO,DMA完成数据从FIFO到SDRAM的搬移工作。Nios II内核配置和CPU板工作原理框图分别如图2、图3所示。

图2 Nios II内核配置

图3 CPU板工作原理框图

3.1.2 SPI总线控制器模块

SPI是SOPC Builder内部集成的嵌入式系统常用的工业标准串行协议,它可直接与各个厂家生产的多种标准外围器件直接接口。该接口一般使用4根线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT,有的SPI接口芯片没有主机输出/从机输入数据线MOSI[6-8])。

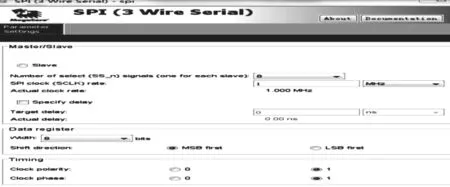

系统中使用SOPC Builder配置向导来指定SPI内核特性,SPI的配置如图4所示。

(1)主/从配置(Master/Slave)

系统中SPI内核控制A/D转换器完成数据采集,因此选项选择主控制器模式。在此模式下,可选择通用选择信号(Generate Select Signals)、SPI时钟频率(SPI clock rate)和指定延时(Specify Delay)。

图4 SPI配置选项

(2)通用选择信号

该选项设置从设备的数目,取值范围为1-132。SP主控制器内核为每个从控制器提供唯一的SS_n信号。本系统中,SPI核控制8路AD输入,因此选项选择8。

(3)SPI时钟频率

该选项设置主控制器和从控制器之间的SCLK频率。SPI主控制内核通过Avalon_MM分频产生SCLK。SCLK的实际频率不可能精确地匹配所需的目标时钟频率,实际获得的频率值小于指定的目标值[9]。

由于A/D转换器ICL7135支持的最高时钟频率为1MHz,本系统选用的时钟频率为1MHz。

3.2信号预处理模块

由于系统采集对象是30路相关模拟信号,本设计采用多路模拟开关AD7502阵列作为预处理信号电路。AD7502是一种双4通道多路开关芯片,依据两个二进制地址线(A0,A1)和选通端(EN)的状态来选择8路输入的两路,分别与两个输出端相接通。本系统中30路信号共需要四片AD7502,在译码控制逻辑的控制下,这四片AD7502将同时选通8路相关信号。为了能够并行采集到相关信号,在分配AD7502的引脚时,需要将这些相关信号分配在能够同时被选通转换的输入通道上。

3.3A/D采集模块

A/D采集模块是数据采集系统的重要组成部分。由于系统的采集对象是30路相关模拟信号,为了满足系统的高精度和高速要求,选用美国INTERSIL公司生产的4位双积分A/D转换器ICL7135。该芯片具有精度高(相当于14位A/D转换器)、成本低、自动校零、自动极性输出、自动量程控制信号输出等特点,其最高转换速率可达25次/秒。

要采集的模拟量先经过多路模拟选择开关MC4051芯片,由Nios II CPU通过SPI核控制8片ICL7135芯片完成数模转换,并通过UART核与上位机通信,将数据传回上位机。当“积分2秒”按键按下,待检测的信号形成后,就发SB_TB信号来启动A/D开始转换。Nios CPU采用中断方式读取结果。A/D转换结束后,由BUSY、STROBE和高位D5信号组成中断信号,由CPU响应中断来读走转换结果。模数转换器ICL7135及其外围电路如图5所示。

图5 模数转换器ICL7135及其外围电路

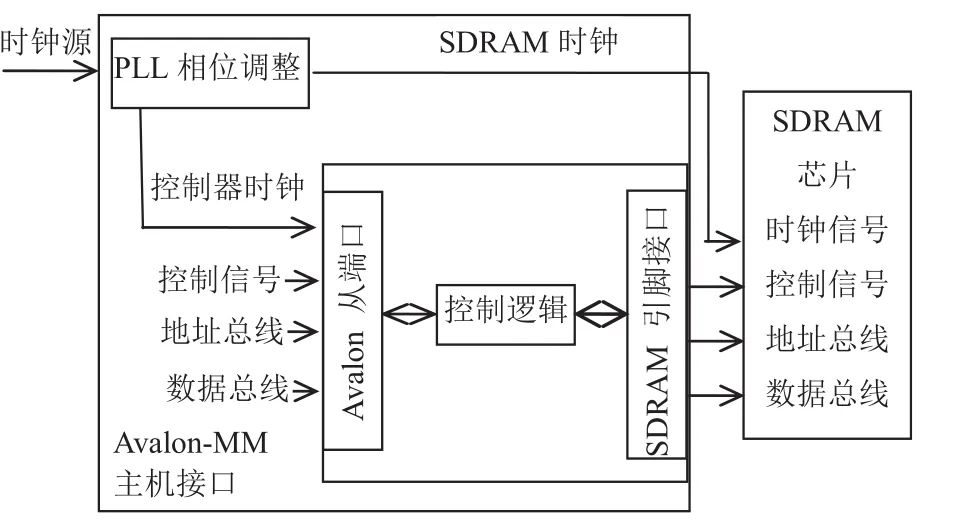

3.4SDRAM模块

由于EP2C35芯片的内存容量不能满足控制系统程序容量,因此需要外扩SDRAM作为运行存储器。根据SDRAM一般用于大容量易失存储器且成本较低的应用中的特点,因此将采集到的数据存储在一片SDRAM存储器中。Avalon总线接口的SDRAM控制器结构框图如图6所示。FPGA片内的SDRAM控制器IP核与外部SDRAM存储器芯片之间的硬件接口,包括了时钟接口(clk)、时钟屏蔽接口(cke)、地址总线(addr)、块选信号(ba)、片选信号(cs)、行选信号(ras)、列选信号(cas)、写选通信号(we)、数据总线(dq)和数据字节屏蔽信号(dqm)。SDRAM控制器的IP核可通过不同的数据宽度来访问SDRAM[9-10]。本系统中采用32位数据。

图6 SDRAM控制器结构图

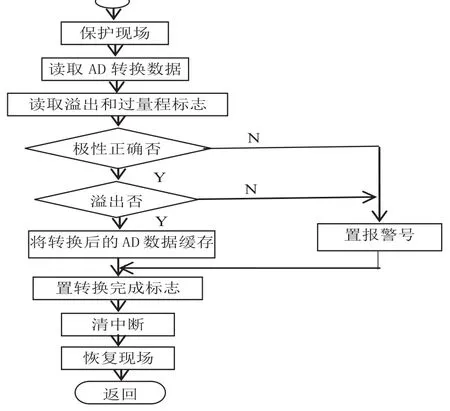

4 软件设计

系统软件设计是利用Altera公司的软件集成开发工具Nios II IDE来完成,用C语言进行编程[11-12]。软件设计主要包括嵌入式操作系统的移植、目标板底层驱动设计、A/D采集程序代码编写等部分,这里主要介绍关键的A/D采集程序。A/D采样子程序流程图如图7所示。

图7 A/D采样子程序流程图

5 结束语

系统采用Nios II处理器集成SOPC系统,有效解决了电子舱信号群数据的采集和存储问题,较好地完成了电子舱信号群的高速采集工作。

设计采用了通用大规模集成电路和嵌入式技术,简化了硬件电路、减小了设备体积、降低了成本,智能化程度更高。方案的硬件系统已通过了PCB加工及功能调试验证。该方案稳定可行,程序操作性强,在数据采集以及其它方面具有一定的参考价值。

参考文献:

[1]李薇,危建国.基于PCI总线的电子舱信号群高速采集系统[J].计测技术,2006,26(3):24-26.Li Wei,Wei Jianguo.The Electronic Cabin Signal Group High Speed Acquisition System Based on PCI Bus[J].Measurement technology,2006,26(3):24-26.

[2]刘政,刘富强.基于PCI总线的数据采集[J].中国科技信息,2005(11):12.Liu Zheng,Liu Fuqiang.Data Acquisition Based on PCI Bus[J].CHINA SCIENCE AND TECHNOLOGY INFORMATION,2005(11):12.

[3]刘书文,骆英.基于Nios II的超声相控阵数据采集系统[J].仪表技术与传感器,2014(6):72-75.LIU Shu-Wen,LUO Ying,WANG Zi-Ping.Data Acquisition System for Ultrasonic Phased Array System Based on Embedded NiosII[J].Instrument Technique and Sensor,2014(6):72-75.

[4]秦文姬,黄国兵.基于Nios II的蓄电池组在线监测系统的设计[J].微处理机,2011(6):73-76.QIN Wen-ji,HUANG Guo-bing.Design of Battery Online Monitor Unit Based on Nios II[J].MICROPROCESSORS,2011(6):73-76.

[5]赵宏阳,丁晓明.基于FPGA的高速多路视频数据采集系统[J].单片机与嵌入式系统,2012(7):56-59.Zhao Hongyang,Ding Xiaoming.Acquisition System for High-speed Multi-channel Video Data Based on FPGA [J].Microcontrollers &Embedded Systems,2012(7):56-59.

[6]刘培洲,高天德,夏彦泽,等.基于Nios 1I的以太网数据采集平台设计[J].计算机与数字工程,2014,42 (9):1733-1736.LIU Peizhou,GAO Tiande,XIA Yanze et al.Ethernet Data Collection Platform Design Based on NiosⅡ[J].Computer &Digital Engineering,2014,42(9):1733-1736.

[7]Alter Corporation.NiosII Hardware Development Tutoria [EB/OL].(2013-03-05)[2015-02-20]http://www.doc88.com/p-256253727166.html.

[8]李萍,凌力.基于Nios II的数据采集系统设计与实现[J].舰船电子工程,2012,32(1):74-76.Li Ping,Ling Li.Design and Implementation of Data Acquisition System Based on Nios II[J].Ship Electronic Engineering,2012,32(1):74-76.

[9]赫建国,倪德克,郑燕.基于Nios II内核的FPGA电路设计[M].北京:电子工业出版社,2010.He Jianguo,Ni Deke,Zheng Yan.FPGA circuit design based on Nios II[M].Beijing:Publishing House of Electronics Industry,2010.

[10]陈伟军,陶纯匡.基于Nios II的CCD采集系统的设计[J].单片机与嵌入式系统应用,2012(8):58-61.Chen Weijun,Tao Chunkuang.Design of CCD Acquisition System Based on NiosII[J].Microcontrollers & Embedded Systems,2012(8):58-61.

[11]张燕,任安虎.基于SOPC数据采集与控制系统的设计[J].电子设计工程,2012,20(12):184-185.ZHANG Yan,REN An-hu.Design of data acquisition and control system based on SOPC[J].Electronic Design Engineering,2012,20(12):184-185.

[12]蔡伟纲.Nios II软件架构解析[M].西安:西安电子科技大学出版社,2007.Cai Weigang.Nios II software architecture Analysis [M].Xi’an:Xi'an University of Electronic Science and Technology Press,2007.

A High Speed Acquisition System Based on Nios II for the Electronic Cabin Signal Group

Qin Wenji,Li Li

(Institute of Computer,Xi’an Polytechnical University,Xi’an 710048,China)

Abstract:As a key part of the missile system,the electronic cabin can detect and track the target missile,and it is required to be debugged and tested before using.A high speed data acquisition system based on Nios II is designed and realized for the electronic cabin signal group in this paper.Using cyclone series EP2C35 chip and Nios II as core processor,the system can process the signals converted by A/D and complete the high speed data acquisition.Compared with the previous PCI bus program,this system has some advantages,such as simplifying the hardware circuit,reducing equipment size and costs,adapting to a variety of different products' logic level,coding stapling and satisfying needs of presetting parameters and functional expansion upgrade.And it improves the level of reliability and intelligent analysis of experimental data processing system.

Key words:Electronic cabin;Nios II soft core;SOPC;SPI core;A/D converter ICL7135;Data acquisition

DOI:10.3969/j.issn.1002-2279.2016.02.019

中图分类号:TP368.1

文献标识码:A

文章编号:1002-2279(2016)02-0073-04

基金项目:❋2014年陕西省大学生创新创业训练计划项目(1240)

作者简介:秦文姬(1981-),女,山西省临县人,讲师,硕士研究生,主研方向:计算机测控、嵌入式系统应用。

收稿日期:2015-04-28