基于FPGA的SATA主机端控制器链路层发送模块设计

张庆顺,刘赞,郭宝增,张锁良

(河北大学 电子信息工程学院,河北 保定 071002)

基于FPGA的SATA主机端控制器链路层发送模块设计

张庆顺,刘赞,郭宝增,张锁良

(河北大学 电子信息工程学院,河北 保定071002)

计算机系统中SATA(serial advanced technology attachment)主机端控制器采用专用总线转换芯片和软件控制方式.为使得以FPGA(field-programmable gate array)为控制核心的电子系统可以直接使用SATA3.0硬盘作为数据存储介质,借鉴ATA1-7、SATA1.0、SATA2.0、SATA3.0等相关协议,提出了一种基于FPGA的SATA3.0主机端控制器的链路层发送功能模块的设计与实现方法,成功实现了数据在发送过程中的校验、加扰以及流量控制等相关功能.仿真结果表明:本控制器数据处理速度可达600 MB/s,验证了设计的正确性.

FPGA;ATA协议;SATA协议;主机端控制器

SATA(serial advanced technology attachment)是一种连接主机总线适配器和大容量存储设备的串行数据传输协议,主要应用于存储系统的数据传输.随着硬盘技术的发展,硬盘容量越来越大,接口传输速度越来越快,传统PATA(parallel advanced technology attachment)协议接口的不足日益明显.目前,PATA协议的主流是ATA-100协议和ATA-133协议,使用80根排线作为数据线、地址线和控制线.在传输速度方面,ATA-100的速度是100 MB/s,ATA-133的速度是133 MB/s.随着传输速度的不断提高,PATA总线间的相互干扰越来越难以抑制,过高的传输误码率导致传输后的数据无法使用.当传输速度达到133 MB/s时,并行传输技术已无法有效抑制总线信号之间的串扰,基于串行传输技术的SATA协议接口应运而生,其采用的高速差分串行传输技术从根本上解决了因串扰导致的传输误码问题.

2001年,Intel、DELL、Seagate等几大厂商组成了Serial ATA委员会,提出了第1代SATA协议标准,以取代PATA.SATA1.0的传输速度可达150 MB/s,超越了当时传输速度最快的PATA(ATA-133).2005年发布了第2代SATA 标准,SATA2.0的传输速度可达到300 MB/s.2009年发布了第3代SATA协议标准,其传输速度可达600 MB/s,但还远远没有达到串行传输技术的极限,第4代SATA标准有望达到1.2 GB/s.随着硬盘及计算机技术的发展,SATA 标准还将得以延续.此外,SATA协议接口支持热插拔,并提高了CRC(cyclic redundancy check)对数据、命令和状态包检错的能力,提高了数据传输的可靠性[1].

虽然SATA芯片接口速度越来越高,应用越来越广泛,但是针对SATA芯片开发的核心技术绝大多数都被国外的一些大公司所掌握,国内主要是购买国外的集成芯片,并无自主研发的成果.文献[1-3]也都是基于SATA2.0协议控制器的研究,在处理速度和设计方法上均有别于SATA3.0控制器的设计.鉴于此,为了实现以FPGA为核心的电子系统与SATA3.0接口的硬盘进行高速数据存储与读取功能,提出了一种基于FPGA芯片XC5VLX110T的SATA3.0主机端控制器的链路层发送功能模块的设计与实现方法,成功实现了数据在发送过程中的CRC计算、加扰以及流量控制等相关功能,处理速度可达600 MB/s,符合SATA3.0协议的标准.

1 SATA3.0协议链路层发送模块顶层设计

链路层位于物理层与传输层之间,主要用于校验和流量控制.在链路层进行数据传输的过程中,需要进行一系列操作,包括数据的CRC计算、数据加扰以及流量控制等,而这些操作都是依靠主机端与设备端原语的相互交互完成的[2].SATA3.0协议中定义了18种不同类型的原语,每种原语都是1个32位的控制字,本设计中的链路层发送状态机根据设备端反馈的原语控制主机端原语的生成与发送,从而实现主机端与设备端原语的交互.

图1为发送模块顶层设计示意图,主要分为链路层发送FIFO(first input first output)、链路层发送状态机、加扰器、CRC校验器4部分[3].当传输层有数据需要发送时首先向链路层控制器发送请求信号,此时tx_request信号置1,同时传输层开始将FIS(frame lnformation structure)帧写入链路层发送FIFO中.在空闲状态时,主机端与设备端没有建立数据通路,仅保持同步原语的交互,因此当主机端需要向设备端发送数据时,在数据通路建立完成前,不能进行数据的传输,若没有链路层发送FIFO,传输层发送的FIS帧必会丢失部分数据.本文中链路层发送FIFO的作用是缓存传输层的数据,保证数据的完整性.当主机与设备通过原语建立数据通路后,主机端物理层会向链路层反馈PhyRdy信号,此时发送状态机使能FIFO读和加扰器使能信号Scramble_en.根据Xilinx芯片的FIFO IP核的时序特性,当FIFO读使能有效时,数据将延迟1个时钟输出,而设计的加扰器产生的扰码序列也会延迟1个时钟输出,所以应同时使能FIFO读和Scramble_en信号,二者的输出数据经异或操作后通过Link_data端输出.当一帧数据传输完毕或者发送状态机接收到物理层反馈的DMA中断传输原语DMAT时,将CRC校验和与加扰器产生的扰码值异或并通过Link_data端输出.最后链路层发送状态机发送原语WTRM,等待设备端的校验结果,并将结果反馈到传输层[4].

2 加扰器模块的设计与实现

根据不同的需求,加扰器具体的实现结构与扰码值都不尽相同.SATA3.0协议给出了一种并行实现的算法.图2是SATA3.0协议给出的加扰器的实现结构,M1和M2是2个16×16的矩阵,协议规定了加扰器的初始值是十六进制数f0 f60 000,当拉高加扰器使能之后,M1、M2分别输出扰码值的高16位和低16位,并且M1输出的高16位值会赋值给寄存器REG,进行下一次扰码计算[5].

图1 发送模块顶层设计示意Fig.1 Transmit module top design diagram

图2 加扰器的实现结构Fig.2 Scrambler implementation structure

图3为加扰器的仿真图,本文用Verilog 硬件描述语言实现了加扰器模块.协议给出了加扰器产生的部分扰码序列,如表1所示.

图3 加扰器仿真Fig.3 Scrambler simulation diagram

图3表明,加扰器未在复位状态即rst=0,加扰器的使能端enable为1,并且当时钟上升沿来临时输出第1个扰码值,经过比对,用Verilog实现的加扰器产生的扰码值与协议给出的扰码序列一一对应,因此,加扰器模块满足协议的要求.

表1 扰码序列

3 CRC校验模块的设计与实现

CRC校验模块具有传输数据检错功能,通过对数据进行多项式计算,并将得到的结果附在帧的后面,接收设备也执行类似的算法,以保证数据传输的正确性和完整性.根据不同的需求,CRC校验模块的具体实现结构也不同.图4是SATA3.0协议给出的CRC校验模块的实现结构,协议规定了CRC校验的初始校验值是十六进制数52 325 032,当数据来临时,数据与寄存器REG中存储的CRC校验值进行异或运算,运算结果进入CRC计算逻辑块得到新的CRC校验值,新的CRC校验结果存放在REG中,当一帧数据CRC计算全部完成后,REG中的CRC校验和经过加扰后输出到帧数据末尾,否则REG中的CRC校验值始终与输入的数据进行异或运算,并计算新的CRC校验值,重复这一操作,直到一帧数据CRC计算全部完成[6].

图5是CRC校验模块的仿真图,本文用Verilog硬件描述语言实现了CRC校验块.协议给出了一组测试数据流,并给出了相应的CRC校验结果,如表2所示.

图4 CRC校验和的实现结构Fig.4 CRC checksum implementation structure

测试数据流CRC值0x003080270x11E353FD0xE12345670x0F656DA70x000000000x3D14369C0x000000020x92D0D6810x000000000x319FFF6F

图5 CRC校验块仿真Fig.5 CRC check block simulation diagram

图5表明,CRC校验块未在复位状态即rst=0,CRC校验块的使能端crc_en为1,并且时钟上升沿来临时开始计算并输出第1个CRC校验值,经过比对,用Verilog实现的CRC校验模块在数据流是0 x00 308 027、0 xE1 234 567、0 x00 000 000、0 x00 000 002、0 x00 000 000时输出的CRC校验值与协议给出的校验值相同,因此,CRC校验模块满足协议的要求.

4 链路层发送状态机的设计与实现

当主机向设备发送数据时,主机端链路层发送状态机根据传输层的发送请求,启动数据发送,通过各类原语的发送与接收实现主机与设备之间的数据传输与流量控制.链路层发送状态机共有9个状态:L_IDLE主机空闲状态、L_SendChkRdy主机发送准备就绪状态、L_SendSOF主机发送帧头原语状态、L_SendData主机发送数据状态、L_RcvrHold设备暂停接收状态、L_SendHold主机暂停发送状态、 L_SendCRC发送CRC状态、L_SendEOF发送帧结束原语状态和L_Wait等待设备校验状态[7].

链路层发送状态机状态转换如图6所示.

主机无操作时发送状态机处于L_IDLE状态.当主机端传输层需要向链路层发送数据时,发送请求信号,tx_request信号置1,状态机跳转到L_SendChkRdy状态,并发送X_RDYp原语.

状态机处于L_SendChkRdy状态时,当物理层反馈信号PhyRdy有效并且链路层接收到设备端反馈的R_RDYp原语时,说明设备端已准备好接收数据,并且主机端物理层准备就绪,链路层发送状态机跳转到L_SendSOF状态.

状态机处于L_SendSOF状态时发送帧头SOFp原语,并拉高链路层发送FIFO读使能和加扰器使能,链路层发送状态机跳转到L_SendData状态.

图6 状态转换Fig.6 State transition diagram

状态机处于L_SendData状态时发送数据,将数据与加扰器产生的扰码序列进行异或运算后发送给物理层,当设备端需要暂停接收数据时,主机端会接收到设备端反馈的HOLDp原语,状态机跳转到L_RcvrHold状态,并发送HOLDAp原语;当主机端数据没有发送完毕且FIS帧没有封装完成时,主机会暂停发送数据,状态机跳转到L_SendData状态,并发送HOLDp原语;当数据传输完毕时,即tx_request信号置0并且链路层发送FIFO的empty信号置1时,状态机跳转到L_SendCRC状态[8].

状态机处于L_SendHold状态时,当主机端FIS帧封装完成后,状态机跳转到L_SendData状态;当接收到设备端反馈的HOLDp原语时,状态机跳转到L_RcvrHold状态,并发送HOLDAp原语;当接收到设备端反馈的DMATp中断原语时,状态机跳转到L_SendCRC状态.

状态机处于L_RcvrHold状态时,设备端暂停接收数据,当主机端链路层接收到设备端反馈的非HOLDp原语数据时,状态机跳转到L_SendData状态.

状态机处于L_SendCRC状态时,将CRC值与扰码序列进行异或运算后发送给物理层,状态机跳转到L_SendEOF状态.

状态机处于L_SendEOF状态时,发送EOFp原语,状态机跳转到L_Wait状态.

状态机处于L_Wait状态时,发送WTRMp原语,并等待设备端反馈的校验结果,当主机端接收到设备端的校验结果之后,状态机跳转回L_IDLE状态.

本文没有单独对发送状态机模块进行仿真,而是在链路层发送模块仿真的过程中,通过输入不同的原语,实现了发送状态机的跳转,对数据的传输实现了流量控制,从而验证了发送状态机状态跳转的正确性[9].

5 仿真验证

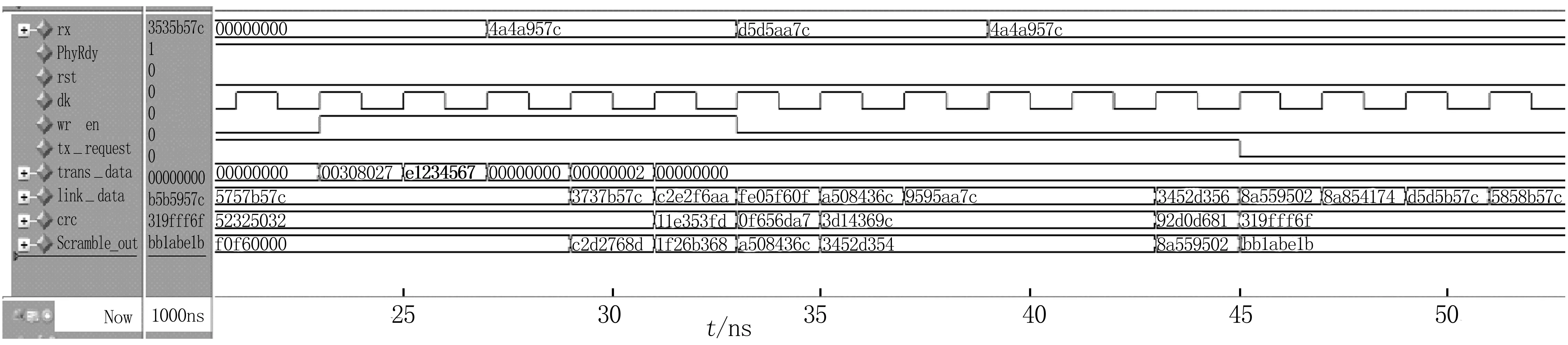

链路层发送模块具有主机端暂停发送数据状态的仿真图(图7),链路层发送模块具有设备端暂停接收数据状态的时序仿真图见图8.协议中给出了一组测试数据流,并且给出了数据在经过加扰之后的输出结果,如表3所示.

图7表明,当tx_request为1并且接收到设备端反馈的原语R_RDYp(4A 4A9 57C)时,link_data开始输出数据帧头SOFp原语(37 37B 57C),下一时钟link_data开始输出加扰后的数据,FIFO中写入了3个有效数据,当FIFO中的3个数据全部读出之后,FIFO的empty信号为1,但tx_request信号仍是1,主机端请求暂停发送数据,link_data发送HOLDp原语(D5 D5A A7C),在一定的时钟之后FIFO写使能为1,写入了2个数据,link_data输出加扰后的帧数据,当FIFO中的数据全部读出并且tx_request为0时,link_data输出加扰后的CRC校验和,下一时钟link_data输出数据帧尾EOFp(D5 D5B 57C),之后输出WTRMp(58 58B 57C)等待设备端反馈的校验结果.仿真结果和协议中给出的输出结果相同并完成了链路层流量控制,本设计满足SATA3.0协议链路层发送模块的功能要求.

图7 链路层发送模块仿真Fig.7 Link Layer sending module simulation diagram

FIS数据扰码加扰后数据FIS数据扰码加扰后数据3737B57CN/A3737B57C000000023452D3543452D35600308027C2D2768DC2E2F6AA000000008A5595028A559502E12345671F26B368FE05F60F319FFF6FBB1ABE1B8A85417400000000A508436CA508436CD5D5B57CN/AD5D5B57C

图8表明,当tx_request为1并且接收到设备端反馈的原语R_RDYp(4A 4A9 57C)时,link_data开始输出数据帧头SOFp原语(37 37B 57C),下一时钟link_data开始输出加扰后的数据,FIFO中写入了5个有效数据,当读出FIFO中3个数据之后,设备端请求暂停接收数据,设备端发送原语HOLDp(D5 D5A A7C),链路层接收到设备端的HOLDp原语,链路层不再读取FIFO中的数据,link_data发送HOLDAp原语(95 95A A7C),在一定的时钟之后链路层接收到设备端反馈的非HOLDp原语数据,link_data在下一时钟开始输出加扰后的帧数据,当FIFO中的数据全部读出并且tx_request为0时,link_data输出加扰后的CRC校验和,下一时钟link_data输出数据帧尾EOFp(D5 D5B 57C),之后输出WTRMp(58 58B 57C)等待设备端反馈的校验结果.仿真结果和协议中给出的输出结果相同并完成了链路层流量控制,本设计满足SATA3.0协议链路层发送模块的功能要求.

图8 链路层发送模块仿真Fig.8 Link Layer sending module simulation diagram

6 结论

选用Xilinx公司的FPGA芯片XC5VLX110T,并在开发环境Xilinx ISE中对其功能进行了仿真,仿真结果表明:所设计的SATA3.0协议链路层发送模块能够在1个时钟周期内正确处理1个四字节数据,即32位二进制数据,并且通过加扰、CRC校验功能保证了数据在链路层传输过程中的稳定性.由于XC5VLX110T芯片的参考时钟频率为150 MHz,经过物理层8b/10b编码后,设计的SATA主机端控制器的处理速度可达600 Mb/s,经并串转换后,串行传输速度可达6 Gb/s,完全符合SATA3.0协议的标准.

[1]范俊.基于FPGA的SATA控制器的研究与实现[D].武汉:华中科技大学,2006.

FAN Jun.Design and implementation of SATA adapter using FPGA[D].Wuhan:Huazhong University of Science & Technology,2006.

[2]高志.基于FPGA的SATAⅡ协议研究与实现[D].长沙:湖南大学,2009.

GAO Zhi.Research and realization of SATA II protocol based on FPGA[D].Changsha:Hunan University,2009.

[3]唐纯杰.SATA协议分析及其FPGA实现[D].长沙:湖南大学,2009.

TANG Chunjie.The research of serial ATA protocol and its FPGA implementation[D].Changsha:Hunan University,2009.

[4]陈才.基于FPGA的SATA主机端控制器的设计[D].武汉:华中科技大学,2011.

CHEN Cai.Design of SATA host controller based on FPGA [D].Wuhan:Huazhong University of Science & Technology,2011.

[5]朱佳齐.SATA II主机控制器IP核设计及FPGA实现[D]. 绵阳:中国工程物理研究院,2013.

ZHU Jiaqi.Design and implementation of SATA II host controller IP core based on FPGA[D]. Mianyang:China Academy of Engineering Physics,2013.

[6]王烨,张峰,李燕斌.SATA高速存储的FPGA实现[J].电讯技术,2012,52:1801-1804.DOI:10.3969/j.issn.1001-893x.2012.11.019.

WANG Ye,ZHANG Feng,LI Yanbin.A high-speed recording system of SATA based on FPGA[J].Telecommunication Engineering,2012,52:1801-1804.DOI:10.3969/j.issn.1001-893x.2012.11.019.

[7]吴从中,但德东,刘盛中.SATA3.0协议物理层握手模块设计与验证[J].合肥工业大学学报(自然科学版),2014,37:604-608.DOI:10.3969/j.issn.1003-5060.2014.05.020.

WU Congzhong,DAN Dengdong,LIU Shengzhong.Design and validation of SATA 3.0 physical layer’s handshake module[J].Journal of Hefei University of Technology(Natural Science),2014,37:604-608.DOI:10.3969/j.issn.1003-5060.2014.05.020.

[8]张庆顺,周拴柱,张锁良.基于FPGA的IP over CCSDS协议中长帧拆分的实现与仿真[J].河北大学学报(自然科学版),2015,35(2):204-209.DOI:10.3969/j.issn.1000-1565.2015.02.017.

ZHANG Qingshun,ZHOU Shuanzhu,ZHANG Suoliang.Implementation and simulation of FPGA-based IP over CCSDS protocol long frame split[J].Journal of Hebei University (Natural Science Edition),2015,35(2):204-209.DOI:10.3969/j.issn.1000-1565.2015.02.017.

[9]叶勃宏.基于FPGA的SATAII协议物理层实现[J].电子科技,2014,27(6):17-21.DOI:10.16180/j.cnki.issn.1007-7820.2014.06.036.YE Bohong.Realization of physical layer of SATAII based on FPGA[J].Electronic Sci &Tech,2014,27(6):17-21.DOI:10.16180/j.cnki.issn.1007-7820.2014.06.036.

(责任编辑:王兰英)

Design of FPGA-based SATA host controller in the link layer delivery

ZHANG Qingshun,LIU Zan,GUO Baozeng,ZHANG Suoliang

(Electronic Information Engineering College,Hebei University,Baoding 071002,China)

SATA(serial advanced technology attachment)3.0 disk as a data storage medium cannot be directly used in electronic systems represented by FPGA(Field-programmable gate array).Referring to ATA1-7,SATA serial advanced technology attachment 1.0,SATA2.0,SATA3.0 and other relavant protocols,this paper proposes a design and implementation method originated from SATA3.0 host controller which is based on FPGA in the link layer of sending module.This method is successfully implemented in sending data validation,scrambling and flowing control.Simulation results are also provided.The results show that the data processing speed of the controller is 600 MB/s which verify the success of the design.

FPGA;ATA protocol;SATA protocol;host controller

10.3969/j.issn.1000-1565.2016.02.018

2015-10-27

河北省自然科学基金资助项目(F2011201045)

张庆顺(1979—),男,陕西汉中人,河北大学讲师,主要从事通信系统的研究.E-mail:87086486@qq.com

张锁良(1966—),男,河北藁城人,河北大学教授,主要从事高速数据通信的研究.E-mail:zhangsl@hbu.cn

TP336

A

1000-1565(2016)02-0218-07