基于a-IGZO TFTs的低功耗D触发器设计*

姚若河 林少龙

(华南理工大学 电子与信息学院, 广东 广州 510640)

基于a-IGZO TFTs的低功耗D触发器设计*

姚若河 林少龙

(华南理工大学 电子与信息学院, 广东 广州 510640)

设计了一个基于Pseudo-CMOS逻辑门的低功耗异步复位D触发器电路.该D触发器全部由n型a-IGZO TFTs(薄膜晶体管)构成,采用动态负载替代Pseudo-CMOS拓扑中的二极管连接负载,通过减少电路导通的概率来降低静态功耗.电路的输出级为锁存器,通过反馈通路减少由动态负载造成的输出摆幅降低对延迟的影响.将该D触发器应用于环行移位寄存器的设计中,结果表明,该触发器电路可有效降低或非门逻辑电路中的静态功耗.

薄膜晶体管; D触发器; 动态负载; 移位寄存器

薄膜晶体管(TFTs)的有源层材料有非晶硅(a-Si∶H)、多晶硅(Poly-Si)、非晶氧化物和有机材料等.非晶硅由于迁移率低(约为1 cm2/(V·s))使其TFTs难以构建高速电路,而多晶硅和以非晶铟镓锌氧 (a-IGZO)为代表的非晶氧化物的迁移率比非晶硅高出一至两个数量级.但多晶硅中固有晶界的存在使其在大面积制备时难以保证好的均匀性.而a-IGZO TFTs具有大面积制备时均匀性好和迁移率较高的优点[1],可以在室温工艺温度下制备,并可直接在柔性廉价塑料衬底上制备[2].近年a-IGZO TFTs被广泛应用于有源矩阵液晶显示器[3]、有机发光二极管显示[4]、存储器[5]、射频识别技术[6- 7]、近距离无线通讯技术[8]等领域.

a-IGZO TFTs由于有源层材料存在内在施主,目前尚难于制备出性能一致的p型管和n型管[9],使其电路设计中不能运用现代CMOS电路设计技术.单极型TFTs逻辑电路设计中常见设计方法有二极管连接[6]和零点连接[10],但这两种设计存在较大静态功耗和较差噪声容限.为了优化电路性能,一些特殊结构的薄膜晶体管被提出,如双栅型结构[8,11- 12]、集成耗尽型/增强型结构[13]等.另一种优化方法是从电路结构进行,自举结构[14]、电平位移[12]、Pseudo-CMOS结构[15- 16]相继被提出.其中Pseudo-CMOS结构是目前TFT技术中性能较好的一种电路结构[16],可以在低供电电压下获取较高噪声容限和较高开关速度,但Pseudo-CMOS电路仍存在较大静电功耗,与CMOS电路在低功耗的对比中仍有一定的差距.

触发器是一个具有记忆功能、两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元.文中基于Pseudo-CMOS逻辑单元构建异步复位D触发器,采用动态负载代替Pseudo-CMOS拓扑结构中二极管连接负载,减少了电路中的静态功耗.

1 电路设计

1.1 异步复位D触发器

图1为一种仅用或非门实现上升沿触发并带有异步复位功能的D触发器[16].该D触发器将复位信号RST和时钟信号CLK经由门电路实现对输入D的控制,输出一对互补信号Q和Qb.通过对该触发器的分析,图中用虚线表示的传输线可以省略掉,进而或非门G4变为二输入.该传输线是为门G4提供输入D的反相信号,但是由于门G3输出至门G4传输线的存在,该传输线的去除并不影响原有的维持功能.

图1 异步复位D触发器

1.2 触发器门电路优化

Pseudo-CMOS逻辑单元是一种鲁棒性足够应对低成本柔性衬底和制造方法所造成的工艺偏差的电路结构.上述D触发器中采用Pseudo-CMOS逻辑结构的或非门构成.虽然对于n型TFTs而言,或非门的对地电导率更小,但相比与非门电路其在等概率输入下电路的导通概率更大,即由或非门构成的电路会产生更大的静态功耗.

图2(a)为Pseudo-CMOS逻辑单元的一个二输入或非门.当输入VIN1和VIN2同为低电平时,下拉网络(M2a、M2b、M4a、M4b)均截止,静态电流保持一个低的水平,输出电平由M2和M3按照电压跟随器的原理输出高电平.当输入VIN1和VIN2任一为高电平时,VIM被拉低,输出上拉管M3被截止,而下拉管M4a或M4b处于强导通状态,此时输出VOUT接近接地GND水平.通过引入额外电压源VSS进行后调节,改善电压转移曲线和输出摆幅.因此Pseudo-CMOS或非门能有效改善输出摆幅,具有无比逻辑的特性.

图2 两种二输入或非门的原理

如果存在输入VIN1或者VIN2的反向信号,将反向信号VIN_UP接入M1的栅极使得M1管由二极管接法负载变成动态负载,如图2(b)所示.由于在或非门电路中,只有在输入均为低电平时才需要由上拉管M1将VIM信号上拉,所以该电路仍能实现或非逻辑,且在输入等概率情况下电路的导通概率由3/4降低至1/4.该电路由于输入的反向信号最高等于电源电压VDD,不能配合额外电压源VSS进行后调节,输出摆幅不能达到轨至轨.

由于门G5与G6构成锁存器存在反馈通路对输入的高电平不敏感,且图1的D触发器电路中门G3和门G4都存在输入方向的信号,因此可采用动态负载结构,具体电路分别对应图3(a)和(b).图3(a)中仅当VG2为高电平,RST或CLK也为高电平时,M1和M2a同时打开,才会有静态电流形成.同理,图3(b)中在VG2为高电平且VG3也为高电平时,M1和M2a同时打开,才会形成导电通路.

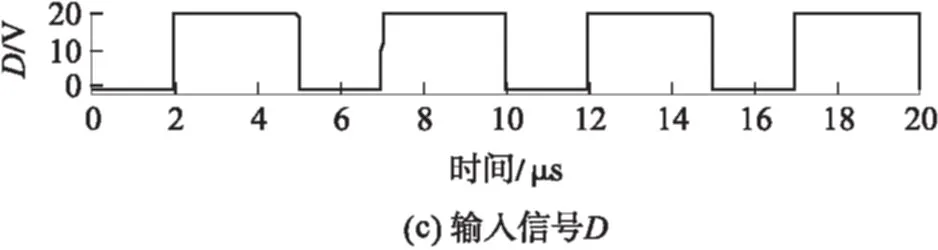

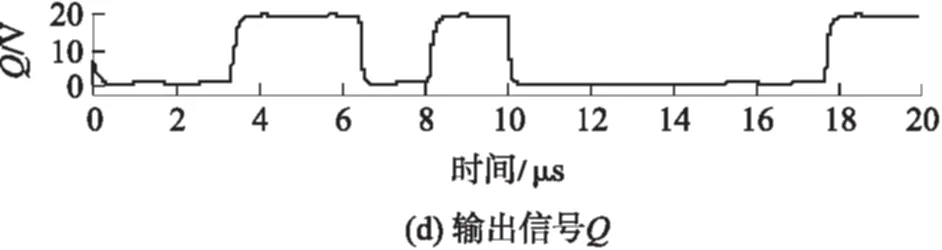

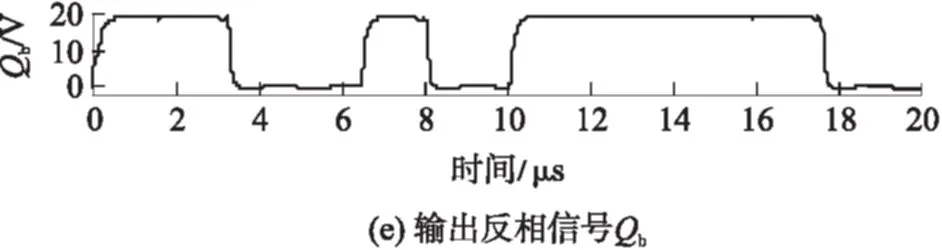

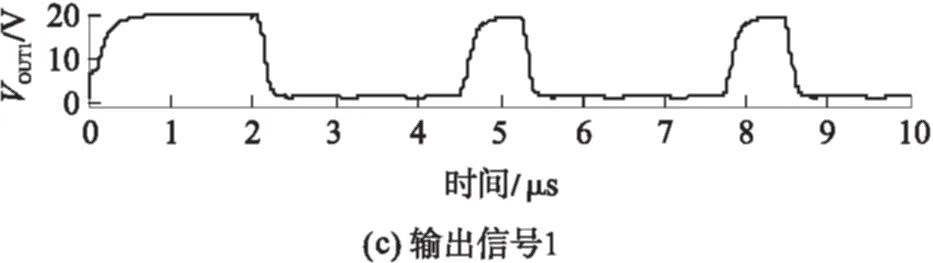

图4是动态负载D触发器在625kHz频率的时钟信号下的仿真时序图,图4(a)-(c)分别是时钟信号CLK、复位信号RST、输入信号D的时序图.图4(d)和(e)是输出信号Q和Qb的时序图.可见采用动态负载D触发器输出摆幅仍能达到轨至轨,并未受门G3、G4输出高电平降低的影响.

图3 两个采用动态负载Pseudo-CMOS的逻辑门

Fig.3 Two logic gates using dynamic load in Pseudo-CMOS

图4 D触发器的仿真时序图

1.3 环行移位寄存器

移位寄存器在柔性电子产品比如RFID标签中作为一个重要的功能块,可以由D触发器实现.如图5所示.该电路使用D触发器实现一个四位并行输出的环行移位寄存器.在射频识别(RFID)标签中,移位寄存器用以产生位选信号读取只读存储器(ROM)中数据[16].该环行移位寄存器可以自发产生位选信号,可以通过RST复位恢复至初始位选信号.图6为该移位寄存器的仿真时序图.图6(a)和(b)分别为输入时钟信号CLK和复位信号RST,图6(c)-(f)为环行移位寄存器的四位平行输出.通过环行移位寄存器可以检测出在具体电路中动态负载D触发器的功耗和延迟表现.

图5 并行输出环行移位寄存器

图6 环行移位寄存器仿真时序图

2 仿真结果与讨论

为了对不同拓扑结构的单极型D触发器[10,16- 17]的性能进行比较,参与对比分析的D触发器都采用了Pseudo-CMOS逻辑结构,并在hspice仿真器中进行仿真.由于目前没有a-IGZO TFTs的spice模型, 仿真过程中使用的模型是通过提取到相应的a-IGZO TFTs的数据对Rensselaer Polytechnic Institute(RPI) a-Si∶H TFT模型的参数修改得到[18- 19].该晶体管的主要参数为:迁移率μo=38.7 cm2/(V·s),阈值电压VTH=2.557 V,亚阈值摆幅S=0.223 5 V/dec.

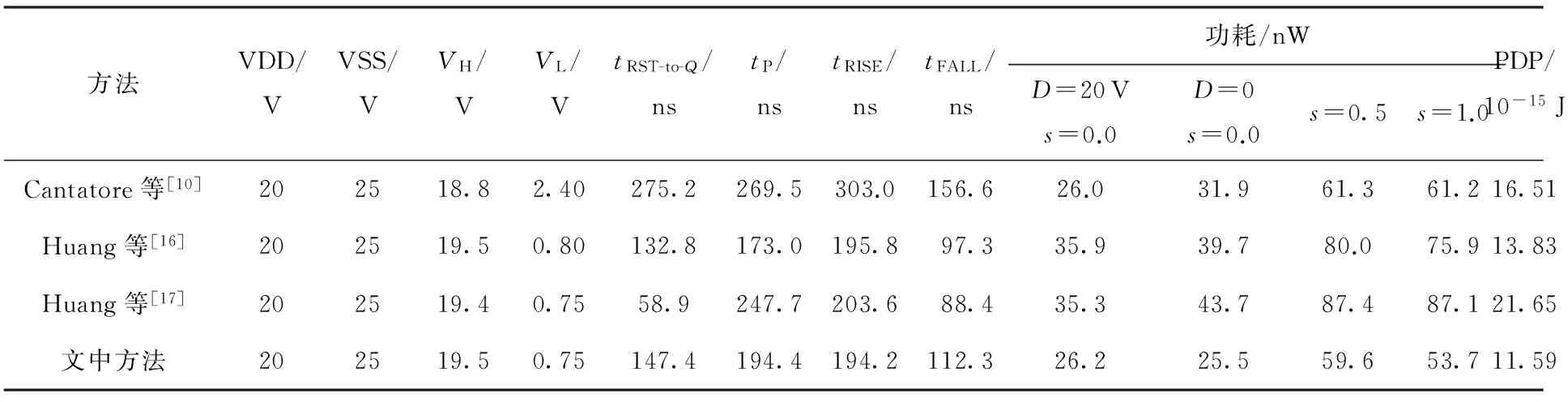

表1给出不同D触发器在625 kHz时钟信号下的仿真结果. 表1中:VH和VL分别代表输出最大电压和最低电压;tRST-to-Q和tP分别为复位延时和传播延时;tRISE和tFALL分别为输出上升和下降时间;s为数据开关活动性,表示在一定时间内输出数据改变次数与时钟触发沿到达触发器的个数之比.s=0.5代表每经过两个时钟触发沿,输出数据才改变1次,s=0.0表示输入恒定不变.从表1中可知,Huang等[17]采用nMOS传输管和反相器构成的D触发器在输出恒为高电平时略低于或非门方案[16],其他情况下功耗都是最大,而采用动态负载的D触发器仅在输入恒为高电平时(D=20V,s=0.0)和Cantatore等[10]的功耗接近,其他情况中功耗均为最小.由于采用动态负载D触发器与Huang等[16]都由或非门构成,从表1中可以发现,两种触发器在输出信号的各自延时均表现较好.动态负载D触发器中锁存器的输入没有达到最高摆幅会影响延迟,但从表1中可以看出,因为锁存器正反馈通路的存在对延迟影响不明显,仍保持或非门在延迟方面的良好性能.在功耗延迟积(PDP)方面,动态负载D触发器具有最低的值.

表1 D触发器仿真结果对比1)

1)仿真中所有门电路中管M1、M2、M3、M4的长度为8 μm,宽度设为24、72、80、80 μm,门电路中多输入管的管宽一致.

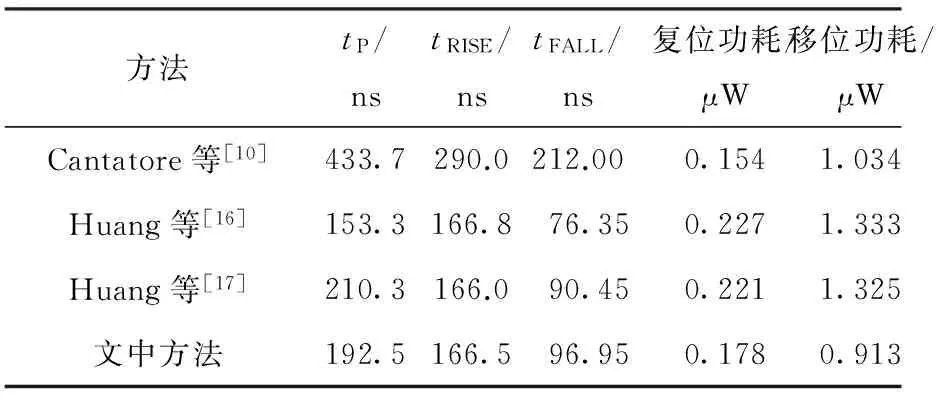

表2给出不同触发器构成环行移位寄存器在1.25 MHz时钟信号下经过10 μs仿真时间的仿真结果.动态负载D触发器构成的移位寄存器保持了或非门电路在延迟方面优势,同时相比其他3种D触发器在移位功耗上分别减少了13.3%、46.0%和45.1%.

表2 环行移位寄存器仿真结果对比

3 结语

文中在Pseudo-CMOS逻辑结构的门电路中采用动态负载减小门电路的导通概率,实现低功耗D触发器.该D触发器全部由n型a-IGZO TFT管构成,其中锁存器通过反馈通路减少由动态负载造成的输出摆幅降低对延迟的影响.最后在Hspice仿真器中进行仿真.从仿真结果可见,在n型MOS管电路中采用动态负载D触发器可以在保留或非门电路延迟优势的同时有效降低或非门逻辑电路中静态功耗,平衡单极型电路设计中与非门电路和或非门电路延迟和功耗的矛盾.

[1] HSING H H,HSING H L,HUNG C T,et al. Development of IGZO TFTs and their applications to next-generation flat-panel displays [J].Journal of Information Display,2011,11(11):160- 164.

[2] NOMURA K,OHTA H,TAKAGI A,et al. Room-tempera-ture fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors[J].Nature,2004,432(7016):488- 92.

[3] LEE J H,KIM D H,YANG D J,et al. 42.2: World’s largest (15- inch) XGA AMLCD panel using IGZO Oxide TFT [C]∥Proceedings of SID Symposium Digest of Technical Papers.Los Angeles: SID,2008∶625- 628.

[4] KWON J Y,SONK S,JIS J,et al. Bottom- gate gallium in- dium zinc oxide thin- ilm transistor array for high- resoluti- on AMOLED Display [J].IEEE Electron Device Letters,2008,29(12):1309- 1311.

[5] YIN H,KIM S,CHANG J K,et al. Fully transparent non- volatile memory employing amorphous oxides as charge trap and transistor’s channel layer [J].Applied Physics Letters,2008,93(17):172109.

[6] YANG B D,OH J M,KANG H J,et al. A transparent logic circuit for RFID tag in a-IGZO TFT technology [J]. Etri Journal,2013,35(4):610- 616.

[7] ZONG Z,LI L,JIN J,et al. A new surface potential- based compact model for a- IGZO TFTs in RFID applications[C]∥Proceedings of Electron Devices Meeting.San Francisco:IEEE,2014:35.5.1- 35.5.4.

[8] MYNY K,TRIPATHI A K,JAN- LAURENS V D S,et al. Flexible thin- film NFC tags [J]. IEEE Communications Magazine,2015,53(10):182- 189.

[9] CONLEY J F. Instabilities in amorphous oxide semiconductor thin- film transistors [J].IEEE Transactions on Device and Materials Reliability,2011,10(4):460- 475.

[10] CANTATORE E,GEUNS T C T,GRUIJTHUIJTHUIJSE A F A,et al.A 13.56- MHz RFID system based on organic transponders [C]∥ Proceedings of IEEE International Solid- State Circuits Conference.San Francisco: IEEE,2006:84- 92.

[11] 蔡旻熹,姚若河.双栅非晶InGaZnO薄膜晶体管有源层厚度对电学性能的影响 [J].华南理工大学学报

(自然科学版),2016,44(9):61- 66. CAI Min- xi, YAO Ruo- he.Effects of active layer thickness of dual-gate amorphous InGaZnO thin film transistors on their electrical characteristics [J].Journal of South China University of Technology(Natural Science Edition),2016,44(9):61- 66.

[12] RAITERI D,VAN LIESHOUT P,VAN ROERMUND A,et al.Positive- feedback level shifter logic for large- area electronics [J].IEEE Journal of Solid- State Circuits,2014,49(2):524- 535.

[13] YIN H,KIM S,PARK J,et al.High performance low voltage amorphous oxide TFT enhancement/depletion inverter through uni- /bi- layer channel hybrid integration[C]∥Proceedings of Electron Devices Meeting.Baltimore: IEEE,2009:1- 4.

[14] YIN H,KIM S,CHANG J K,et al.Bootstrapped ring oscillator with propagation delay time below 1.0nsec/stage by standard 0.5 μm bottom-gate amorphous Ga2O3- In2O3- ZnO TFT technology [C]∥ Proceedings of IEEE International Electron Devices Meeting.San Francisco: IEEE,2008:1- 4.

[15] HUANG T C,CHENG K T.Design for low power and reliable flexible electronics: self- tunable cell- library design [J].Journal of Display Technology,2009,5(6):206- 215.

[16] HUANG T C,FUKUDA K,Lo C M,et al.Pseudo- CMOS: a design style for low- cost and robust flexible electronics [J].IEEE Transactions on Electron Devices,2011,58(1):141- 150.

[17] HUANG T C,CHENG K T,BEAUSOLEIL R.Process- variation tolerant flexible circuit for wearable electronics [C]∥ Proceedings of IEEE International Symposium on Circuits and Systems.Montreal:IEEE,2016.

[18] JEONG H,MATIVENGA M,SANG G L,et al.Design of a low-power-consumption a-IGZO TFT-based V com driver circuit with long- term reliability [J].Journal of the Society for Information Display,2011,19(11):825- 832.

[19] SHUR M S,SLADE H C,JACUNSKI M D,et al.SPICE models for amorphous silicon and polysilicon thin film transistors [J].Journal of the Electrochemical Society,1997,144(8):2833- 2839.

Design of a Low-Power Consumption D Flip-Flop on the Basis of a-IGZO TFTs

YAORuo-heLINShao-long

(School of Electronic and Information Engineering, South China University of Technology,Guangzhou 510640,Guangdong,China))

Proposed in this paper is a low-power consumption D flip-flop circuit with asynchronous reset on the basis of Pseudo-CMOS logic gates, which consists of n-type a-IGZO TFTs (Thin Film Transistors), replaces the dio-deload in Pseudo-CMOS topology with dynamic load, and decreases the static power consumption by reducing the conduction probability of the circuit.The output stage of the circuit is a latch, and the effect of dynamic load-caused output swing decrement on the delay is reduced through a feedback path.The proposed D flip-flop is then applied to the design of a ring shift register.The results show that the trigger circuit can reduce the static power consumption in NOR gate logic circuit effectively.

thin film transistor; D flip-flop; dynamic load; shift register

2016- 05- 29

国家自然科学基金资助项目(61274085);广东省科技计划项目(2015B090909001) Foundation items: Supported by the National Natural Science Foundation of China(61274085) and the Science and Technology Research Projects of Guangdong Province(2015B090909001)

姚若河(1961-),男,教授,博士生导师,主要从事集成电路系统设计、半导体物理及器件研究.E-mail:phryao@scut.edu.cn

1000- 565X(2017)03- 0042- 06

TN 44

10.3969/j.issn.1000-565X.2017.03.006