一种高性能电荷泵锁相环电路的设计与实现

唐玉兰,陈建慧,赵 吉

(1.无锡职业技术学院,江苏 无锡 214121;2.无锡城市学院,江苏 无锡 214151;3.江南大学 物联网工程学院,江苏 无锡 214122)

集成电路技术的不断发展和工艺的进步,对频率合成器提出了更高的要求[1-2].频率合成器是现代电子系统的关键电路,决定着电子系统的性能.频率合成可以采用直接频率合成、锁相频率合成、直接数字式频率合成和混合频率合成这4种不同的方法[3],目的都是为了生成高准确度的信号.其中,锁相环频率合成器[4-5]包含滤波器、可控分频器(divider)[6]、鉴相器(Phase detector, PD)、压控振荡器(Voltage control oscillator, VCO)及前置分频器等功能单元,常用来生成高质量的高频时钟,实现倍频.锁相环路(Phase locked loop, PLL)特别是电荷泵(charge-pump)锁相环[7]因具有功耗低、稳定性高、容易集成等优点,应用最广泛,成为倍频信号产品的主流.

文中基于SMIC 0.18 μm CMOS工艺,设计了一款可编程控制电荷泵锁相环电路作为时钟倍频器,它的输出频率范围大,可动态调节的范围多,锁相可调节频率最高可达2.2 GHz,具有重要的理论意义和实际应用价值.在高速锁相环设计过程,采用创新的延迟可控相频鉴相器,使得电路既能够检测到小的相位差,又不会由于电流失配而造成控制电压的周期性震动;采用优化的差分输入-单端输出电荷泵,能有效抑制噪声,并且线性度突出,功耗小;采用6路可配置压控振荡器电路结构,有效控制了VCO的增益,从而控制频率调整范围.

1 可编程锁相环系统结构设计

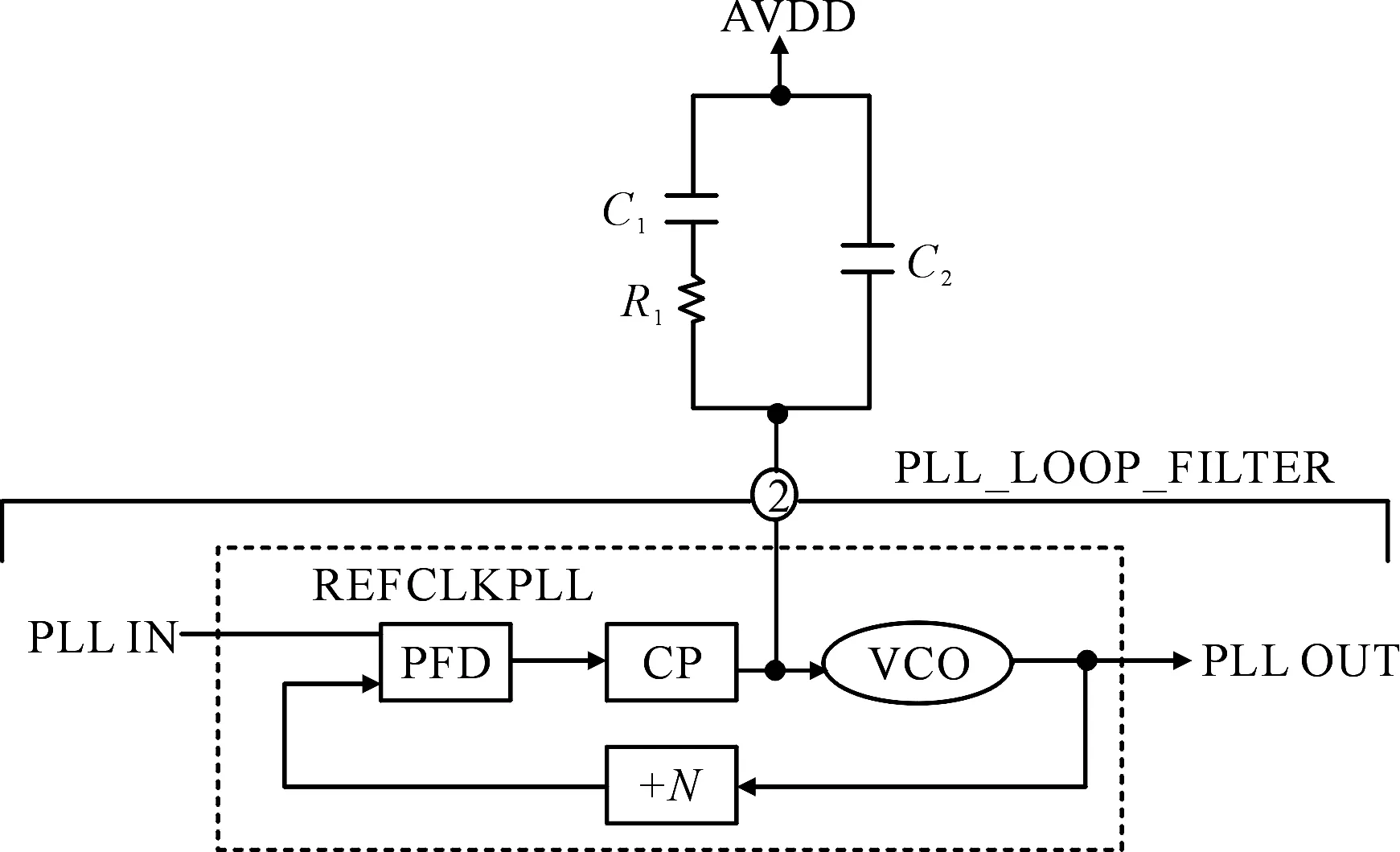

可编程锁相环模块核心由分频器、鉴频鉴相器(PFD)、电荷泵和压控振荡器几个部分组成,系统结构框图如图1所示.它作为倍频器使用可提供系统时钟,输出频率范围在420 MHz~2.2 GHz.可编程控制锁相环与普通锁相环的区别是它能够输出的频率范围大,可动态调节的范围多.该电荷泵与普通电荷泵的不同点在于,为了达到可编程宽频锁相的目的,电荷泵电流与VCO调节级数都是数字可控可调节的.

电路通过输入编程控制字调节倍频,通过N[6:0]产生12~127倍的控制范围.IC[2:0]可提供8种不同的电荷泵电流以改善PLL的性能.通过VC[2:0]可选择多达6种VCO,针对不同输出信号频率选择相应的VCO,可有效缩短信号锁定时间.鉴相器可比较参考时钟与分频后的输出时钟的频率及相位差,通过电荷泵输出信号控制压控振荡器,直至最后相位、频率锁定(图1).锁定后输出信号频率为参考时钟的N倍.

2 核心电路设计

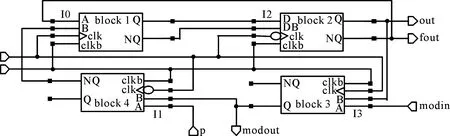

2.1 分频器设计

分频器需要产生12~127倍的分频信号,因此常用的二分频电路不适用于本电路.采用了2/3分频电路[8],并作了相应的改进,使其适合串联使用(图2).

图1 可编程锁相环结构框图

图2 分频器结构

因为N个串联的2/3分频器的分频比的范围只能为2N~(2N+1-1),因此要实现16~127的分频比,必须把它分成3部分:16~31,32~63,64~127.同时需要串联的2/3单元个数依次为4,5,6个.但是在信号输入时,必须有一个输入选择电路和输出选择电路(图3).

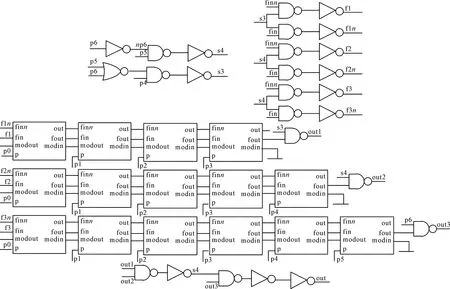

2.2 鉴相器设计

可编程锁相环设计采用时序鉴相器(图4),该电路锁相环的创新点在于当锁相环锁住之后,控制电压几乎不变,而传统电路的控制电压一般会有周期性的波动.该电路主要包含2个D触发器、1个与门电路和1个缓冲器.该电路的工作过程是:先把2个D触发器的数据端都设置为1,R作为基准输入信号,V作为反馈信号,这2路信号经过与非门翻转后,分别作为这2个D触发器时钟端的输入信号,输出分别为UP和DN.如果输入的时钟触发沿正确,那么相应的D触发器的数据端都被置1,如果门电路检测出2个触发器的输出端同时为TRUE,那么就会通过反馈,把2个D触发器的数据端同时置0.

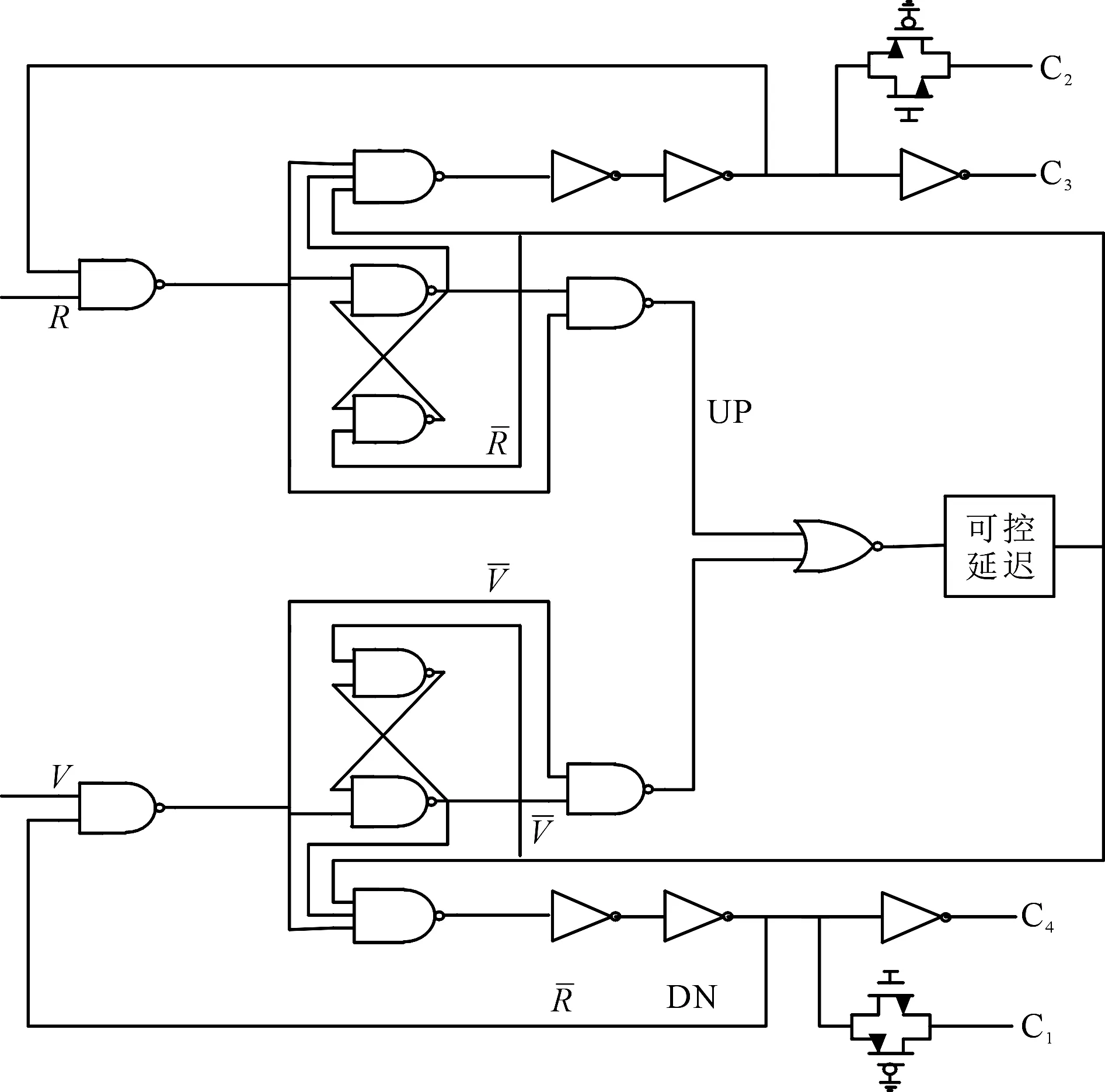

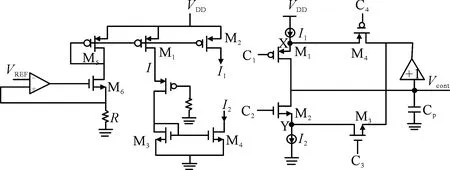

2.3 电荷泵电路设计

因为电荷泵电路本质上作为一个开关电流源使用,所以能完成理想的开关功能和作为精确稳定的恒流源最重要.CMOS电荷泵按照结构来分类,主要可以分为单端输出电荷泵和全差分电荷泵.为了减少功耗和面积消耗,选择了差分输入-单端输出结构的电荷泵(图5).

图3 分频器的总体电路

图4 鉴相器的电路结构

当C1为低电平,C2为低电平时,开关S1打开,电源通过电流源I1向Cp充电,Vcont电压升高.当C1为高电平,C2为高电平时,开关S2打开,Cp通过电流源I2放电,Vcont电压降低.

图5 电荷泵结构电路

由于2个电流源内部存在一定的电容(M1,M2),如果没有C3,C42个开关,即使电流源内部的电容相等并且I1=I2,VX和VY的变化量也不相等.当Vcont比较高时,CP反映的是VX和VY之间的差,这时VX变化量大,而VY变化量小,这就是电荷共享现象.

M3,M4以及单倍增益的运放可以解决电荷共享作用,C3,C42个开关的开关情况正好和C2,C1的开关情况相反,当C1打开的时候,C4关闭, 电压通过开关C4加到X点,下次C1关闭的时候,Vcont的电压只要从上一点的电压的基础上进行变化,而不用从电源点变化,减小了电压的波动.依此类推,Y点的电压也是如此.

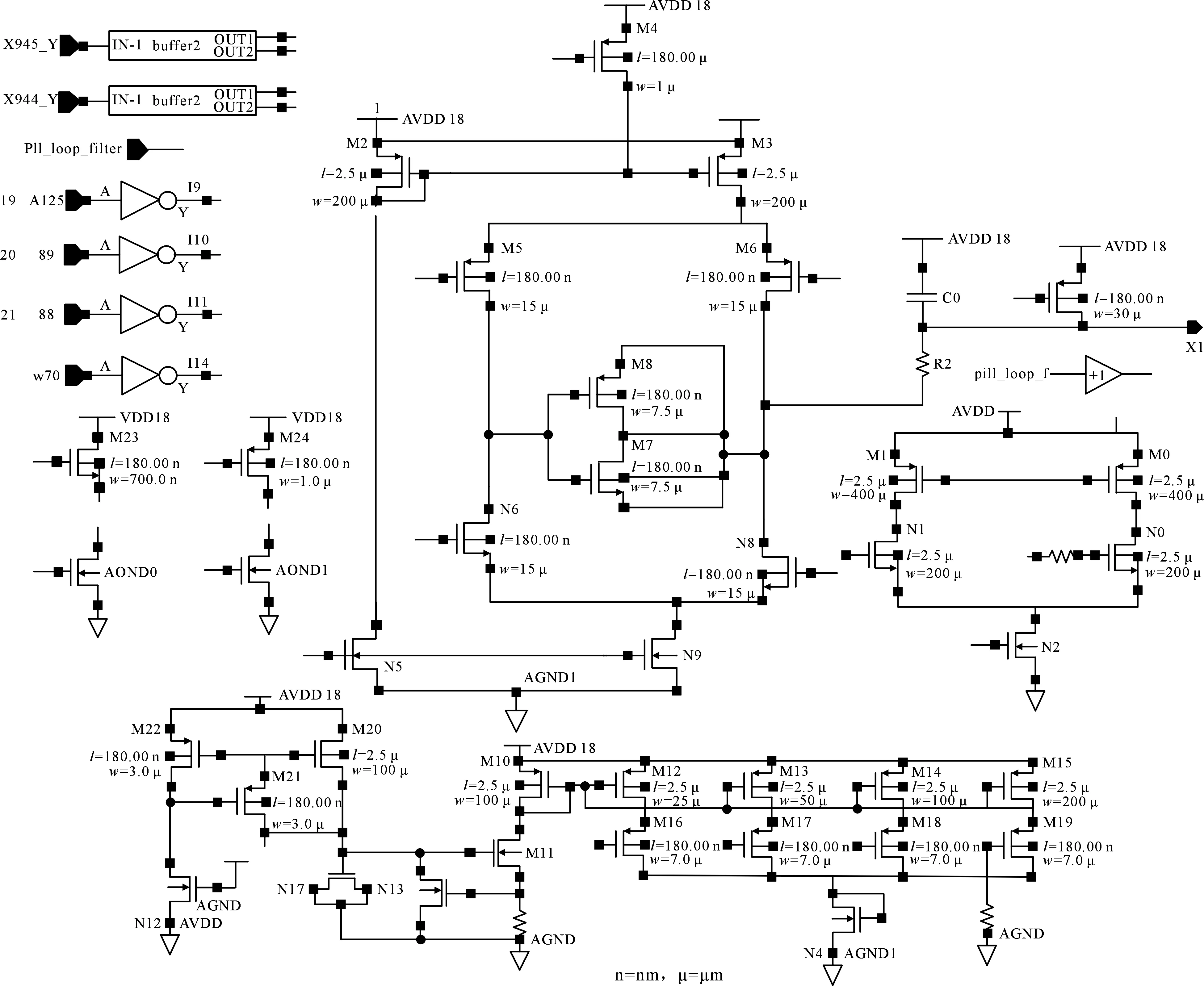

图6是电荷泵电路的详细电路图,图中充放电电流Icp可以通过外接信号IC[2:0]进行调节,在电路图上表示为(19,20,21).

图6 电荷泵结构详细电路

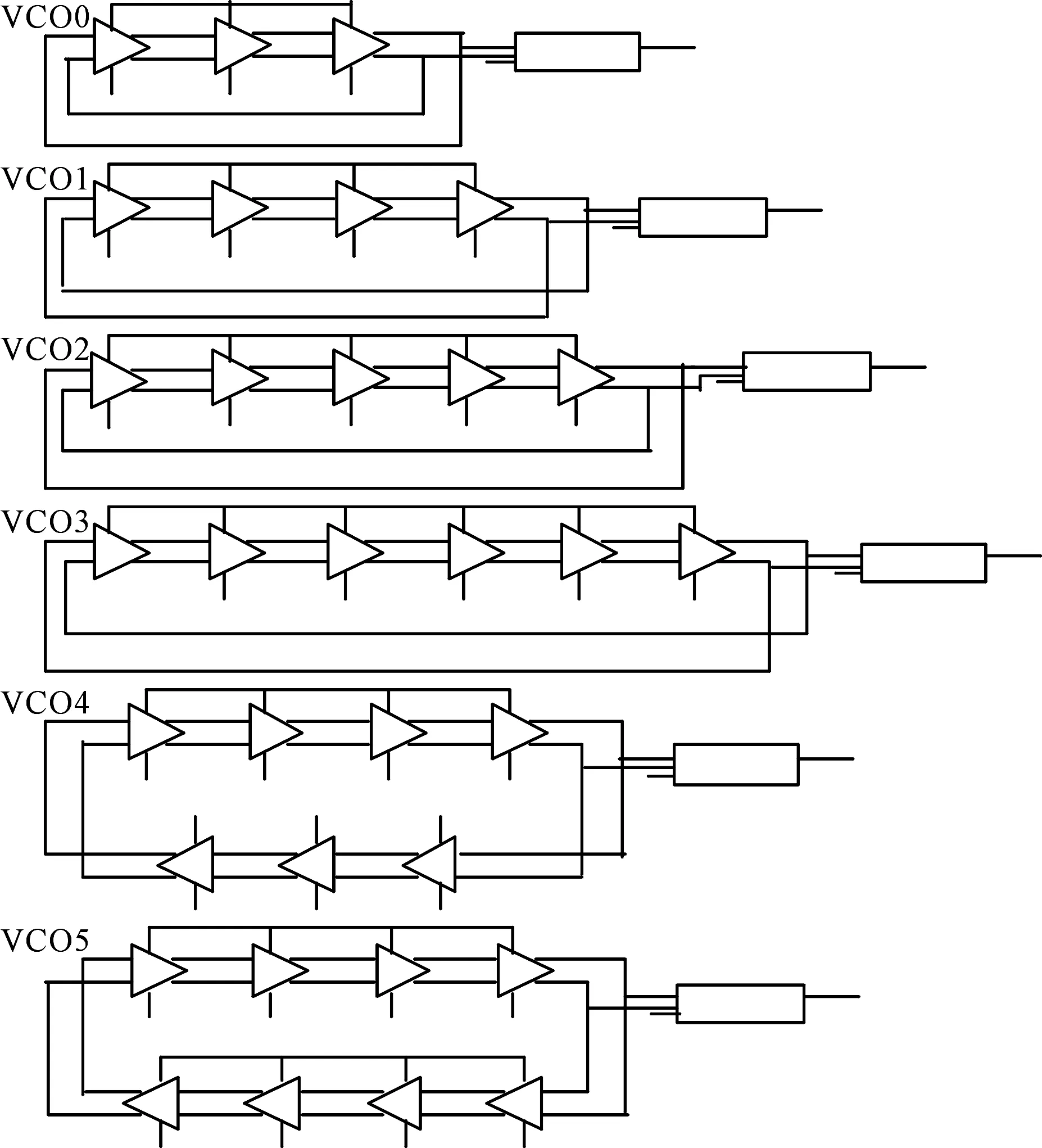

2.4 压控振荡器电路设计

电路采用多级环形压控振荡器结构,该结构单位集成度高,所占面积小,并且调谐范围较宽.因为差分结构具对称性和抑制噪声的优点[9],因此选择差分结构环型压控振荡器.由于PLL的倍频倍数非常大,为了保证电路的带宽范围,采用多级(3,4,5,6,7,8级运放串联)的VCO结构(图7).

2.5 环路滤波器电路设计

环路滤波器在PLL电路中具有重要的作用.这里的PLL环路滤波器[10]为外接,具有更高的适应性,便于优化PLL性能(图8).

通过加入环路滤波器,使得Ⅱ型锁相环变成了三阶的结构,这种结构有效避免了二阶结构带来的时钟馈通和电荷注入带来的相位抖动.R1,C1,C2的计算式为

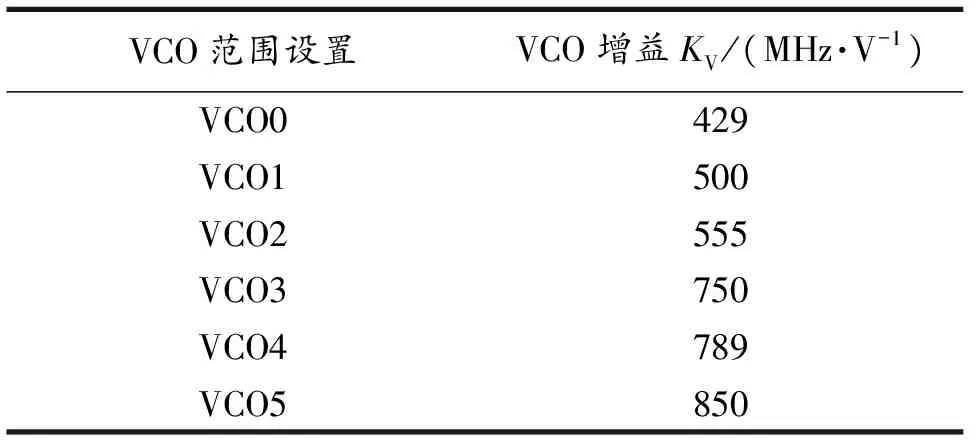

其中,N为分频值;KD为鉴相器增益(Hz·V-1);KV为压控振荡器增益(Hz·V-1);fOL为开环带宽(Hz);φ为相位裕度.表1列出了IC[2:0]可提供的8种不同的电荷泵电流值,表2列出了不同的VCO设置所对应的VCO增益.

对于Icp=287 μA,KV=625 MHz,N=25,开环带宽50 kHz,相位裕度45°,可得R1=52.85 Ω,C1=145.4 nF,C2=30.11 nF.

图7 多级压控振荡器电路

图8 环路滤波器结构示意

ICP(IC[2:0])电荷泵电流值/μA000212001237010262011287100312101337110363111387

3 版图设计

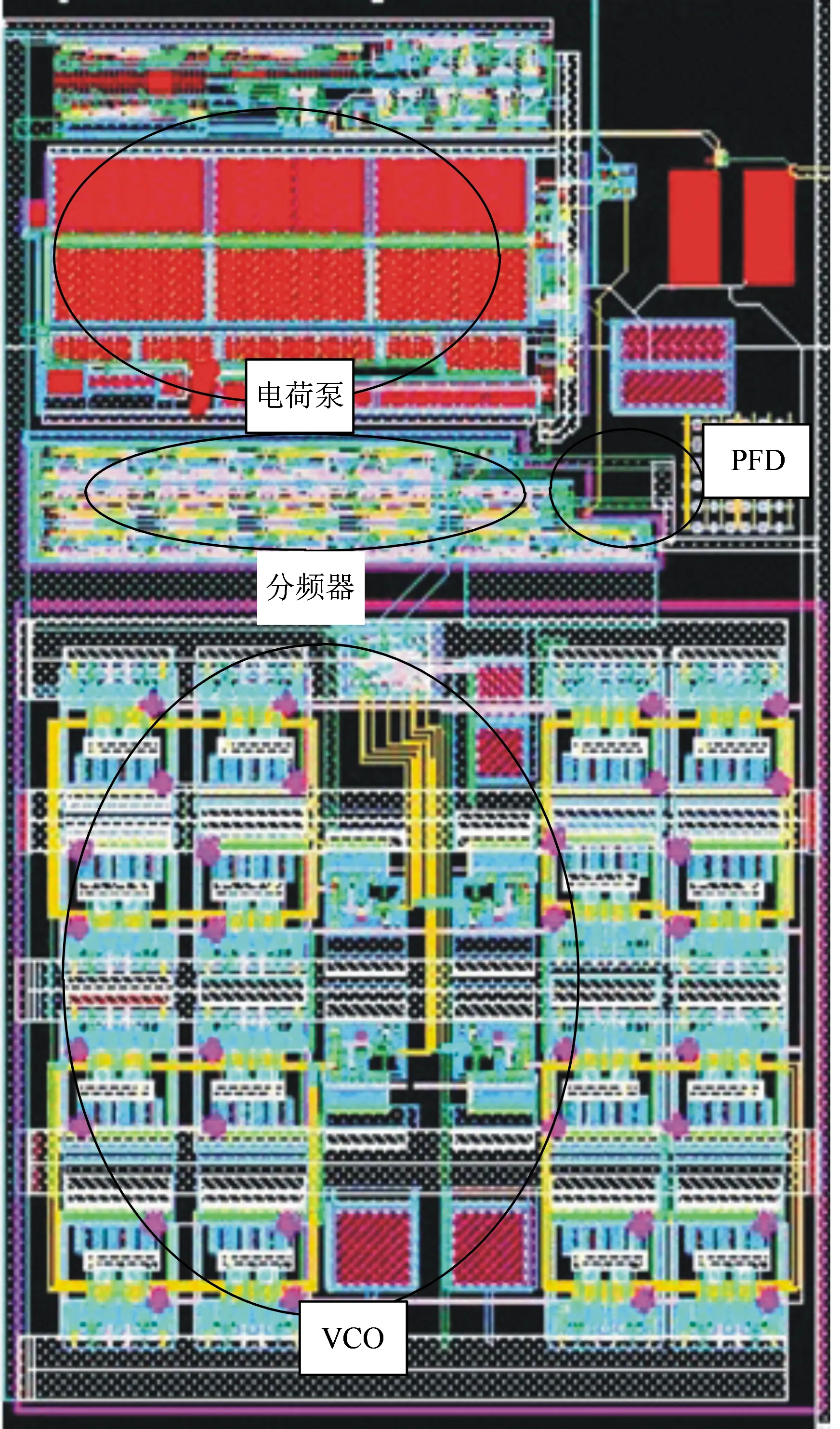

设计的电荷泵可编程锁相环版图如图9所示,综合考虑了包括面积、模拟和数字电路的隔离在内的各方面因素.由于压控振荡器和分频器工作频率较高,产生噪声也较大,因此这2个器件都加了隔离保护环.电荷泵也加了隔离保护环,以避免相邻器件对电荷泵衬底产生扰动.

表2 VCO增益

图9 可编程锁相环版图

4 实验仿真

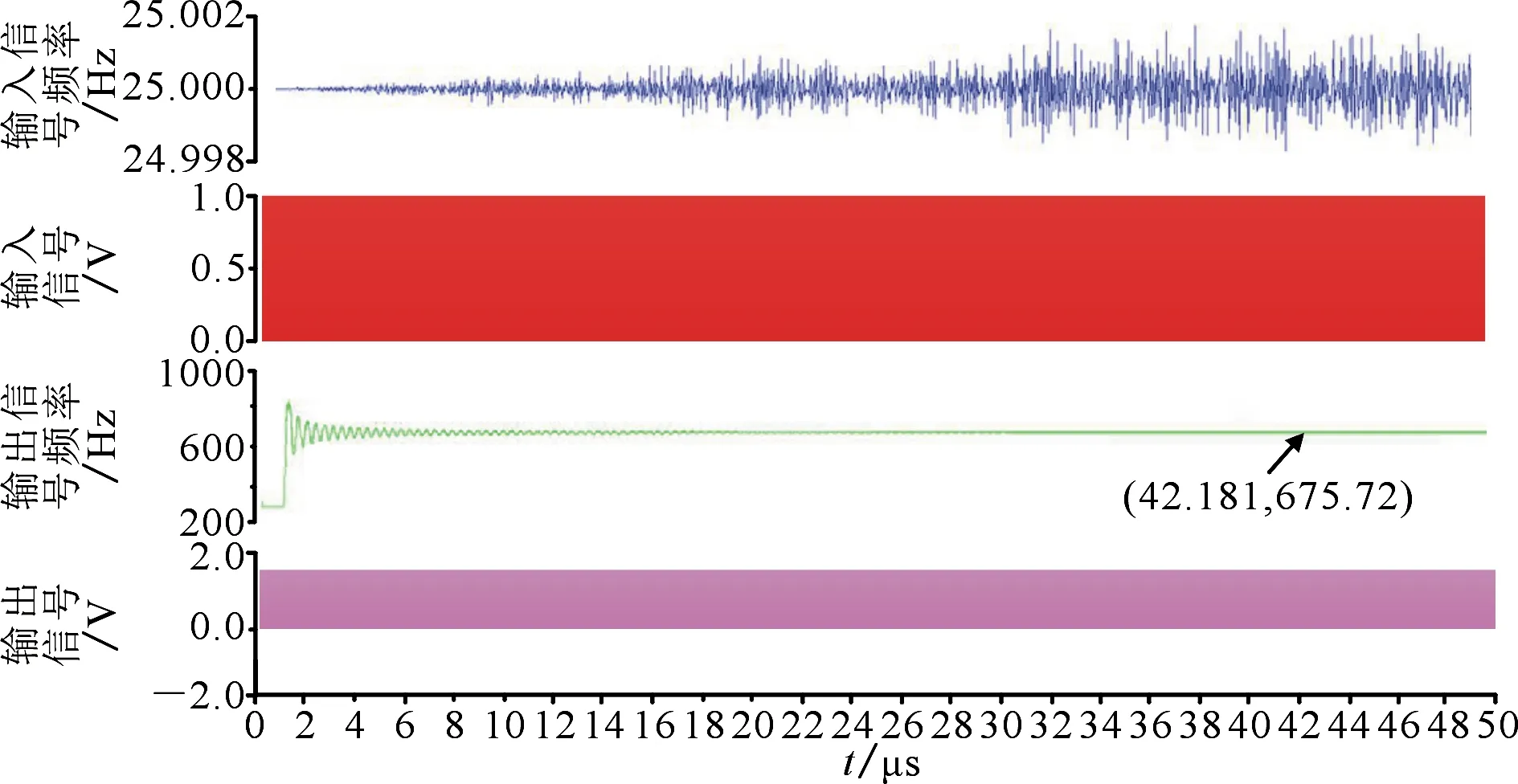

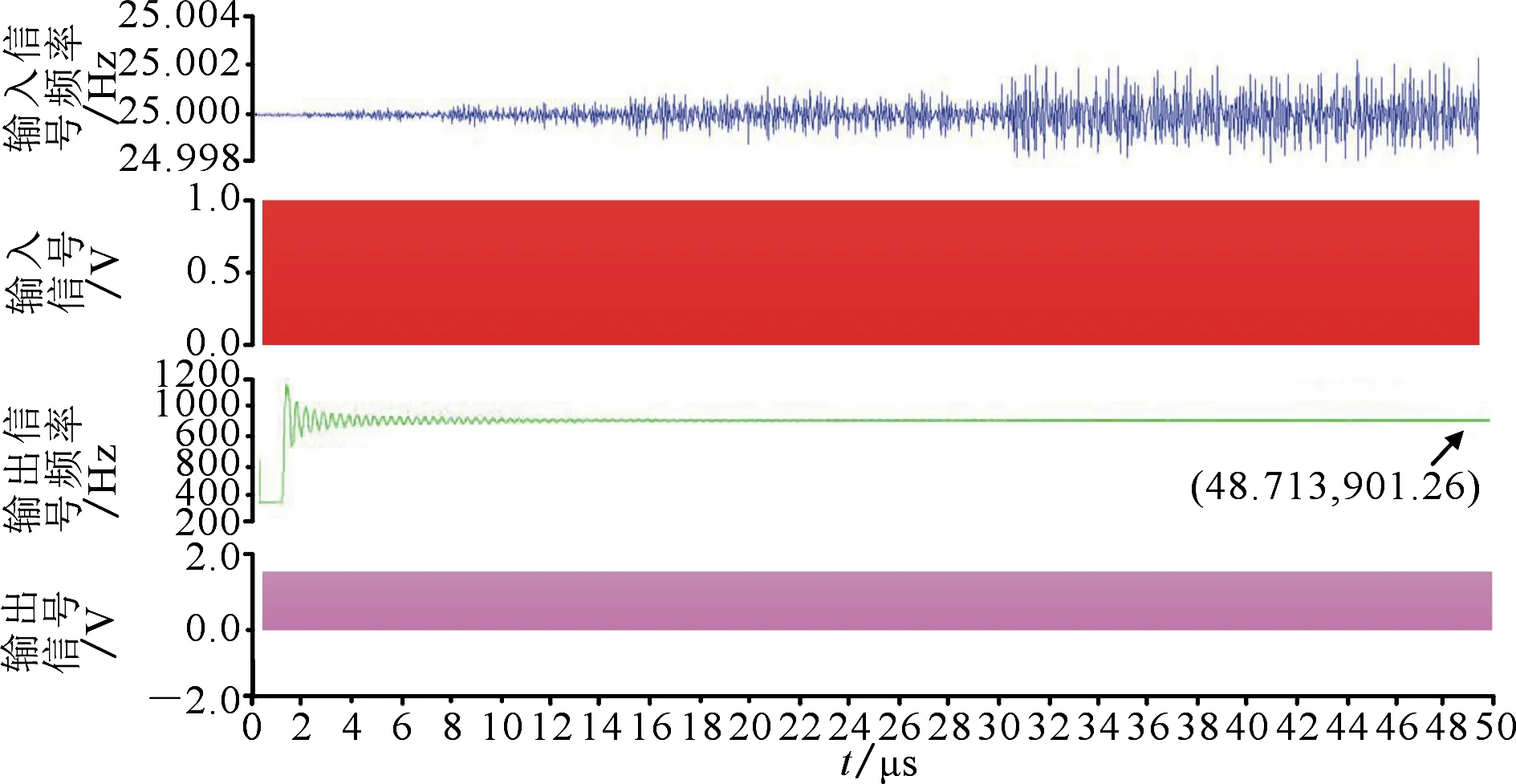

采用Synopsys Hspice工具对电荷泵锁相环电路进行整体仿真,波形采用Synopsys Cosmos工具.图10是锁相环频率锁定在675 MHz的仿真波形图,其中输入信号频率稳定在25 MHz,输出信号频率为一阻尼振荡曲线,它输出了时钟频率稳定在675.72 MHz的输出频率响应曲线,通过该曲线可以看出在约48 μs PLL频率稳定.

图10 锁相环整体仿真波形(输出频率=675 MHz)

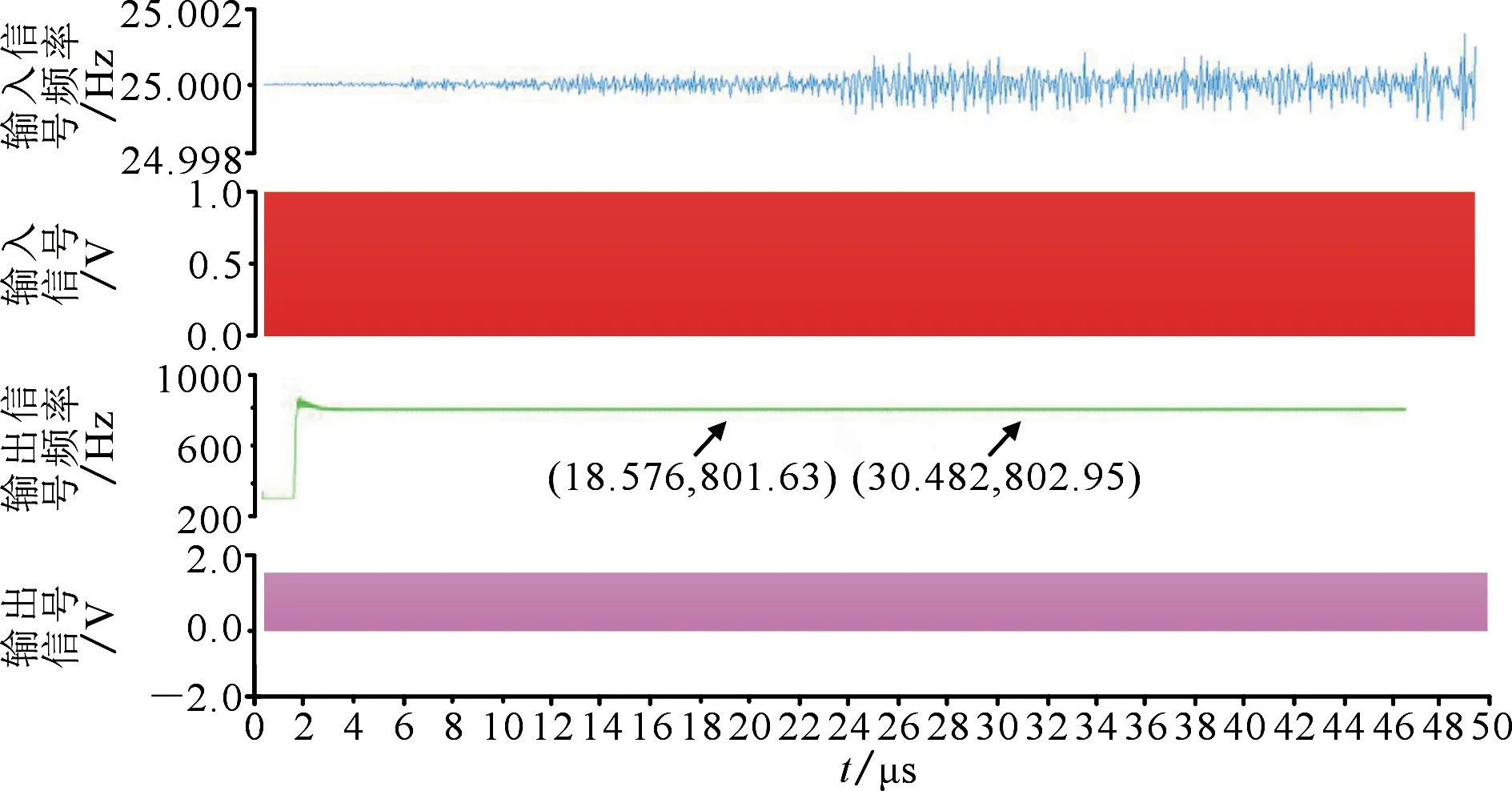

图11是锁相环频率锁定在800 MHz的仿真波形图,其中阻尼振荡曲线是输出时钟频率稳定在802.95 MHz的输出频率响应曲线,通过该曲线可以看出在约30 μs PLL频率稳定.

图11 锁相环整体仿真波形(输出频率=800 MHz)

图12是锁相环频率锁定在900 MHz的仿真波形图,其中阻尼振荡曲线是输出时钟频率稳定在901.26 MHz的输出频率响应曲线,通过该曲线可以看出在约49 μs PLL频率稳定.

图12 锁相环整体仿真波形(输出频率=900 MHz)

从仿真波形可以看出, 所设计的PLL作为可编程倍频器可调节范围宽,在电路中起到系统采样时钟的作用,整体仿真表明本单元设计的PLL达到了设计要求.

5 结束语

该电路采用SMIC 0.18 μm CMOS工艺,已实现流片生产,并通过测试.芯片符合设计要求,各项性能良好.

参考文献:

[2] SUNG G N,LIAO S C,HUANG J M,et al.All-digital frequency synthesizer using a flying adder[J].IEEETransactionsonCircuitsandSystemsⅡ:ExpressBriefs,2010,57(8):597.

[3] YEOH H C,JUNG J H,JUNG Y H,et al.A 1.3 GHz 350 mW hybrid direct digital frequency synthesizer in 90 nm CMOS[J].IEEEJournalofSolid-StateCircuits,2010,45(9):1845.

[4] JIANG Xu-dong,LI Wei,YIN Jiang-wei,et al.A single-PLL dual-PPF synthesizer for Mode-1 MB-OFDM UWB communication[J].AnalogIntegratedCircuitsandSignalProcessing,2010,62(3):291.

[5] 鲁纯,韩周安.C频段宽带低杂散频率合成器的设计与实现[J].现代电子技术,2015,38(3):87.

[6] 邵红,纪明霞,丁国臣.一种简约整流电路的设计[J].现代电子技术,2012,35(2):153.

[7] 何国军,李荣宽.电荷泵锁相环2阶无源环路滤波器的设计[J].微电子学,2015,45(2):184.

[8] 刘宝宝,李国刚,杨骁,等.Sigma-Delta小数分频频率综合器系统建模和仿真[J].微电子学与计算机,2012,29(4):80.

[9] SIDIROPOULO S,LIU D,KIM J,et al.Adaptive bandwidth DLLs and PLLs using regulated supply CMOS buffers[C]//IEEE2000SymposiumonVLSICircuitsDigestTechnicalPapers.Honolulu:IEEE,2000:124.

[10] 朱斌.高动态微弱信标信号载波捕获跟踪的设计与实现[J].现代电子技术,2015,38(8):12.