一种高精度多通道实时数据采集系统设计

韩 宾,易志强,江 虹,张秋云,曾 润

(西南科技大学信息工程学院,四川绵阳 621010)

0 引言

传统的精密检测产品多以DSP或RAM作为采集控制核心,存在功能单一、造价昂贵、时钟频率低、实时性差等缺点[1-3]。与DSP和ARM相比,FPGA具有时钟频率高、内部延时小、开发周期短、运算速度快、编程配置灵活、集成度高、功耗低、内部资源丰富等优点,在实时高速数据采集领域有着不可或缺的地位[4-5]。STM32虽然时钟频率低但由于其具有开发灵活、功耗低和性价比高等特点,非常适合作为数据显示和参数配置的处理器。

所以,本文设计了一种FPGA+STM32架构的高精度多通道实时数据采集系统,采样频率为四档可调,最高为150 kHz的采样率。通过合理地运用FPGA内部资源和协调控制各模块间的数据流,达到实时传输的目的[6]。通过STM32配置采集参数和LCD数据实时显示,增强了系统的完备性。

1 系统总体设计

本系统的总体结构如图1所示,该系统由模拟信号采集系统、控制及预警系统、FPGA处理系统、STM32控制系统及其他外围器件组成,其中模拟信号处理系统主要实现模拟信号放大及AD7609数据采集功能;控制及预警系统主要实现外部信号接入和采样过阈值断电与提醒功能;FPGA处理系统主要实现AD7609数据采集控制、数据实时缓存、选通开关及继电器控制、串口收发控制和Flash数据存储控制等功能;STM32控制系统主要实现LCD显示控制和外部键盘数据读取等功能。

1.1 系统工作原理

系统上电后,等待FPGA初始化完成将所有端口电平拉低。首先,FPGA通过串口接收STM32发送的配置参数,给被测设备通电并打开相应被测信号的选通开关,将被测信号放大滤波后转换成数字信号;其次,将转换后的数字信号缓存并组帧,判断采集后的电压是否超过用户设置的阈值电压,若超过阈值电压则断电保护并通过蜂鸣器提示;最后,将组帧的数据通过串口发送到STM32单片机实现LCD实时显示的功能和通过SPI接口发送到FLASH中进行实时存储。

1.2 系统主要指标

本文设计的采集系统的主要技术指标如下:

被测信号支持16路同步数据采样;

图1 系统总体结构图

系统采用频率四档可调,分别为10、50、100、150 kHz;

电压测量误差≤0.1%,电压测量分辨率≤0.01 V;

输入被测模拟电压范围为0.01~5 V。

2 系统硬件设计

系统的硬件电路设计主要为了提高系统的稳定性和增强电路的抗干扰能力,主要介绍以下2个主要电路的硬件设计。

2.1 滤波放大电路设计

为了满足输入数据的稳定性,本文设计了一个4阶的巴特沃斯低通滤波放大电路[7]。使用程控放大器AD8253和AD8250构成的4阶有源巴特沃斯低通滤波电路截止频率约为10 kHz。如图2所示,采用程控放大器设计低通滤波器电路既能有效地滤除无用信号,还能将被测信号进行放大处理,增强了输入信号的稳定性和有效性。

图2 放大滤波电路图

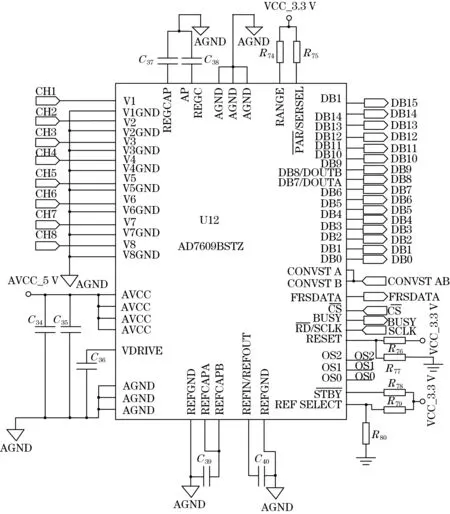

2.2 AD7609采集电路设计

为了满足系统的基本指标,本设计采用2片高精度、低功耗、电荷再次分配逐次逼近型模数转换器AD7609实现16路通道并行数据采集功能,该产品是一款8通道、18位、真差分、同步采样模数数据采集系统。如图3所示,将引脚CONVST A与CONVST B相连施加同一个转换信号能实现一个芯片的8通道同步采样功能[8]。

3 系统软件设计

系统软件设计主要分为FPGA处理和STM32控制两部分,下面依次介绍系统主要功能模块。

3.1 AD7609采集模块

AD7609采样模块的控制功能流程图如图4所示,是控制CS片选信号拉低后,使转换信号CONVST由高电平跳变为低电平且BUSY信号的上升沿到来则转换开始,直至检测BUSY信号的下降沿,数据转换完成。转换期间在SCLK的上升沿并行读取采样数据。经多次实验测试表明采用AD7609的并行数据输出模式能够满足系统所需采样频率,并且数据采样误差≤0.1%,满足系统所需要求。

3.2 采样时钟切换模块

为了实现频率四档可调的功能,采用时钟切换的方式实现频率多档可调,但在切换过程中为了避免产生毛刺和凸点造成数据采集出错,系统通过采用多个寄存器级联的方式防止采样时钟的毛刺产生。时钟切换仿真图如图5所示,通过时钟的两两切换方式,实现了4个时钟的无缝切换,完成系统所需的采样功能可调功能。

图3 AD7609硬件电路图

图4 AD7609采样流程图

图5 时钟无缝切换仿真图

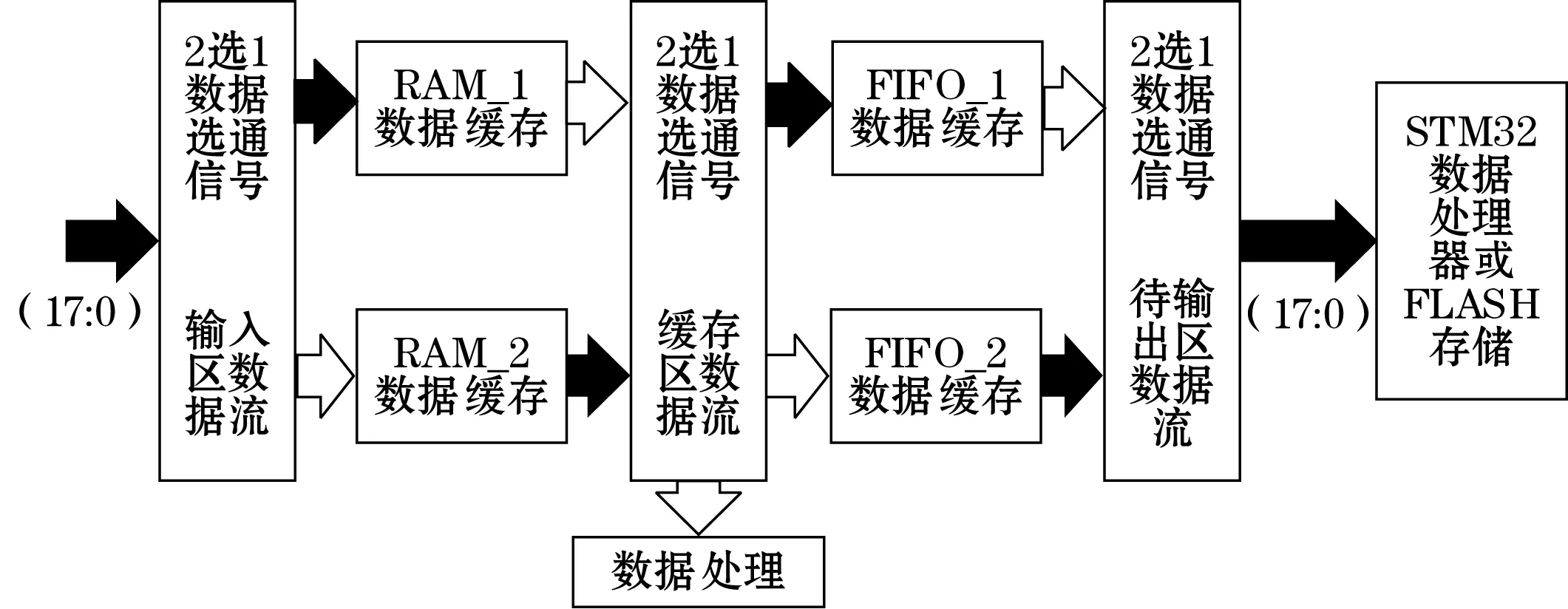

3.3 数据缓存模块

由于系统支持16通道并行数据采集,所以每次采集完成都会产生大量待处理数据,与STM32通信存在传输速率不匹配的问题。与传统的乒乓缓存方式相比,该模块存储效率更高,数据缓存更加可靠[8]。如图6所示,将采集后的数据RAM_1和RAM_2构成的第一级乒乓数据缓存,对数据进行实时组帧和判别处理。然后再通过FIFO_1和FIFO_2构成的第二级乒乓缓存完成STM32的数据实时显示和FLASH实时数据存储功能。图7为乒乓缓存仿真时序图,图中标注为数据缓存状态跳转,通过采用嵌套式乒乓缓存方式能实现实时性数据传输与处理。

图6 嵌套式乒乓缓存图

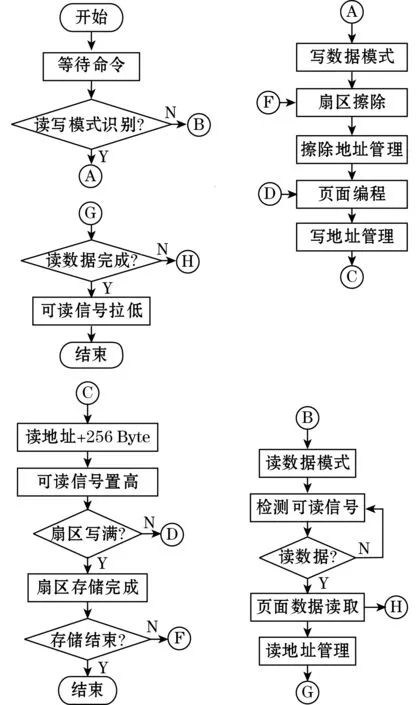

3.4 FLASH存储模块

数据存储模块是将FPGA与FLASH芯片通过SPI接口实现数据读写功能,本系统利用两片存储芯片S25FL32进行轮询读写操作,既克服了NOR Flash的半双工读写缺陷,又能提高数据存储能力。该芯片具有成本低廉、读写可靠和应用广泛等特点,图8为Flash读写流程图。

图7 嵌套式乒乓缓存仿真图

图8 FLASH数据读写流程图

3.5 STM32控制模块

本文采用STM32作辅助控制系统,主要实现参数配置和LCD数据显示两部分功能。

STM32状态跳转图如图9所示,STM32采用串口发送键盘输入的配置参数,和接收回传信号和采集数据发送到LCD屏上进行显示。若采集超过输入阈值则及时发送断电命令,从而更好地避免被测设备损坏。

图9 STM32状态跳转图

4 结束语

本文设计了一种采样频率可调的高精度16通道实时高速采集系统,利用FPGA内部资源,设计了一种嵌套式的乒乓缓存方式。极大地发挥出FPGA并行数据处理能力,实现了实时数据处理和FLASH存储,增强了数据传输和存储的可靠性、有效性和稳定性。经大量实验数据验证,该系统各通道平均采样误差约为0.093%。