基于AD9361的雷达干扰信号模拟器设计

罗勇江,杨腾飞

(西安电子科技大学 电子工程学院,陕西 西安 710071)

在现代战争中,电子对抗已经成为一种重要的作战方式,雷达对抗又是电子对抗的主要组成部分之一,在现代电子对抗中有着不可替代的地位。雷达对抗是侦察、压制敌方电磁频谱的使用并增强我方电磁频谱使用有效性的作战行为,主要包括雷达侦察、雷达干扰、雷达防护等[1]。其中,雷达干扰以破坏或扰乱敌方雷达检测目标为目的,包括无源干扰和有源干扰。有源干扰是干扰机根据雷达的参数和具体目的产生特定类型干扰,具有很强的针对性和灵活性,是一种非常有效的干扰方式,也是现代雷达受到的主要干扰方式。有源干扰按照干扰信号的作用原理分为欺骗式干扰和遮盖式干扰。欺骗性干扰是根据真实目标的特性,加上一定的调制方式模拟形成假目标,将假目标作用于雷达的工作过程中,使得敌方雷达对真、假目标难以区分,造成敌方雷达获取我方目标参数信息的难度增大,从而达到迷惑或扰乱敌方雷达对我方真实目标进行跟踪或检测的目的[2]。根据欺骗式干扰所利用的距离、速度和假目标数目的不同,可以将欺骗式干扰分为距离拖引干扰、速度拖引干扰、距离速度同步拖引干扰、假目标密集复制干扰和音频扫频干扰五类。遮盖性干扰又称压制式干扰,主要实现方式是通过干扰机发射干扰信号来遮盖或淹没目标回波,阻止雷达正常检测和跟踪目标[3]。遮盖性干扰主要通过发射大功率噪声实现,强功率的噪声干扰信号进入雷达接收机,使目标回波信号的信噪比明显下降,从而使雷达对目标难以进行检测和跟踪。典型的遮盖性干扰有射频噪声干扰、噪声调幅干扰、噪声调频干扰、噪声调相干扰、噪声脉冲干扰等。本文利用Xilinx公司的Spartan-6系列SP605评估板和AD9361评估板AD- FMCOMMS3-EBZ进行联合设计,实现低成本的雷达干扰信号模拟器。

1 方案设计

本文选择目前较成熟的零中频软件无线电方案,使用AD9361和FPGA设计雷达干扰信号模拟器。根据功能需求,本模拟器的核心包含两大模块,即射频信号收发模块和基带数据处理模块。射频信号收发模块由AD9361及其外围电路构成,完成基带数字信号到射频模拟信号的数模转换、变频、滤波、增益控制以及最终的发射工作。基带数据处理模块的核心是FPGA,用来实现基带数字干扰信号的产生以及对AD9361芯片的控制。

1.1 AD9361介绍

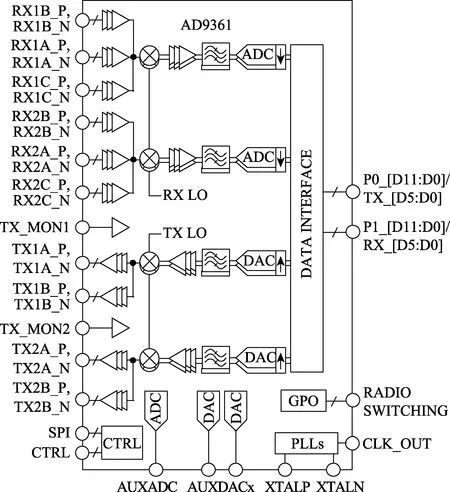

AD9361是ADI公司推出的一款高性能、高集成度的零中频结构的射频收发芯片,工作频段为70 MHz~6 GHz,支持通道带宽为 200 kHz~56 MHz。该器件内部集成了大量模块,包括射频放大器、发射和接收通道的频率合成器、混频器、模拟滤波器、数据转换器等,可以完成信号在射频前端与基带数据流之间的转换工作[4]。并行数据端口 P0和 P1作为AD9361与各种基带处理器(BBP)之间的数据传输接口。图1为AD9361的功能框图。

图1 AD9361功能框图

AD9361的信号接收和发送链路分别有两个相同的、独立控制的通道。每个发送通道包含两个射频输出端口,接收通道则有三个射频输入端口。在信号接收通道中,射频信号从输入端口进入芯片,经过正交混频器被分成 I、Q两路基带模拟信号,每一条接收通路上集成的模数转换器能对 I、Q两路信号同时进行采样,采样后的数字信号通过内部可配置的抽取滤波器和 128阶有限脉冲响应(FIR)滤波器处理后生成 12位基带数字信号,这些数字信号通过数据接口P0发送给BBP[4-6]。发送通道与接收通道类似。AD9361通过P1接口从BBP接收基带数据,然后数据通过一个不带插值选项的完全可编程128抽头的FIR滤波器和一系列插值滤波器,进行滤波和数据速率插值处理。随后由数模转换器将基带数字信号转换为基带模拟信号。I/Q两路模拟信号经过滤波后在混频器中被组合起来形成已调制信号。已调制信号再经过处理后输出到天线发射。AD9361的收发通道可以同时工作,支持时分双工(TDD)和频分双工(FDD)两种工作模式。

1.2 系统框图及硬件平台

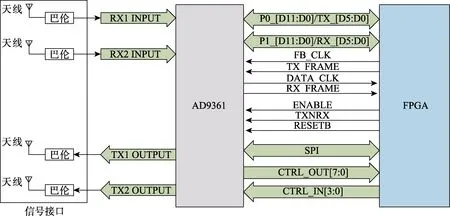

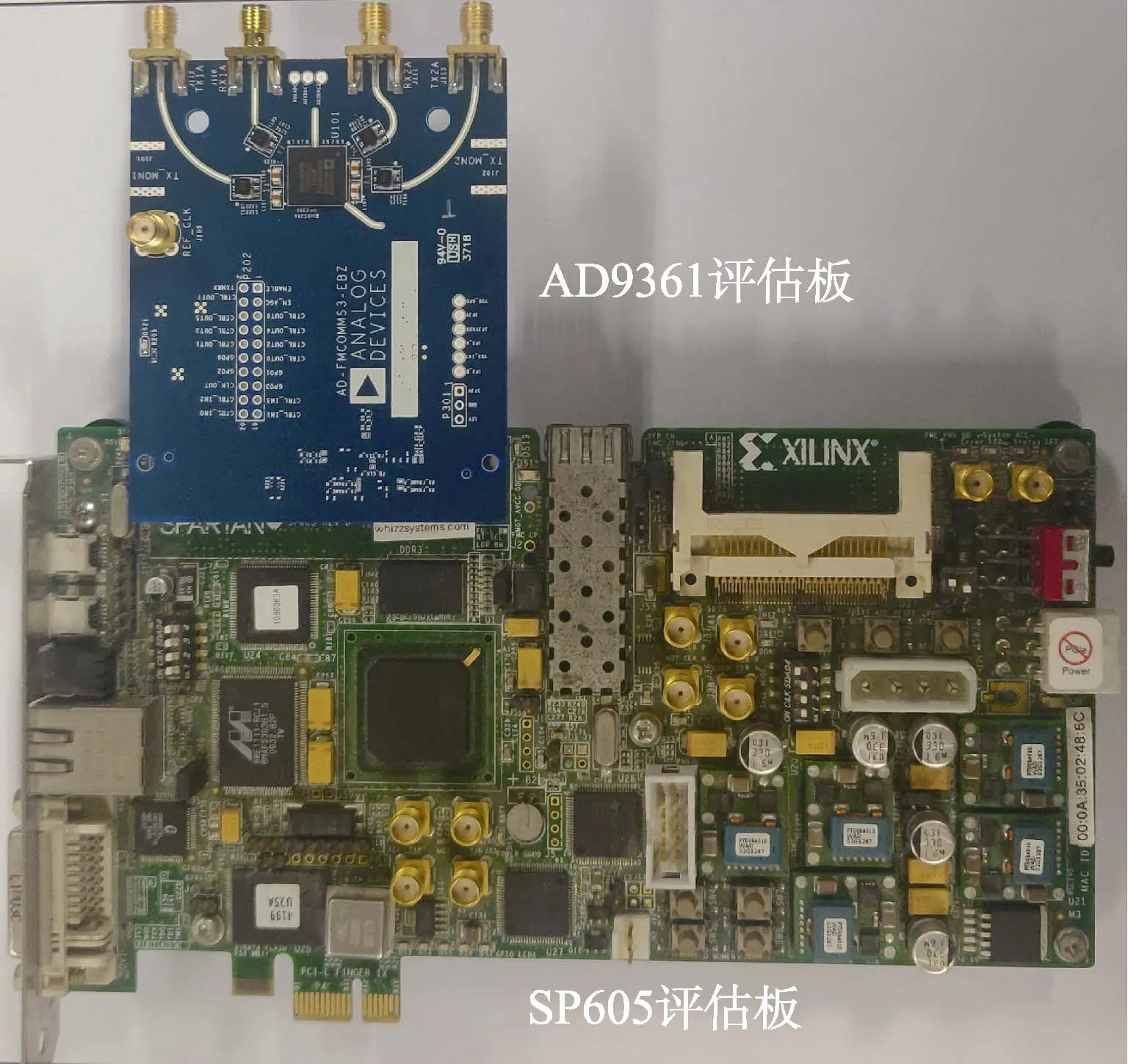

雷达干扰信号模拟器由AD9361和FPGA相互配合实现,原理如图2所示。信号接口模块主要由天线

图2 基于AD9361的雷达干扰信号模拟器原理图

和巴伦组成,用来实现射频信号的接收与发送、单端信号与差分信号的转换。射频模拟信号与基带数字信号之间的转换由 AD9361完成。AD9361的数据输入输出引脚和控制引脚通过FPGA夹层卡(FMC)接口与FPGA的可配置IO引脚相连,实现两者之间的数据传输以及FPGA对AD9361的控制。硬件平台实物连接如图3所示。

图3 硬件平台实物连接图

1.3 系统中的主要接口

1.3.1 串行外设接口

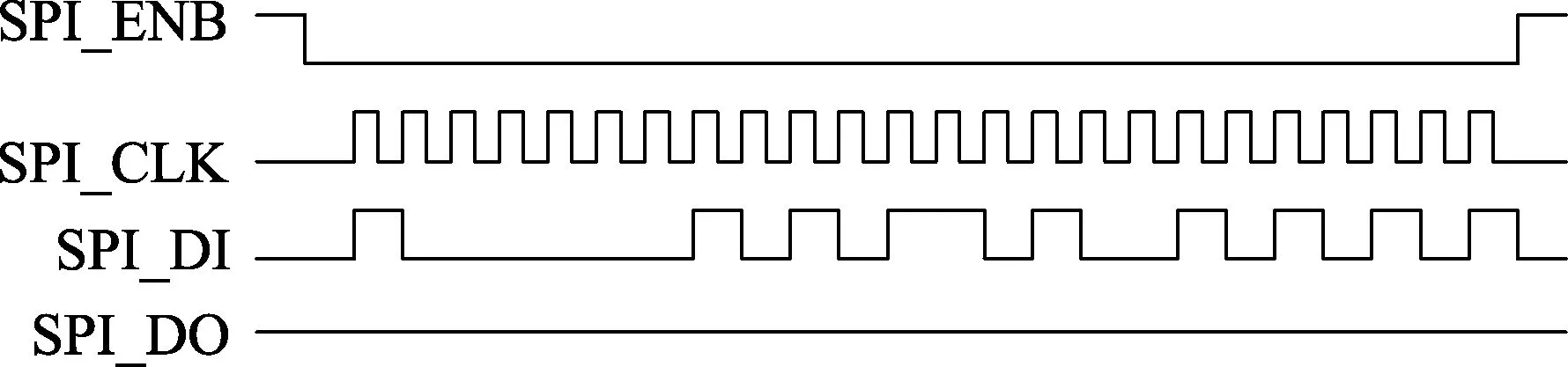

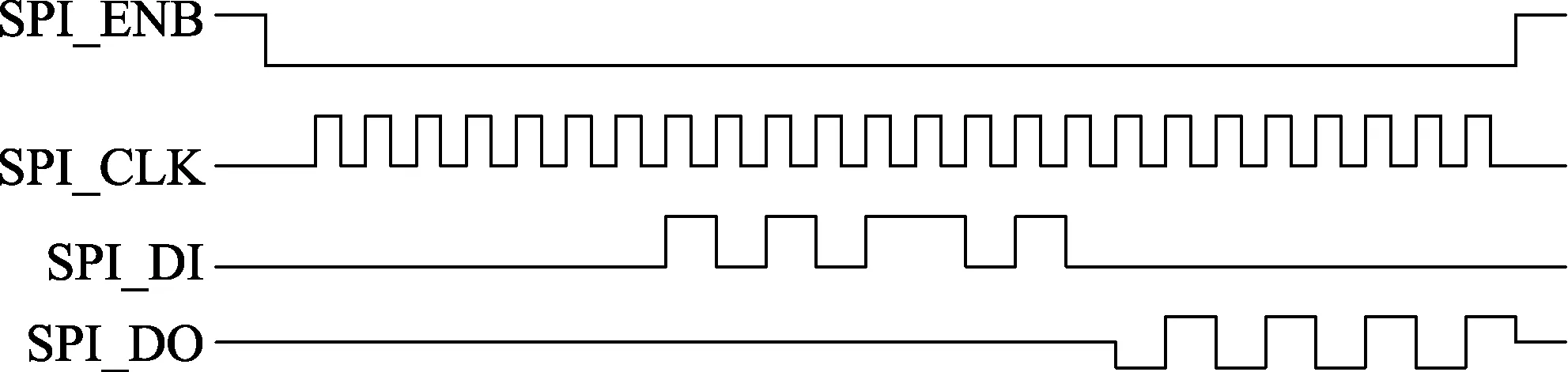

BBP对AD9361芯片的控制通常通过串行外设接口(SPI)实现。AD9361内部有大量的8位寄存器,BBP可以通过SPI总线对这些寄存器进行读或者写操作,来判断或者设置AD9361当前工作状态。AD9361的SPI端口可以配置成3线或者4线标准SPI接口[7]。

SPI的写命令遵循24位格式:前6位设置总线方向和需要传输的字节数,接下来的10位是需要写入数据的寄存器的地址,最后8位是将被传输至指定寄存器地址的数据。读命令遵循相似的格式,区别在于最后8位数据从AD9361中读取,如果是4线模式则在SPI_DO引脚传输这8位数据,如果是3线模式则在SPI_DI引脚传输这8位数据。

图4和5分别详细展示了单寄存器写操作和读操作的4线SPI总线波形。在图4中,0x55被写入寄存器0x15A,在图5中,读取寄存器0x15A,并且AD9361返回0x55。如果使用3线SPI总线执行相同操作,则图4中没有SPI_DO线,图5中的SPI_DI和SPI_DO线上数据合并到SPI_DI线上。

图4 SPI写数据时序

图5 SPI读数据时序

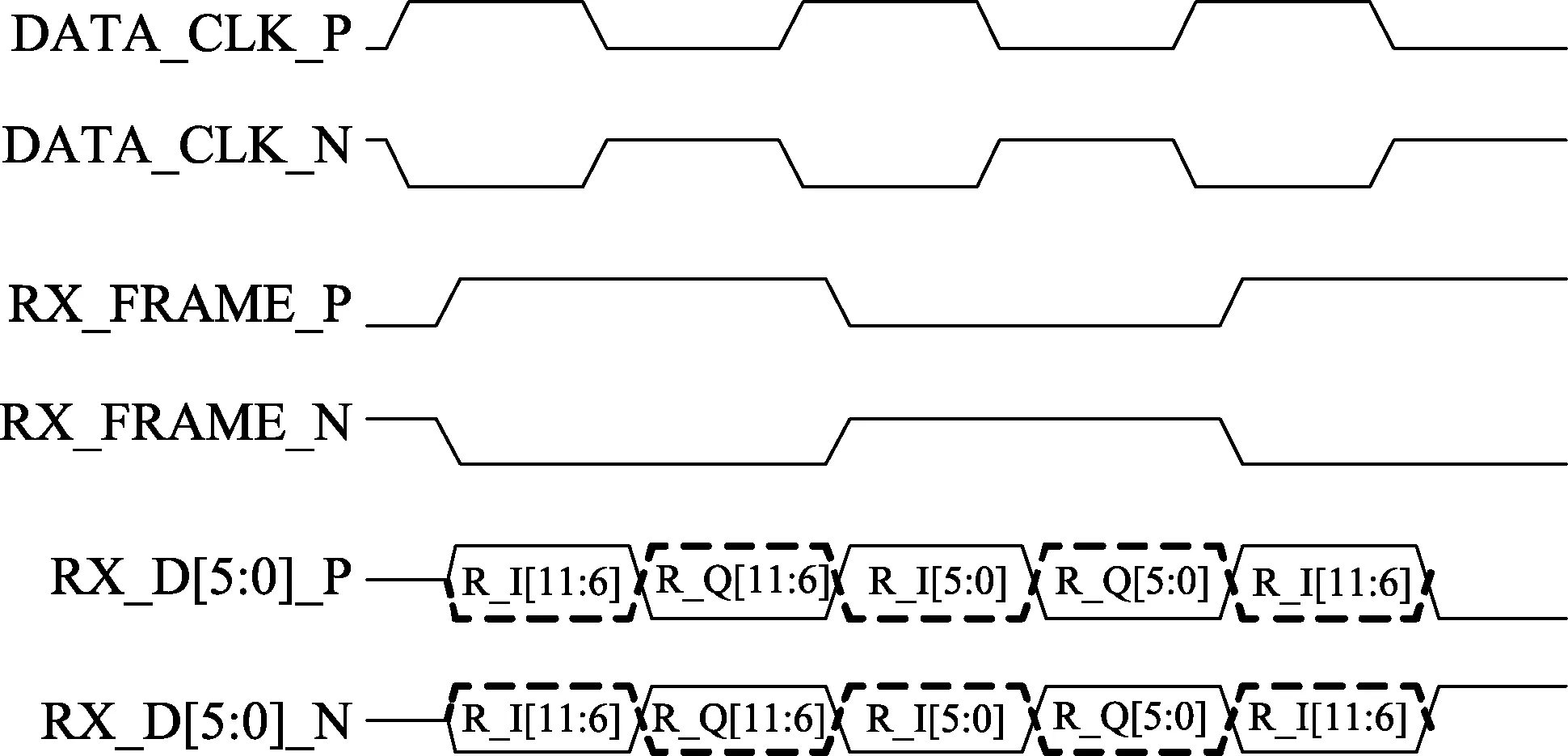

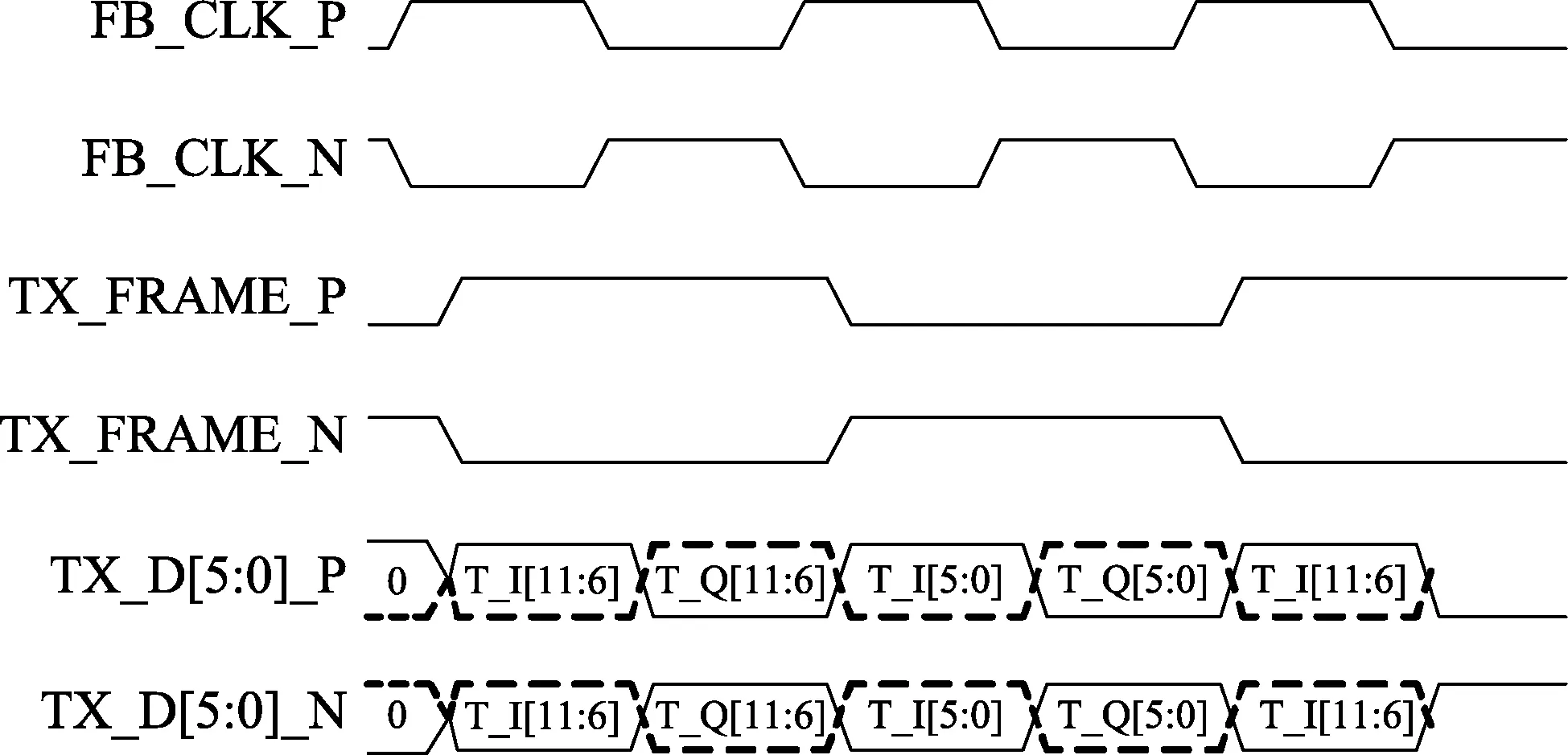

1.3.2 并行数据端口

并行数据接口用于在AD9361和BBP之间传输数据,该接口的工作模式分为两种:标准CMOS兼容模式和低压差分信号(LVDS)兼容模式[8]。相比CMOS,LVDS具有低电压、低功耗、抗干扰能力强和有利于高速传输等特点,在需要更稳定性能和更高数据速率的宽带高速系统设计中,常常采用LVDS兼容模式。当AD9361使用双总线全双工LVDS兼容模式时,主要的数据传输端口为 Tx_D[5:0]和 Rx_D[5:0]。Tx_D[5:0]和Rx_D [5:0]均是由六个差分对组成的LVDS数据总线,数据以成对的数据字在总线上传输。要发射的数据在 Tx_D[5:0]数据总线上从 BBP传输到AD9361;接收到的数据在 Rx_D[5:0]数据总线上从AD9361传输到BBP。这两组总线可以同时工作,从而保证BBP和AD9361之间的数据发送和接收为全双工。

两组总线上的数据传输格式会根据接收通道数和发送通道数的不同而改变。对于具有1个接收通道和1个发送通道(1R1T)的系统,I和Q两路的数据以4路交错方式传送:IMSB, QMSB, ILSB, QLSB,…。图6和7中的时序图说明了 1R1T系统在 DDR、FDD、LVDS模式下总线信号之间的关系。

图6 接收数据路径时序图

图7 发送数据路径时序图

2 雷达干扰信号的FPGA实现

对雷达的干扰方式有多种,本文实现较为常用的干扰信号。干扰信号发射的主要流程为:对于压制干扰,先使用FPGA产生基带干扰数字信号,然后将该数字信号发送给 AD9361,再由 AD9361完成基带数字信号到射频模拟信号的转换,并将其通过天线发射出去;对于欺骗干扰,先通过天线接收雷达信号,在FPGA中对收到的雷达信号进行处理,再由 AD9361及外部天线完成发射。

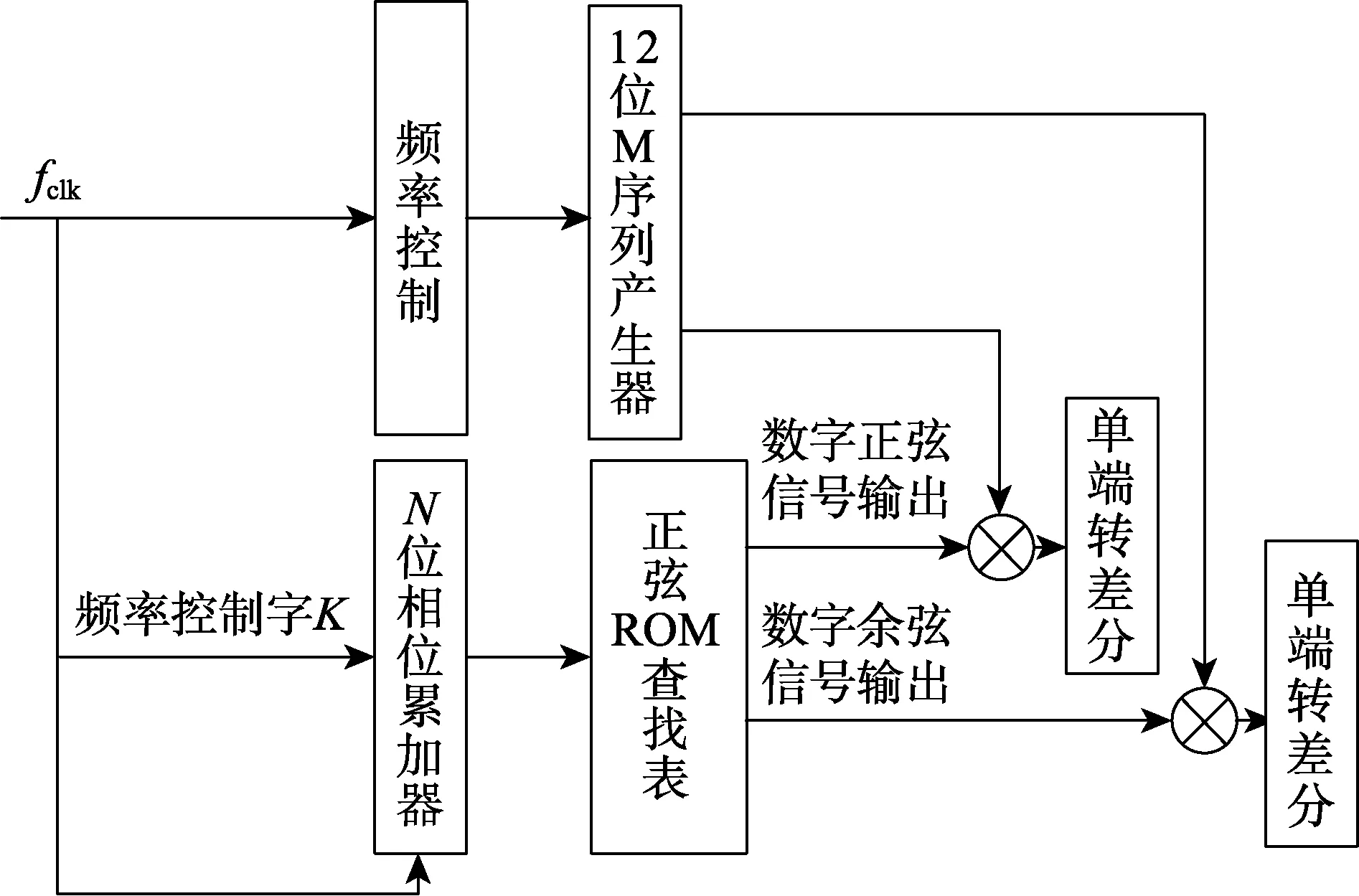

2.1 噪声调幅干扰信号产生原理

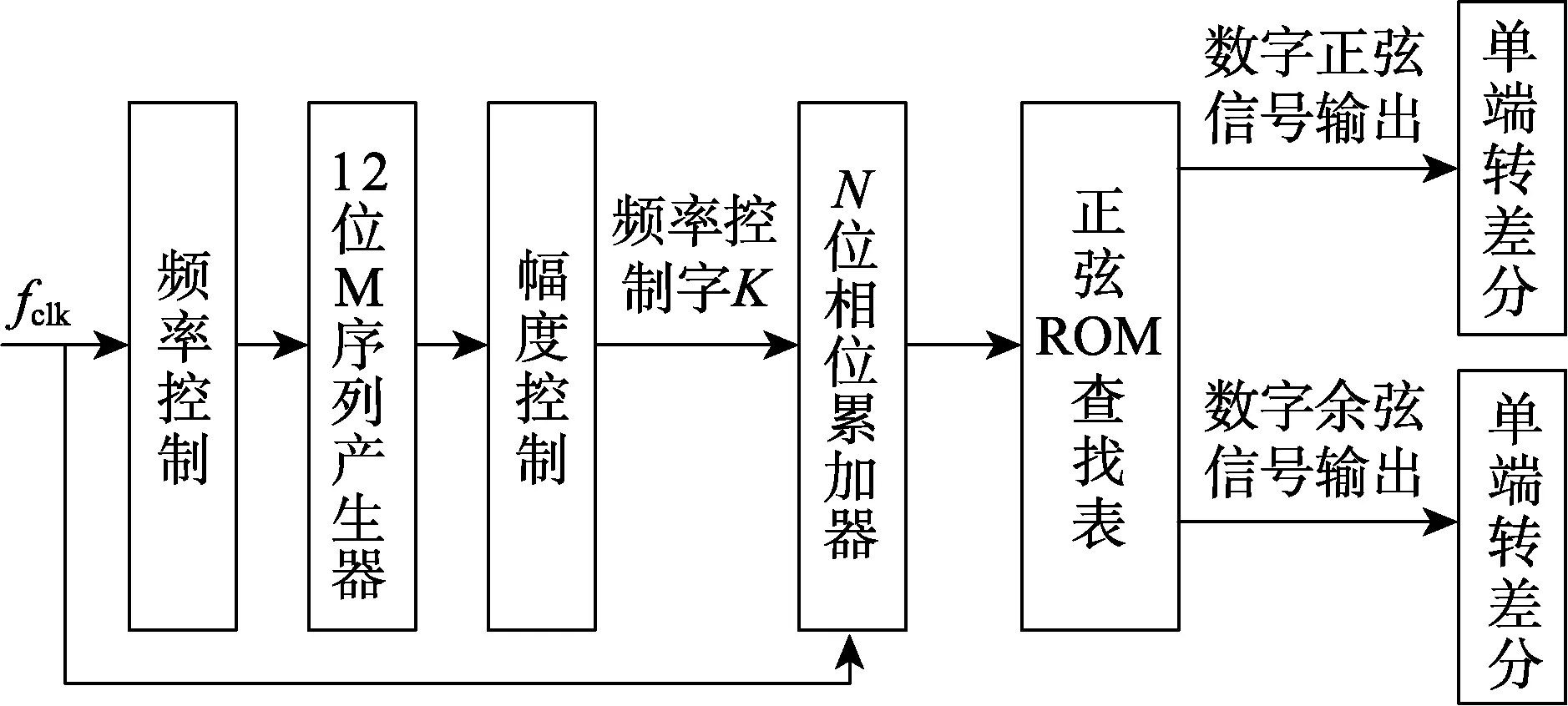

基带噪声调幅干扰数字信号的产生结合了 M 序列产生器[9]和DDS技术[10],具体的实现框图如图8所示。12位 M序列产生器的输出是性质类似于白噪声的伪随机序列,将其分别与数字正弦信号和数字余弦信号相乘,对应得到噪声调幅正弦信号和噪声调幅余弦信号。

图8 基带噪声调幅干扰数字信号的产生流程框图

2.2 噪声调频干扰信号产生原理

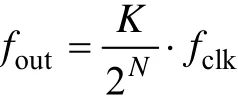

基带噪声调频干扰数字信号的产生主要参考DDS技术。FPGA实现基带噪声调频干扰数字信号的流程如图9所示。

图9 基带噪声调频干扰数字信号的产生流程框图

正弦信号和余弦信号的频率的计算公式为

其中,K是频率控制字,N是相位累加器的数据位宽,fclk是基准时钟频率。12位M序列产生器的输出是性质类似于白噪声的伪随机序列,这些序列值被用作频率控制字K。由于N和fclk为固定值,当K呈噪声变化时,输出信号的频率fout也呈噪声变化,即为基带噪声调频信号[11]。

2.3 噪声调相干扰信号产生原理

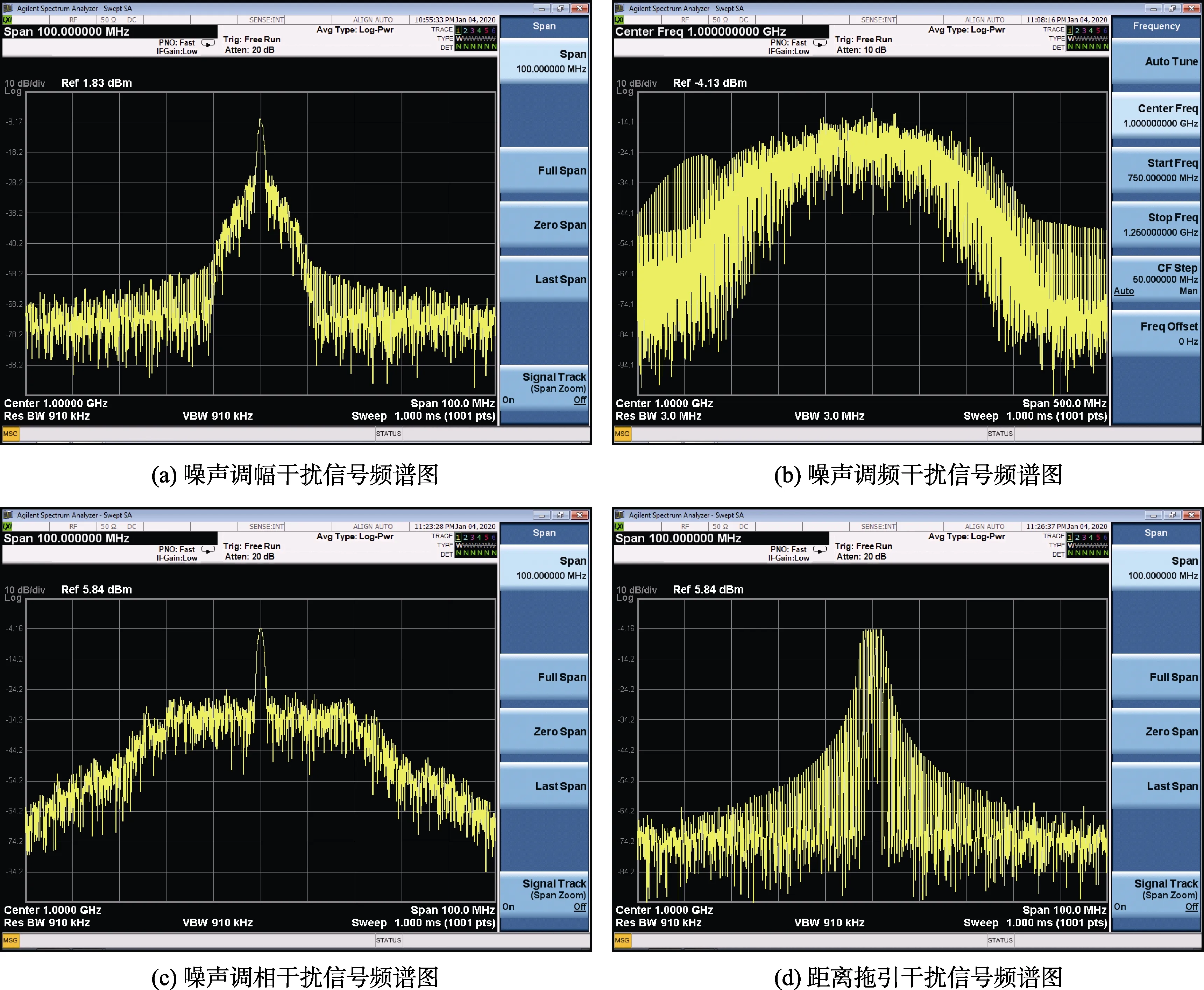

噪声调相干扰信号的具体实现框图如图10所示。将12位M序列产生器的输出与N位相位累加器的输出相加,两者之和用作正弦 ROM查找表的输入,从而实现干扰信号的调相。

图10 基带噪声调相干扰数字信号的产生流程框图

2.4 距离拖引干扰信号产生原理

距离拖引干扰主要是通过对收到的雷达照射信号进行延时实现。具体的,雷达信号通过天线进入干扰机,由AD9361处理并传输给FPGA。FPGA对该信号进行存储、延迟,再通过AD9361和天线进行发射作为假目标信号回波。在该过程中,可以通过控制延迟时间移动假目标的位置。信号的延迟在FPGA中可以用FIFO结构实现[12]。FIFO的深度表示信号的延迟,假设FIFO的深度为D,系统时钟频率为fclk,则延时为D/fclk,对应的距离为c·D/(2fclk),c是电磁波在真空中的传播速度。距离拖引干扰信号的产生流程如图11所示。

图11 距离拖引干扰信号的产生流程框图

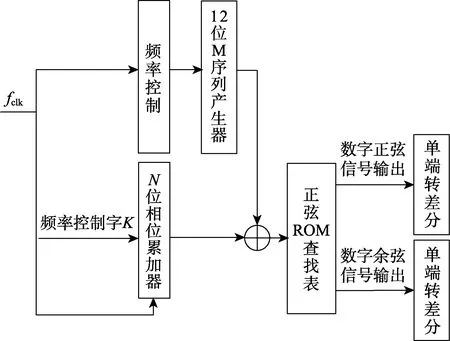

3 实验测试

本文设计的模拟器可以根据实际需求产生多种雷达干扰信号,信号中心频率最高可达6 GHz,信号带宽最大可达 56 MHz。本次实验选择四种典型干扰信号进行实现,分别为:噪声调幅干扰信号,中心频率1 GHz,带宽10 MHz;噪声调频干扰信号,中心频率1 GHz,带宽50 MHz;噪声调相干扰信号,中心频率1 GHz,带宽50 MHz;距离拖引干扰信号,接收的雷达信号为线性调频信号,中心频率1 GHz,带宽5 MHz。

将 AD9361评估板插接到 SP605评估板,并将AD9361评估板连接至频谱分析仪,观察四种信号的频谱,实验结果如图12所示。

图12 四种干扰信号的频谱图

4 结语

本文基于射频收发芯片AD9361设计了一种雷达干扰信号模拟器,利用FPGA配合AD9361通过软件无线电技术实现各种雷达干扰信号的模拟产生,给出了模拟器设计思路和程序设计流程。测试结果表明该模拟器的雷达干扰信号具有较好的性能。该模拟器可作为雷达、雷达对抗及相关专业学生的实验教学辅助设备,有助于学生掌握雷达、雷达干扰系统和信号的相关知识。