美国国防部可信微电子战略和举措演进研究

张 倩,刘馨阳,聂国健,周军连

(工业和信息化部电子第五研究所,广东广州 510610)

为保障武器装备用微电子器件的安全,美国国防部自2003 年起逐步建立起“可信供应”能力。随着微电子器件产品供应链的持续全球化和先进制造能力不断向亚洲聚集,美国国防部要求加大对商用技术和产品的使用力度,并于2017 年提出“技术实现可信”的新安全框架[1]。2020 年5 月,美国国防部国防研究和现代化工程主任马克·路易斯表示,国防部将采取“零信任”方式购买微电子器件产品,即假设所购产品均不安全,必须通过验证后才可使用,并表示已经研制出达到该目标的技术[2]。通过分析新安全框架及其所匹配项目的研究成果,可以证实美国国防部已打下了良好的可信技术保障能力。

1 美国国防部一直担心微电子器件的安全和持续供应

美国武器装备用逻辑电路只有约10% 来自国防部的定制化制造,其他则依赖商用现货(Commercial-off-the-shelf,COTS)[3]。在供应链全球化的背景下,微电子器件在装入武器装备前可能会被倒手十余次[4],而且亚洲掌握着最先进的微电子制造和封测能力,美国非常担心武器装备用微电子器件在制造和流转过程中的安全,具体体现在以下四个方面:

敏感信息丢失。通过潜入设计和制造环节或实施逆向工程等手段,可盗取微电子器件产品中的敏感或关键信息、知识产权(Intellectual Property,IP)等,还可了解器件结构和功能,以及发现漏洞,为后续功能复制或发起攻击做好准备。

植入恶意功能。通过修改微电子器件规格、设计和掩膜版等手段,可植入缺陷或硬件木马,使系统性能降低甚至失效,或获取系统访问和控制权,进而实施攻击。2011 年7 月,美国国土安全部在给国会的报告中指出,已发现销往美国的电子元器件被国外组织预置了间谍软件、恶意及损害安全的部分[5]。

混入伪冒产品。将质量不合格和伪冒的微电子器件再次引入国防供应链,包括克隆伪造、废弃再回收、打磨翻新、为改变质量等级而重新打标、未经许可的超量生产等。在美国国防部2010 年前后开展的系列调查中显示[6-7],伪冒电子元器件已影响美国国防电子供应链的40%,涉及海陆空八大武器装备。根据国际电子经销商协会(Electronic Resellers Association International,ERAI)2020 年 统 计 数 据,2018 年伪冒电子元器件预计给美国半导体制造商造成了约75 亿美元的损失;其中69.9%为集成电路[8]。

供应链条断裂。原因包括技术升级或商业压力迫使供应商停止生产、供应商倒闭或被收购、地缘政治冲突或自然灾害导致生产和交付中断等,严重威胁关键武器系统的维护和升级。

2 美国国防部从2003 年开始建立“可信供应”能力

2003 年,美国国防部制定了《国防可信集成电路战略》,要求建立能为国防关键武器、情报系统提供可靠微电子器件的国防工业基础。2004 年初,国防部发布《专用集成电路(Application Specific Integrated Circuit,ASIC)可信供应商临时指南》,将“可信”定义为“通过评估国防安全用重要器件设计、生产、制造、分销等环节中人员和流程的完整一致性,确定其具备保障国家安全的能力”;指出可信是国防系统的最低要求,明确必须由可信代工厂制造的器件类型[9]。

2.1 国防部希望为微电子器件提供“端到端”的全面安全保障

2004 年,美国国防部与国家安全局开展“可信代工厂”项目,并与美国IBM 公司签署了一份为期10 年、总金额6 亿美元的可信代工线共建合约,以满足关键军事和情报核心系统所需硅ASIC 的制造[10]。2007年“可信代工厂”项目增加“可信供应商”,采取认证方式,将微电子器件可信服务范围从制造扩展至包括设计、掩模、封装、测试等在内的全产业链,并覆盖砷化镓、氮化硅等更多材料,更好保障ASIC设计和制造过程的完整性和保密性,以及满足军方多样化发展需求。此后出台的5 200.44、5 200.39 等多个国防法令中也持续强调可信的重要性[3]。

美国国防部和国家安全局各出资50%支持“可信代工厂”项目[11]。国防部在2004—2019 年间累计投入7.31 亿美元,历年投资情况见表1。由于数据不允许公开,国家安全局的投资情况不得而知。资金主要用于IBM/格芯(Global Foundry,GF)公司可信代工厂的改造和升级、可信供应商的认证、停产断档ASIC IP 和停产设备的购买、产品原型试样和小批量生产方法研究等。国防部未来每年将继续投入8 000~9 000 万美元。截止2020 年6 月26日,可信供应商数量79 家,包括21 条制造工艺线,覆盖主要类别微电子器件(含抗辐射器件)及部分光电器件,工艺及所对应特征尺寸如表2 所示[12]。

表1 国防部对“可信代工厂”项目历年投资情况单位:万美元

表2 美国现有可信制造能力

表2 (续)

2.2 现有模式存在缺陷且日益无法满足最先进制造能力需求

2014 年8 月,IBM 公司宣布出售微电子制造能力,美国国防部旋即针对无法获取先进微电子器件可能带来的风险、有无合适替代方案等内容与产业界和国防部官员进行了讨论[13],内容因敏感未公开,结论是,短期内没有隶属于美国且掌握先进制造技术的美国境内/外的代工厂可进行替代,长期启动研究和验证具备替代能力的制造技术及新建所有权归政府的代工线等也有相应的风险和限制。

2015 年7 月,格芯公司完成对IBM 公司微电子制造能力的收购。尽管格芯公司位于美国但由阿联酋100%持有,还是引发了美国政府的担心。同年10 月,美国政府问责署发布报告表示,尽管美国已在十多年前采取行动,但在保障可信先进微电子器件制造能力方面仍存在重大缺陷:一是防范手段单一,只有可信代工厂项目这一个手段;二是供应源单一,IBM 公司一直是先进微电子制造能力的唯一来源,随着IBM 公司出售微电子制造业务,可信供应能力进一步恶化,但国防部无明确有效的应对措施[13]。从2015 年10 月开始的可信供应商名单中,原由IBM 公司提供的先进制造能力仍仅由格芯公司提供,且最先进制造能力仅为65 纳米CMOS 工艺和32 纳米SOI 工艺,远落后于商用最先进技术数代。

3 美国国防部提出“技术实现可信”新安全框架

3.1 国防部要求加大对商用技术的使用

商用和军用技术发展呈现“冰火两重天”。美国国防部认为,特征尺寸的不断减小带来微电子器件研发和制造成本快速攀升,远超国防部的承担能力,如10 纳米ASIC 的设计成本近4.2 亿美元,是130 纳米ASIC 设计费用的17~20 倍[14],只有需求量巨大的商用产品才能平摊高昂设计成本,也正因此牵引元器件企业投入到获利更高和更快的商用市场,忽视甚至拒绝服务费时、费力、收益小的军用市场,导致商用技术发展加速迭代,军用技术发展举步维艰。

先进商用技术能带来武器装备性能的巨大提升。美国国防部认为,微电子先进商用制造技术、商用IP、安全技术等可大幅提升武器装备性能,以及增加逆向工程、伪造和克隆的难度,有助于保持超越竞争对手的优势。美国国防高级研究计划局(Defense Advanced Research Projects Agency,DARPA)近年已研制出多款采用先进技术的微电子器件,证实先进技术可带来性能的大幅提升,如以手机电池电量即可支撑180 个小时射频信号识别和以64G/s 速度捕获和分析超大量射频数据的数据处理芯片,具备10倍高动态范围的任意波形发生器,可获取全战域感知能力的单个可重构芯片,可支持实时机器学习的小型平台,可高速智能捕获、识别和分析数据的单个摄像头等[15]。国防部也证实,对采用90 纳米鳍形晶体管(FinFET)结构的ASIC 进行逆向工程需要1 年时间[16]。

可信供应模式不能满足需求。美国国防部认为,“可信供应”运行机制相对封闭,国防部可获得的商业IP 和设计资源非常有限,不能立刻享用技术发展所带来的性能优势。2017 年2 月,美国国防科学委员会发布报告指出,国防部要与最先进商业微电子制造能力合作,而不是投资一个国防部所拥有的先进制造厂,这样才具备资金可行性,以及满足未来自动化和智能化发展新需求;同时应加强防篡改技术的研发及采取拆分制造和跟踪流程等策略,多举措保证安全[17]。

为此,美国国防部提出建立新安全框架,要求既能灵活使用商业技术和制造能力,又能保证高度安全,保障未来十年最有可能推动军事能力发展的电子元器件的来源、安全和可靠。

3.2 DARPA提出“技术实现可信”框架和系列保障方法

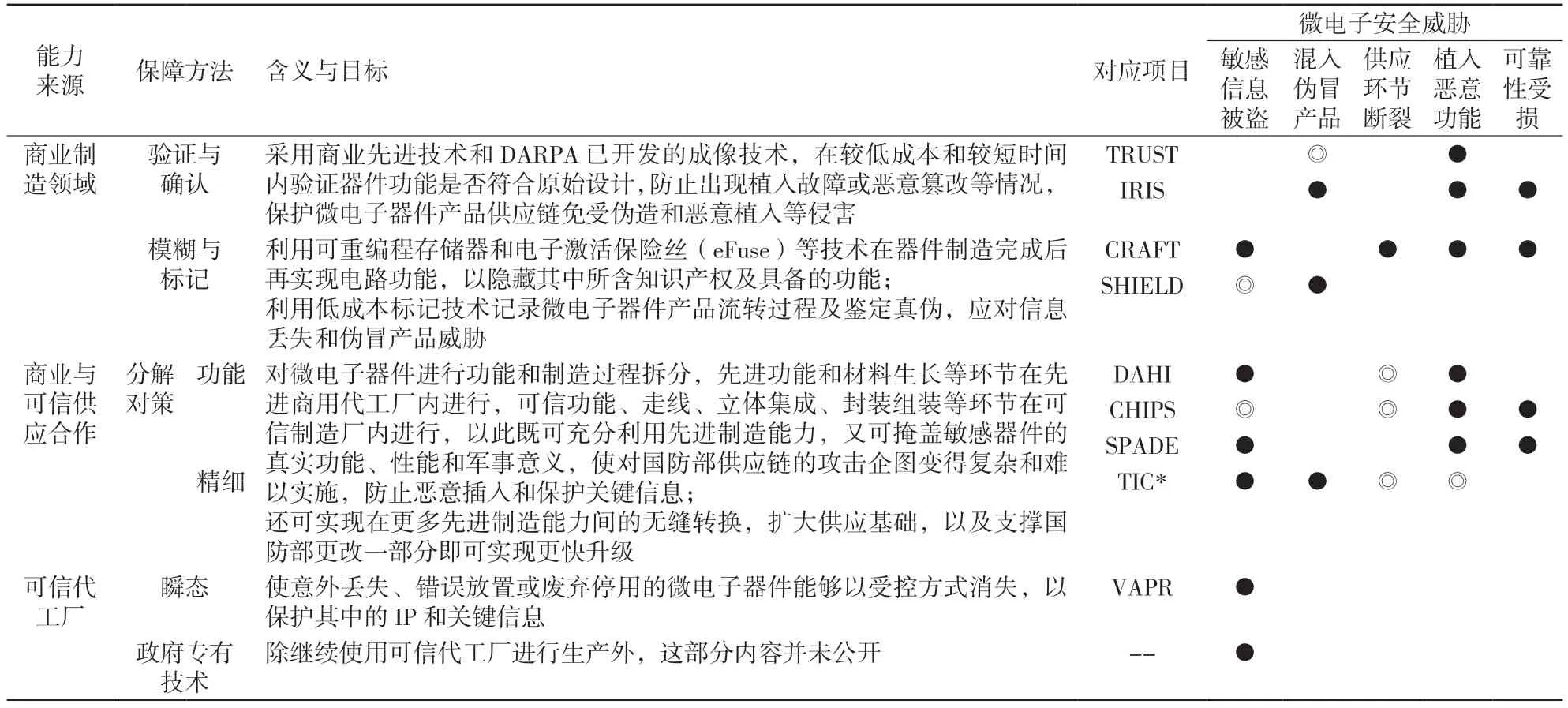

基于“可信供应”模式和已开展项目,DARPA提出“技术实现可信”新安全框架和多个保障方法,包括验证和确认、模糊和标记、功能分解和精细分解、瞬态、政府专有解决方案等,可达到掩盖器件功能、验证器件来源和功能、保护敏感信息和IP、扩大国防供应基础等目的[1]。各保障方法含义、对应项目和可应对威胁如表3 所示。

表3 各保障方法对应项目及可应对威胁

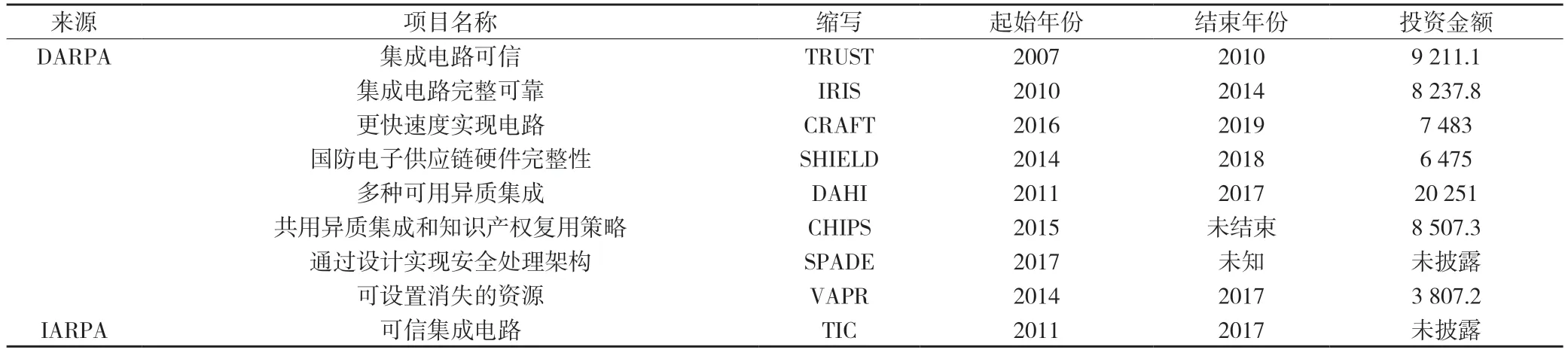

4 美国国防部匹配九个项目以建设体系化可信能力

新安全框架包含9 个项目,但并非新设项目,是对DARPA 和IARPA 对此前和正在开展项目的一次统筹。部分项目已经完成并取得显著成就,部分项目仍在进行中,项目起止时间和已投资金额如表4 所示。以下对各个项目的研究内容和主要成果分别进行论述。

表4 “技术实现可信”框架下9 个项目的起止时间和投资金额 单位:万美元

4.1 TRUST项目

DARPA 认为美国并未具备足够能力来证明其武器装备用微电子器件中不包含恶意的电路,为此于2007 年启动TRUST 项目。

研究内容。项目希望彻底摒弃传统方法,开发出可根据测试概率与虚警概率得出可信度量的公式,验证在非可信条件下设计和制造的军用集成电路的可信程度,以及减少验证所需的成本和时间,为识别遭恶意攻击的集成电路提供了一个条明确防范途径,测试对象包括商用ASIC 和现场可编程门阵列(Field Programmable Gate Arrays,FPGA)[18]。

主要成果。项目历时四年,总投资9 211.1 万美元,历年投资情况如表5 所示[19-24]。项目研制出了系列技术,可通过对已制造出的ASIC 进行自动聚焦离子束(Focused Ion beam,FIB)分层、扫描电子显微镜(Scanning Electron Microscope,SEM)成像和图像处理,重建对应版图(GDS Ⅱ),可判断制造过程是否符合原始设计;可自动检查从寄存器传输列表(Register-Transfer Level,RTL)到网表再到GDSⅡ的器件设计全流程;可将ASIC 和FPGA 中第三方IP 中的未知逻辑单元库与IP 功能特性进行关联,验证IP 的完整性;开发出能准确地代表RTL 所描述的原始设计的比特流,及可验证FPGA 的物理不可克隆(Physically Unclonable Functions,PUF)技术;可在240 小时内完成对采用45 纳米工艺、包含100 万个晶体管的ASIC、FPGA 的验证[19-24]。

表5 TRUST 项目历年投资情况 单位:万美元

成果应用。项目研发出FPGA 和ASIC 功能逻辑验证工具和IP 验证工具,已分别被美国国防微电 子 处(Defense Microelectronics Activity,DMEA)和空军研究实验室(Air Force Research Laboratory,AFRL)所采用[25]。

4.2 IRIS项目

TURST 项目结束后,DARPA 于2011 年启动了IRIS 项目,进一步推进深亚微米CMOS 电路成像和器件识别技术的研究。

研究内容。IRIS 项目最初名为“ 探索”(DISCOVER),2012 年更名为IRIS。项目将研究对象拓展为“电路设计规则和功能未知”的ASIC,重点研究可在仅知道有限性能指标的前提下非破坏性地识别出数字、模拟和混合信号集成电路功能的技术,可清楚确定该集成电路是否被恶意修改;还将加强对负偏压温度不稳定(Negative Bias Temperature Instability,NBTI)、热载流子注入(Hot Carrier Injection,HCI)、时间依赖性介电击穿(Time Dependent Dielectric Breakdown,TDDB)和 电 迁 移(Electro Migration,EM)等ASIC 老化机制的研究,创新器件建模方法及分析和测试技术,实现可从物理层面判断芯片寿命,大幅减少可靠性检测所需样品数量[26]。

主要成果。项目历时五年,总投资8 237.8 万美元,历年投资情况如表6 所示[22-24,27-30]。在功能检查方面:开发出可进行无损成像、电路提取和功能推导的方法和工具,可在晶体管级看到有关芯片制造和电路功能的信息;可对基础元器件(晶体管、电容、电阻)、存储器和互连进行非破坏性成像识别和提取网表;可对45 纳米CMOS 数字和混合信号IC、ASIC 和FPGA 中第三方IP 进行功能推导;将逆向工程的时间从数月减少至数周。在可靠性评估方面:结合成像、电路提取和可靠性建模分析,可识别测试IC 样品中的异常及确定其对可靠性的影响,显著提升可靠性分析的准确性、功能性和有效性;可对90 纳米CMOS 数字IC 和130 纳米CMOS 混合信号IC 做基于少量样品的可靠性推导;开发出可模拟电路性能并解决器件老化问题的模型,能够检测出为了促进早期失效而承受应力的IC 或在丢弃后重新引入供应链的伪冒产品[22-24,27-30]。

表6 IRIS 项目历年投资情况 单位:万美元

成果应用。项目承研方雷神(Raytheon)公司在某军事硬件上验证功能推导准确性为99.4%。项目还研发出可用于防范伪冒电子元器件的扫描光学显微镜(ASOM)技术。美国海军水面作战中心采用了该技术,并进一步建立了“虚拟实验室”,可对器件全生命周期的各种缺陷进行检测,保障嵌入国家关键军事武器和网络空间系统的器件的功能、完整性和可靠性[25]。

4.3 CRAFT项目

2016 年,DARPA 启动CRAFT 项目,提出研发“面向对象设计”(Object-Oriented Design,OOD)的软件工具,希望能显著减少先进节点设计和制造的过高成本。

研究内容。一是通过自动生成器实现大部分设计任务的自动化,实现从高级OOD 语言到原理图的直接转化,减少现有流程所需的大量验证工作,如图1 所示[16],将军事所需高性能ASIC 的设计和制造周期缩短为之前的1/5,如将28 纳米ASIC 的研制由2.5 年减少为0.6 年;二是创建知识贮藏库,归档国防部关键军用ASIC 设计中涉及的文档和IP,使IP 库复用率达50%以上,大幅降低设计工作量;三是提升IC 设计在不同代工线、不同工艺节点上迁移的灵活性,将迁移的工作量减少80%,扩大先进制造能力供应来源;四是研究电子激活保险丝(eFuse)等可掩盖敏感信息的技术,当IC 制造完成后再通过保险丝来改变内部连接实现电路功能[31]。

图1 面向对象设计与传统设计流程对比

主要成果。项目历时四年,总投资为7 483 万美元,历年投资情况如表7 所示[30,32-36]。项目已完成OOD 方法的设计流程,建立了一个包含完成OOD流程所需的知识产权、方法和工具的知识库;形成向所有国防承包商开放的(multiply project wafers,MPW)服务能力,具体指标为中国台湾台积电公司的300 毫米晶圆、16 纳米FinFET 工艺,芯片面积不超过2.5×2.5 平方毫米,单次单个用户成本为5万美元,并完成了实验性设计和3 次MPW 流片。模拟集成电路和数字集成电路的设计时间分别压缩为原来1/11 和1/8;将数字和混合信号ASIC 迁移至格芯16nm 工艺的所需工作量分别减少为原来的1/5.3和1/4.3[37]。研制的原型芯片包括多应用电子战/雷达用芯片、多应用可重置数字信号处理器、计算机视觉加速器、高性能数字接收机、无人驾驶车辆感知/决策芯片等[16,30,32-36]。

表7 CRAFT 项目历年投资情况 单位:万美元

4.4 SHIELD项目

为了加强对微电子器件产品流通过程的管控,DARPA 于2014 年启动了SHIELD 项目,希望研发出能随时随地确认器件真实性的技术。

研究内容。重点研发小晶片(dielet)及配套技术,包括可感知X 射线、可见光、高温等使用环境及捕捉对芯片进行成像、去胶、去帽等行为的无源传感器,以检测和记录试图伪冒、非法访问和逆向破解等行为;采用不易破解的加密算法和抗逆向工程技术,以保障密钥安全;可实现无线供电的射频供能技术;采用可进行短时间大数据交换的通信技术;在遭到被整体移除等试图篡改等行为时变得易碎等。小晶片将作为硬件标识与被保护元器件一同封装,但相互之间没有电连接且产生影响;支持大批量、集中、快速、低成本检测;可帮助国防部预防、检测和应对伪冒产品入侵国防电子供应链。小晶片结构如图2(a)所示[38-39]。

图2 SHIELD 项目

主要成果。项目历时5 年,总投资6 475 万美元,历年投资情况如表8 所示[27-29,31-34]。项目已研发出小晶片,采用14 纳米的CMOS 工艺,面积为100 微米×100 微米、厚度为10 微米、成本小于1 美分、如图2(b)所示[16,28-30,32-35]。国防部还建立了一个在线数据库,记录每一个小晶片的状态和位置。在检测中,首先采用手持式或自动探头靠近小晶片进行扫描,再使用手机等便宜通用设备将序列号上传至服务器。该服务器将向小晶片发送未加密的问题,小晶片将从无源传感器发送回带有篡改指示的加密答案和数据,以比对真伪,工作过程如图2(c)所示。

表8 SHIELD 项目历年投资情况 单位:万美元

4.5 DAHI项目

为了充分利用各种材料和工艺带来的性能优势,DARPA 在“硅上化合物半导体材料”(Compound Semiconductor Materials on Silicon,COSMOS)等项目实现磷化铟(InP)晶体管与硅CMOS 电路集成的基础上,于2011 年启动了DAHI 项目,全力推动更多材料异质集成技术的发展。

研究内容。主要研究在同一硅衬底上的多种材料异质集成工艺、高产量制造能力、新型电路设计与构架。项目拟实现集成的材料和器件包括:(1)硅基CMOS 的模拟和数字IC;(2)氮化镓(GaN)基高功率、高电压和低噪声放大器;(3)基于砷化镓(GaAs)和磷化铟(InP)异质结双极晶体管(HBT)和高电子迁移率晶体管(HEMT)的高速/高动态范围、低噪声电路;(4)基于锑基化合物半导体的高速、低功耗电子器件;(5)用于直接带隙光子源和探测器的化合物半导体光电器件,以及硅基调制器和波导等;(6)传感器、执行器和射频谐振器用微机电(MEMS)器件;(7)热管理结构。项目将构建出真正的片上系统并大幅降低尺寸、重量和体积。研究成果将转移到国防部的可信制造厂中,推进技术的持续迭代,并供国防部实验室、联邦政府投资的研发中心、学术界和工业界使用[40-41]。

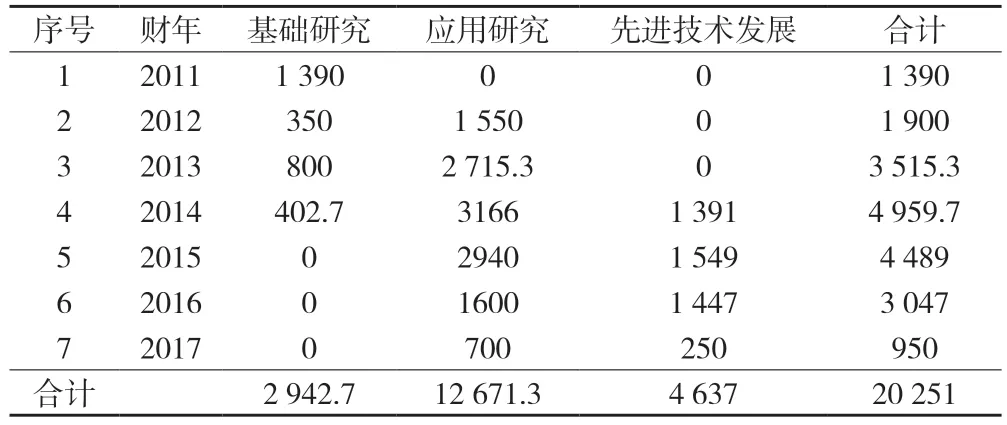

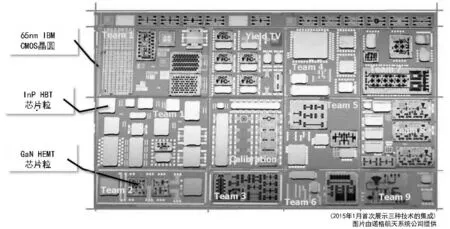

主要成果。项目历时7年,总投资2.025 1亿美元,DARPA 在基础研究、应用研究和先进技术发展三部分预算都给予了资金支持,历年投资情况如表9 所示[23-30,32-34]。项目最终开发了一个高产量、高良品率、高可靠性、可转移至代工厂持续运行的异质集成工艺。为了演示和验证研究成果,项目实现了低噪声放大器、高速跟踪和保持电路、射频数模转换器和可调谐带通滤波器等异质集成射频/混合信号电路,低噪声激光器、光射频信号源、成像阵列芯片和片上激光雷达等光电器件,实现集成多相发射机和压控振荡器-放大器链,可满足雷达、电子战和通信等下一代系统使用需求[23-30,32-34]。2015—2016 年,项目以MPW 方式进行了三次流片。图3 为2015 年1 月硅、InP 和GaN 三种材料制成的小芯片(chiplet)的异质集成的首次展示[42]。

表9 DAHI 项目历年投资情况 单位:万美元

图3 硅、InP 和GaN 三种材料所制造的小芯片的首次异质集成

4.6 CHIPS项目

2014 年,DAHI 项目在执行过程中开发出了三种基于小芯片的异质集成工艺中。DARPA 从2015年启动CHIPS 项目,着重研发可用于异质集成的小芯片,颠覆传统单片集成电路的设计和制造方式。

研究内容。CHIPS 原名“快速和大型混合信号设计”(Fast and Big Mixed-Signal Designs,FAB),2017 年更名为CHIPS。主要研究四个领域:(1)研制大量具备多种功能、可高度复用的小芯片,重点是将现有一系列数字、模拟、射频电子系统和器件模块化,并不研发新的器件技术和电路结构;(2)建立一套通用数字、模拟接口标准,重点是在现有庞大的接口标准中筛选并建立最小接口标准集,并不主动制定新结构标准;(3)研发可实现异质集成、模块化设计的设计工具,简化小芯片的设计开发;(4)研发配套的集成和组装方法[43]。这些小芯片已预先设计好并物理实现,可在通用架构下通过通用接口,以快速组装方式实现各种功能和更新换代,解决复杂IC 的设计难题,并大幅降低研制成本和交付周期,如将IC 的研发成本从现在的500~1 000万美元降到200 万美元,研发时间从21 个月减少到7个月。这种模块化新范式不仅为美国国防部实施“微系统”战略提供技术路径,更可能对现有电子元器件设计和制造流程进行重组,不再需要设计、验证和制造等环节,如图4 所示[44]。

图4 CHIPS 项目将重组电子元器件供应链

主要成果。项目原定研发周期为四年,目前仍在进行中,已累计投入8 507.3 万美元,历年和未来两年投资情况如表10 所示[29-30,32-36]。CHIPS 项目成果的报道不多,可知的有美国英特尔公司在2018 年发布了开放源码AIB 协议[45],是一种时钟转发并行数据传输机制,主要针对英特尔的嵌入式多芯片互连桥接(Embedded Multi-Die Interconnect Bridge,EMIB)封装技术。2020 年3 月,美国Ayar公司通过AIB 接口用其高效光信号接口(I/O)电路TeraPHY 小芯片替代了FPGA 传统接口电路,并通过EMIB 实现了与英特尔公司FPGA 产品的共同封装[46]。由于小芯片和异构集成正好成为应对摩尔定律发展受阻及需求多样化的最好解决方案,受到了整个半导体产业界的高度关注。英特尔、AMD 和台积电等公司积极研发先进集成技术和推出了小芯片产品。

表10 CHIPS 项目历年投资和未来两年预算 单位:万美元

4.7 SPADE项目

DARPA 于2017 年3 月 启 动SPADE 项目[47],并表示其是“电子复兴计划”(Electronics Resurgence Initiative,ERI)的研究基础之一,但未公开SPADE 项目的研究目标、内容及资金预算等信息,只能在零星资料中得出以下内容。项目建议,在可信代工厂内生产为关键数据和算法提供加密和保障的可信器件,并与最先进商业芯片共同安全封装。这些可信器件的功能主要分为两部分,一是保存敏感信息、秘钥等,执行敏感逻辑控制功能;二是主动监测进出商业芯片的所有数据、控制指令、状态和权限等,一旦发现后者受到攻击,立刻实施隔离以减少风险[42]。

4.8 VAPR项目

DARPA 一直关注并投资支持可自分解电子元器件的基础性研究[48-49],并于2013 年底启动了VAPR 项目,正式提出“瞬态电子”这一全新概念并全面推进发展。

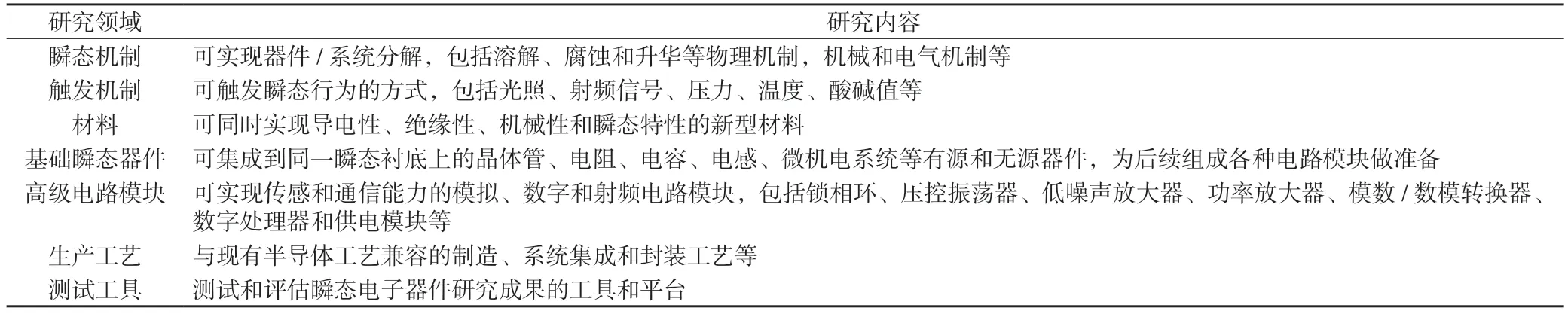

研究内容。瞬态电子器件能够具备多种功能,只在一个非常短和已经确定好的时间段内工作,在光、热和液体中等条件瞬态触发后迅速或以设定的速度自分解和消失。项目将开发和建立一套瞬态机制、支撑材料、器件和模块、配套工艺等,具体如表11 所示。开发出的瞬态电子器件性能可与COTS相比,瞬态特性则可预先编程、实时调整、根据命令触发和/或对环境敏感。瞬态电子器件除了可减少对环境的污染、使病人不再经受医疗设备从体内移除之苦,重要的是可保证军事秘密和先进技术不落入敌手[50-52]。

表11 VAPR 项目研究内容

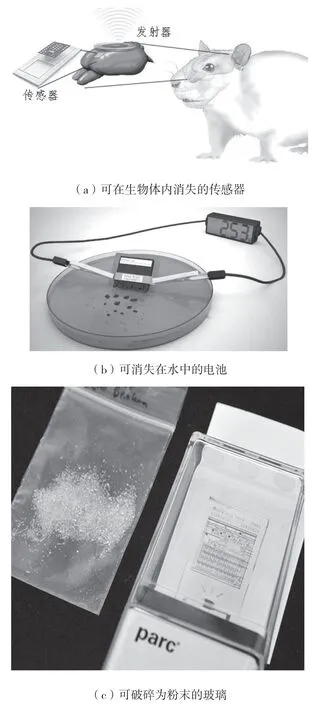

主要成果。项目历时四年,总投资3 807.2 万美元,DARPA 基础研究和应用研究都给予了资金支持,历年投资情况如表12 所示[28-30,31-34]。项目研发出了快速蚀刻、溶解、升华和碎裂等多种瞬态机制;可预测瞬态效应的力学、应力、腐蚀速率建模工具;聚碳酸酯基材料、应力工程基底、水凝胶等可将电子特性和瞬态特性结合起来的新材料;瞬态器件的制造方法,可实现具有射频、存储器、数字逻辑、电源等关键功能的瞬态电子器件的制造[28-30,31-34,52]。

表12 VAPR 项目历年投资情况 单位:万美元

成果举例。在该项目支持下,美国伊利诺斯大学香槟分校等联合开出米粒大小的全新微小超薄电子传感器,可植入头部监控头骨内压力和温度等参数,测量精度与传统设备相当,可在不需要时完全无害地溶解到生物体内的液体中[53],如图5(a)所示;美国爱荷华州立大学研究出可自分解锂离子电池,尺寸为5×6×1 立方毫米,可提供2.5V 电压,为桌面型计算器供电15分钟,在置入水中30分钟内消失,是首个展现出具有实用价值电量、稳定性和寿命的瞬态电池[54],如图5(b)所示;美国帕洛阿尔托研究中心(Palo Alto Research Center,PARC)研发出应力工程玻璃基板,可在收到自毁电流信号将其上的芯片一同碎裂为图5(c)中左侧的粉末[55]。

图5 VAPR 研究成果示例

4.9 TIC项目

2011 年,为使国家情报部门也能利用先进制造能力制造所需集成电路及保障其中信息安全,IARPA 在DARPA TRUST 项目的基础上另辟蹊径,提出将制造过程拆分的新思路,并启动了TIC 项目。

研究内容。项目重点研究将微电子器件制造过程拆分为前道(Front-End-of Line,FEOL)和后道(Back-End-of Line,BEOL)的技术及可行性。前道在海外的先进制造工厂实现基础材料的生长,后道在美国的可信代工厂内进行可信金属化等来实现功能,如图6 所示,以此实现隐藏功能、保证安全、保护IP[56-57]。研究领域包括:制造过程的安全拆分,可在FEOL 阶段隐藏电路功能的技术,电路性能验证及表征,新的晶体管/电路设计及新堆叠方法等。研究对象是8 寸及以上晶圆,0.25 微米及以下特征尺寸的高性能微电子器件。

图6 TIC 项目拆分制造过程示意

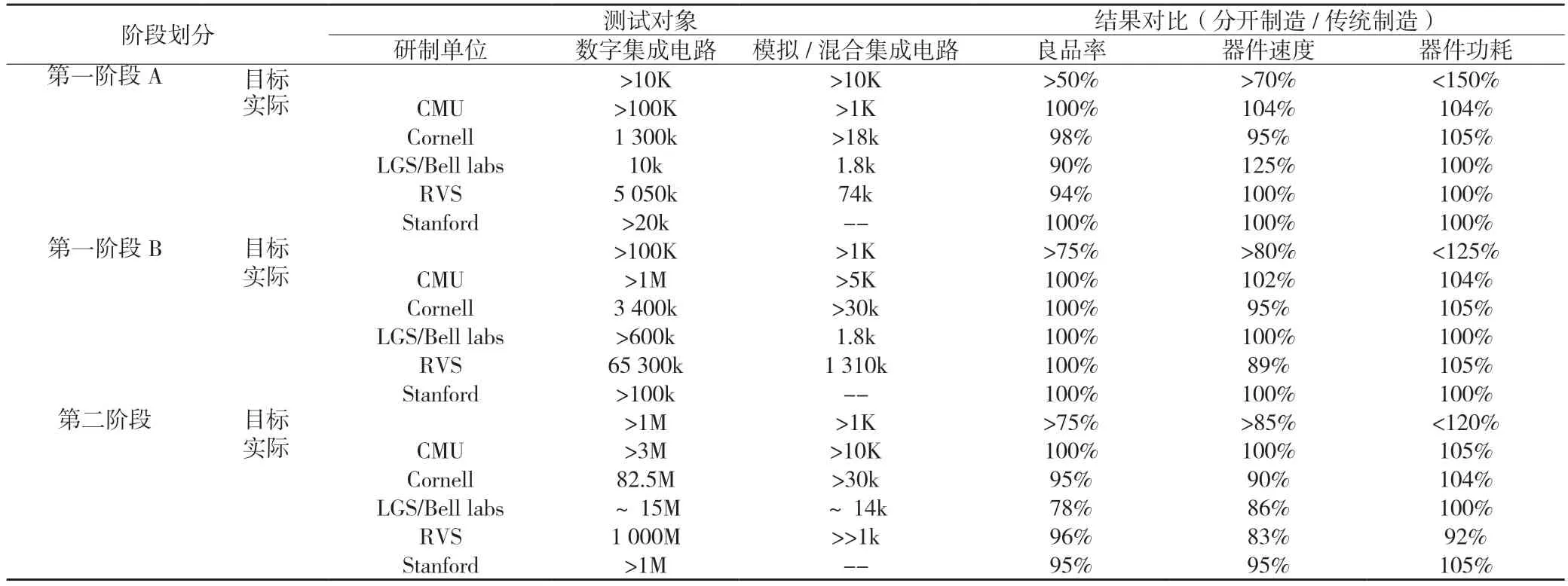

研究成果。TIC 项目历时6 年,由于美国国家情报项目(National Intelligence Program,NIP)的预算不公开,所以TIC 的资金投入情况未知[58]。在项目的第一、二阶段,IARPA 分别采用130 纳米、65 纳米和28 纳米工艺及MPW 形式,对卡纳基梅隆大学(CMU)、康奈尔大学(Cornell)、LGS/贝尔实验室(LGS/Bell labs)、雷声视觉系统公司(RVS)、斯坦福大学(Stanford)共5 家承研单位设计的数字集成电路和模拟/混合集成电路芯片,分别采取了传统制造和分开制造的方式,选取器件的良品率、器件速度和功耗三个指标,以分开制造方式所得芯片性能指标除以传统制造所得芯片相应指标作为衡量分开制造效果的比对数据。传统制造、分开制造的FEOL 和BEOL 所选厂商及地点如表13 所示。第一阶段A、第一阶段B 和第二阶段的比对数据如表14 所示。可以看出,除了雷声公司一款采用28 纳米制造的器件在速度指标上略低于预期目标,在其他指标中是否分开制造并无显著差异[57][59]。

表13 TIC 项目各阶段制造地选择详情

表14 TIC 项目研究成果对比

5 做法借鉴和预警

5.1 围绕发展主线和已有基础建立体系化能力

发展思路一脉相承,实现器件整体能力提升。在国防部提出新安全发展需求时,DARPA 并没有设置新的项目,而是积极引入此前项目的研究成果,并与为应对“摩尔定律趋缓”而发展的芯片模块化和异质集成的发展思路保持同步,如CHIPS、DAHI、CRAFT 三个项目也是DARPA 著名“电子复兴计划”的研究基础,以此在最快时间、用最低成本完成安全保障能力的构建,并更好地融入美国国防部所提出的“微系统”发展大战略中。

分阶段逐步推进,及时调整和完善。在TRUST项目启动之初,DARPA 曾野心勃勃地设置了三个方向以应对安全问题,第一是开发可快速分析微电子器件版图的技术和工具。第二是将复杂IC 拆分为较小的子电路,再进行堆叠或单片集成。第三是研发为IC 添加“硬件保护套”的新技术,可监视IC性能并在出现未预期操作时报警。但随着项目的进行,DARPA 将TRUST 项目研究集中在第一个方向,后两者则是待相关技术成熟后通过另设CHIPS 和SHIELD 等项目来完成。

项目设置体系化,强调从研到用。上述九个项目都是为解决具体问题而设,具有刚性应用要求,为此DARPA 通过体系化设置研究内容来保障该目标的达成。如多个项目都强调了对材料、模型、电路结构和体系架构、制造工艺、测试样品、标准和规范、配套设计流程和软件工具等的全方位研究;同时注重与现有产业基础的融合,以降低产业界接受的门槛,获取最大生态系统支持。

5.2 美国可能利用技术优势对我发起攻击和形成压制

首先,美国已具备微电子器件产品供应链流转跟踪能力,以及针对多种攻击的检验检测能力,美国完全有可能变守为攻,以极低成本,通过植入缺陷、嵌入恶意木马、投入伪冒和质量不合格产品等各种方式,对我国各领域用电子元器件发起全面攻击,而无误伤自己之虞。由于元器件在整个电子信息产业中的核心和基础地位,所造成的影响势必会呈指数级放大。而且,美国还有可能为此前美国多次宣称“中国监听、监视、攻击美国”的蓄意抹黑提供一个“确凿的证据”[5]。

其次,美国国防部正转向采用更通用、低成本和已就绪的通用电路,仅通过改编软件就可使电路实现所需的专用性能,还将加大对先进商用技术的使用力度,军用微电子器件的性能和开发效率都将得到显著提升,将极大地促进美国下一代武器装备的研发和提升现有装备实力。再加之美国对我国半导体产业的全力打压,不仅将限制我国半导体产业整体技术水平的提升,还有可能对我国形成军事压制。

5.3 我国也应加强小芯片和安全技术的发展布局

小芯片和先进集成技术正带来新发展范式,成为半导体产业的争夺热点。小芯片的研发和制造、在系统中的复用和协同,以及配套的仿真和制造工具,将共同构建出一个全新生态系统,美国已展开了全面布局并加速取得进展。小芯片提供了区别于传统摩尔定律的另外一条发展道路,但并不是我国“弯道超车”的机会,相反是对我国半导体设计、制造、封测各环节技术实力的一次“大考”,每个环节都需要在多年不断的积累和沉淀上不断创新。我国也必须重视小芯片的发展,持续推进在小芯片研制和性能检测、标准起草、设计工具的研制、先进异构集成技术等领域的研究,以跟上产业发展的步伐。

我国所使用的电子元器件大量依赖进口,并广泛地应用于国防、电力、交通、金融等国家关键设施和重大任务系统,存在极大安全隐患。我国也必须加强安全技术的研究,不仅可以更好地保障我国所用电子元器件具备所需的性能和可靠性,避免出现存在漏洞、缺陷、伪冒等情况,也是防范他国在元器件层面对我国发起攻击的必要前提。