基于FPGA的多通道出砂振动信号缓存系统研究

王炳友,党 博,党瑞荣,王 港,王新亚

(西安石油大学,陕西省油气井测控技术重点实验室,陕西西安 710065)

油气井出砂是油气生产者所须面对的一个严重问题。出砂监测技术可以给油气生产者提供目标井的实时出砂量,为生产者做出决策提供出砂量数据参考,是解决油气井出砂问题的关键技术[1-3]。在出砂监测领域,最具行业认可度的公司是挪威的clampon公司,其最新一代粒子监控器SandQTM采用有源声学和无源声学相结合的原理实现背景流体流速测量和出砂监测的目的,由于SandQTM自身解决了出砂量反演所必须的背景流体流速,所以该仪器在出厂后无需再进行现场校准[4]。采用无源声学原理,利用线性阵列式出砂监测探头,结合阵列信号处理技术同样可以实现对背景流体流速间接测量的目的,并且还可以实现对背景噪声的抑制[5,6]。线性阵列式出砂监测探头的有效使用需要有多通道同步数据缓存系统的支持。现有的多通道数据处理系统架构多侧重于多通道数据处理算法的并行加速以及多通道数据采集,并未涉及到通道间控制逻辑的关联性,同时,也没有考虑前端AD转换器和后端数据处理子系统间的数据速率匹配问题[7-11]。现有的面向阵列式出砂监测探头的数据采集系统实现了多通道数据的同步采集,但预触发方法和数据缓存架构存在诸多问题[12]。例如,固定阈值触发的漏触问题和数据采集板卡与上位机通信期间可能发生的有效数据遗漏问题。针对以上问题,本文从线性阵列式出砂监测探头的多通道同步数据缓存需求以及保证波形完整性的数据预触发需求触发,充分考虑数据自适应触发、有效数据遗漏等问题,提出了一种适合FPGA器件实现的,具有自适应预触发功能的多通道出砂振动信号缓存系统架构,其采用新的自适应触发方法,并融入了数据乒乓操作的思想。实例测试结果表明,基于该系统架构设计的多通道数据缓存系统能够完成连续数据流的自适应预触发缓存,系统架构功能完整而有效。

1 多通道高速数据缓存系统关键技术

1.1 自适应阈值触发

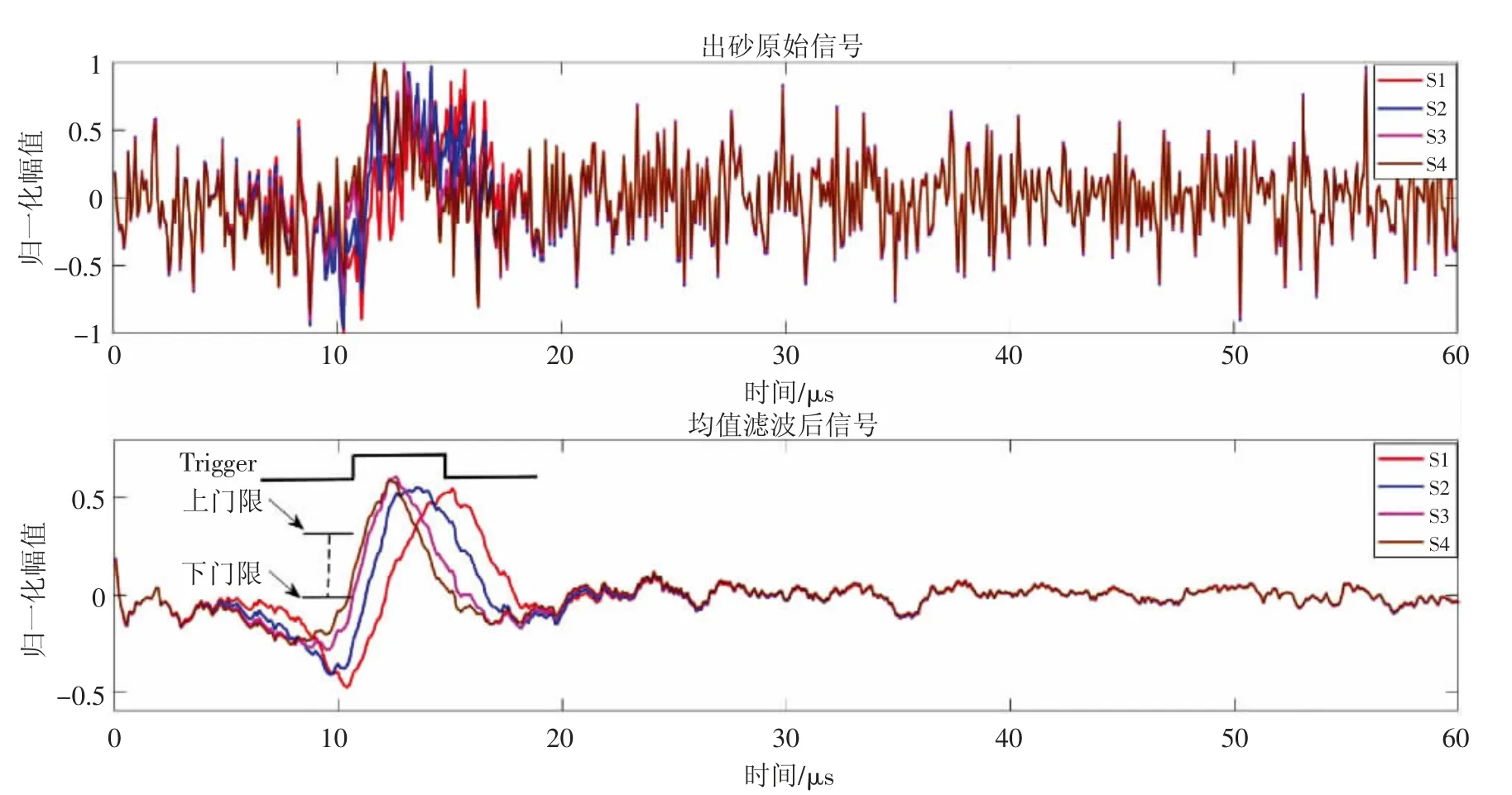

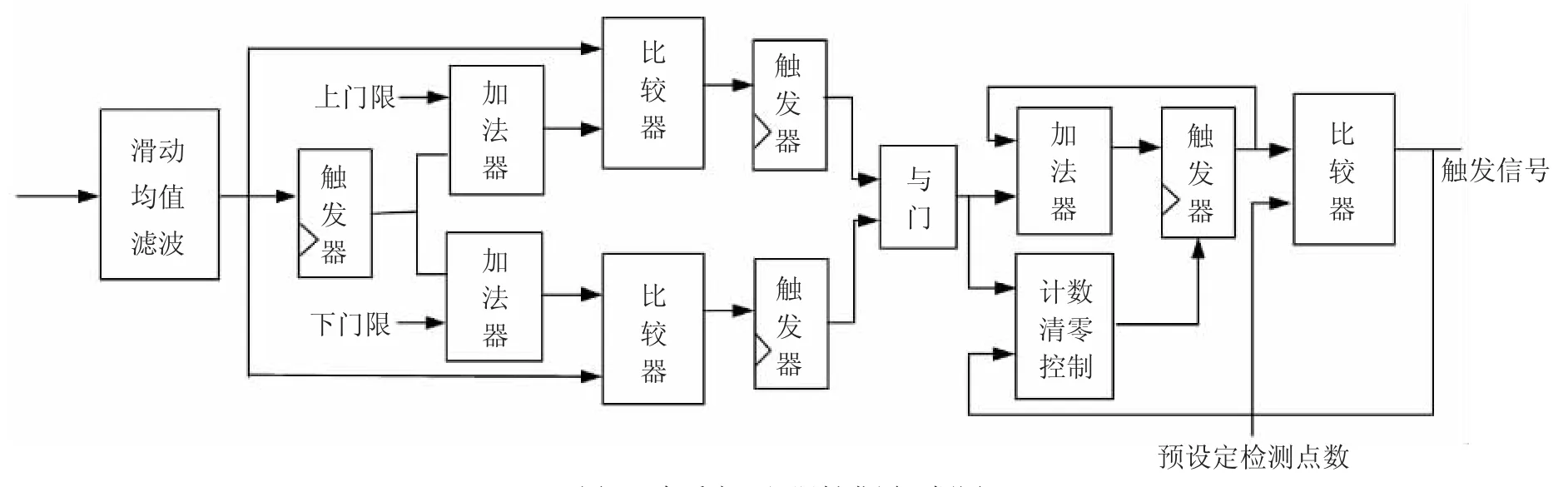

对于应用于阵列信号采集的信号采集系统,预触发功能是保证系统工作效率的关键。预触发即在有效信号到来时刻“之前”触发存储模块的写控制信号,从而缓存完整的有效信号,缓存数据所对应的时刻点应包括有效信号到达时刻及有效信号到达前一定数量的时刻点。预触发机制的难度在于触发方式及触发参数的选择,它与采集系统将面对的信号特征密切相关。理想情况下,希望信号采集系统的触发时刻点就是有效信号的到来时刻,但是,在实际工作环境中,由于测量信号背景噪声的影响,信号采集系统的预触发机制不可能准确地识别有效信号到来时刻。因此,只能选取一种恰当的预触发机制并设置合适的触发参数,以准确的缓存包括有效信号到达时刻点在内的数据帧,而不再关心预触发机制是否在有效信号到达时刻点处被触发。预触发机制的触发时刻即触发点,触发后缓存数据帧中触发点之前的数据深度即预触发深度。还有,由于有效信号幅度值的不同,预先设定的预触发参数并不一定适合所有的有效信号,以此系统所面对的出砂信号为例,当管道中流体流速降低时,砂砾撞击管壁产生的振动信号幅值也会减小,但是遇到这种情况,信号采集系统的预触发机制要能够自动适应。为提高预触发机制对测量信号背景噪声的兼容能力,降低误触概率,同时,提高预触发机制对有效信号幅值的兼容能力,降低漏触概率,设计了双门限自适应预触发机制(见图1),电路原理框图(见图2)。

图1 双门限触发示意图

图2 自适应双门限触发原理框图

自适应双门限触发电路工作原理:原始采样信号经过滑动均值滤波模块降噪后,上一时刻的采样数据点更新比较器上下门限,比较器利用上一时刻采样数据更新后的上下门限对下一时刻采样数据进行比较,如满足条件则计数器加一,直到计数器的值等于预设定检测点数,触发信号有效。如在计数过程中出现不符合条件的突变采样点,计数器在下一个时钟上升沿到来后清零;当一次触发完成,计数器会在下一个时钟边沿到来后归零。此时,触发门限不再是固定值,触发方式也不再是点触发。触发模块检测的是目标信号的某段上升沿,从而降低误触概率及漏触概率。

1.2 乒乓操作

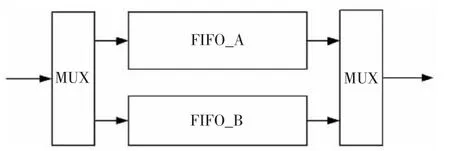

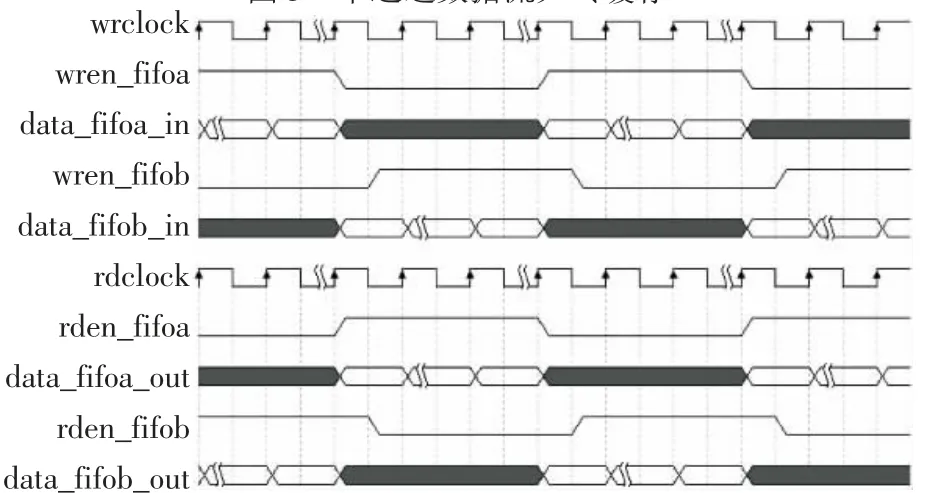

数据流乒乓操作是一种增加设计复杂度及逻辑资源消耗,来保证对连续数据流缓存的一种方法[13]。乒乓操作的核心是使数据缓存单元的读写周期重合,以避免由于读写等待所造成的数据流部分丢失,从而可以对连续高速数据流进行缓存。注意,乒乓操作可以缓解下游信号处理模块的数据处理压力,避免数据堵塞,这是以提高下游信号处理模块的工作时钟频率为代价的,如果下游模块对缓存单元的数据读取速率低于写入速率,使用乒乓操作依旧无法对连续高速数据流进行缓存。单通道数据流乒乓操作模块图(见图3),乒乓操作数据流读写时序(见图4)。

图3 单通道数据流乒乓缓存

图4 数据流乒乓操作时序图

2 带有预触发功能的连续数据流缓存架构

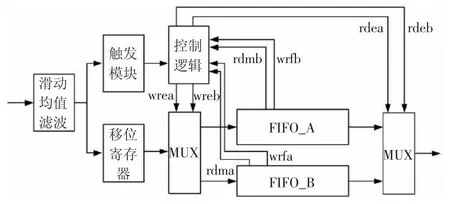

其中,wrea,wreb分别为FIFO_A和FIFO_B的写使能信号;wrfa,wrfb分别为FIFO_A和FIFO_B的写满指示信号;rdea和rdeb分别为FIFO_A和FIFO_B的读使能信号;rdma和rdmb分别为FIFO_A和FIFO_B的读空指示信号。连续数据流触发缓存结构(见图5)融入了数据乒乓操作的思想,对于每一个数据流缓存通道,使用两个相同的FIFO模块,以解决非连续数据流缓存结构读期间不能写所造成的有效数据遗漏问题。

图5 连续数据流预触发缓存结构

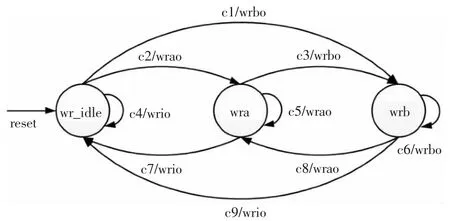

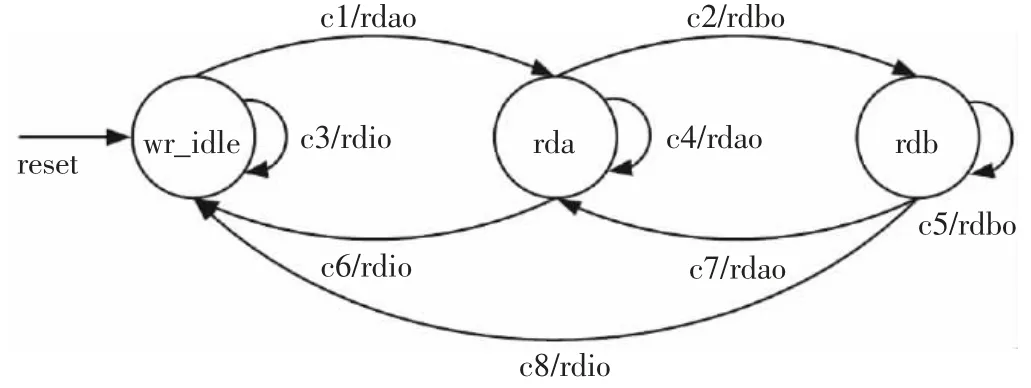

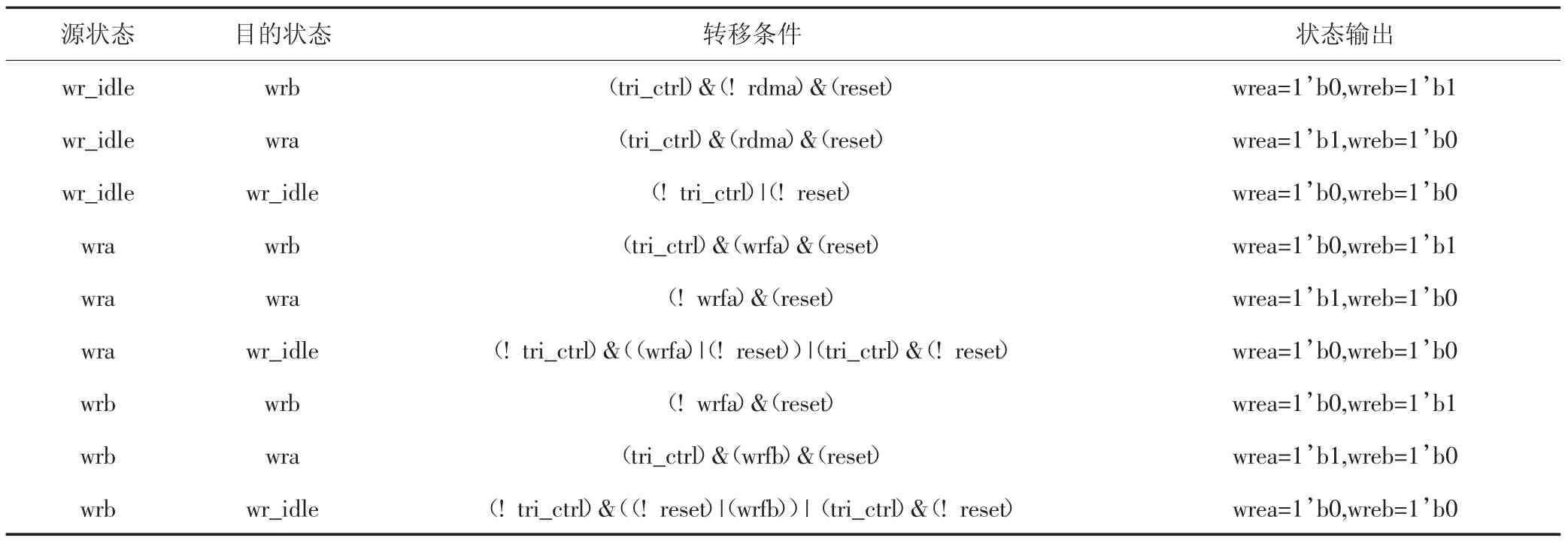

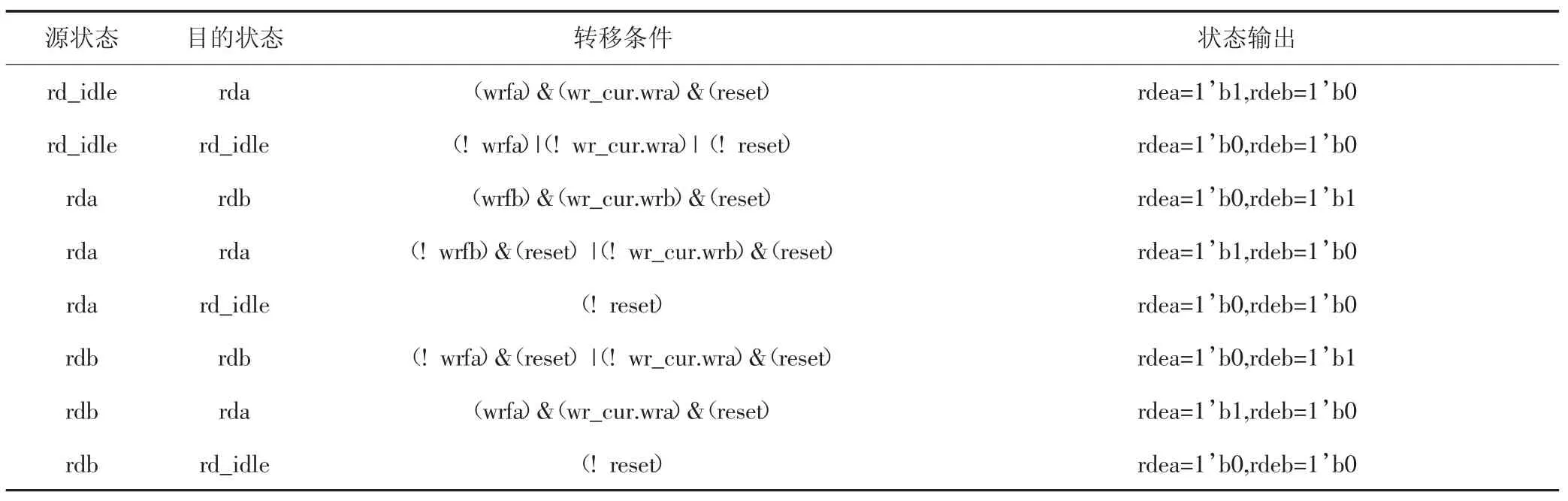

连续数据流预触发缓存结构相比非连续数据流预触发缓存结构在控制逻辑上要复杂,为了更好的描述连续数据流预触发缓存结构控制逻辑的工作过程,分别给出了控制逻辑中的写操作状态机和读操作状态机(见图6、图7);状态转移表(见表1、表2)。

图6 写操作状态机

图7 读操作状态机

结合连续数据流缓存结构写操作状态机状态转移图和状态转移表,连续数据流缓存结构的写操作过程如下:模数转换器输出的原始数字信号,经滑动滤波模块降噪后,被平滑滤波后的数据流同时进入预触发模块和移位寄存器,预触发模块和移位寄存器一直处于工作状态。当进入预触发模块的数据满足触发条件后,触发标志信号tri_ctrl有效,写时钟上升沿翻转电平,高电平有效,持续时间一个时钟周期;当触发信号有效后,如果写操作状态机处于空闲状态wr_idle且FIFO_A读空,则下一个状态进入wra,即FIFO_A写状态,若FIFO_A非空,则下一个状态进入wrb,即FIFO_B写状态;当触发信号有效后,如果写操作状态机处于写FIFO_A的状态,即恰好写完FIFO_A,FIFO_A的写满标志有效,则下一个状态进入FIFO_B写状态;当触发信号有效后,如果写操作状态机处于FIFO_B写状态,即恰好写完FIFO_B,FIFO_B的写满标志有效,则下一个状态进入FIFO_A写状态。注意,在FIFO_A或者FIFO_B写满后,如果没有触发标志信号,则写操作状态机会返回空闲状态。在读时钟速率大于写时钟速率的情况下,不可能出现FIFO_A和FIFO_B同时写满的情况。利用连续预触发数据流缓存结构做单通道或多通道数据采集处理系统,其面对的最差情况就是FIFO的读写时钟频率相等,一般情况下,FIFO的写时钟频率远小于读时钟频率,因为要利用读写时钟频率差预留出一帧有效数据的处理时间。

表1 写操作状态转移表

表2 读操作状态转移表

连续数据流预触发缓存结构的读操作状态机并不是独立的,读操作状态机的状态切换与写操作状态机的当前状态有关。读操作状态机工作在写时钟域,并非工作在读时钟域,其中的原因是为保证FIFO读写使能信号电平翻转的同时性,保证FIFO读写周期时间的相等,这是理想乒乓操作的时序要求。读操作状态机的工作过程如下:复位后,读操作状态机处于空闲状态rd_idle,当写操作状态机处于FIFO_A写状态,即表2中的wr_cur.wra有效,且FIFO_A写满标志信号有效,则读操作状态机的下一个状态是rda,即FIFO_A的读状态,否则,读操作状态机状态不跳转;如果读操作状态机的当前状态是FIFO_A读状态,当写操作状态机处于FIFO_B写状态,即表2中的wr_cur.wrb有效,且FIFO_B写满标志信号有效,则读操作状态机的下一个状态是rdb,即FIFO_B读状态,否则,读操作状态机状态不跳转;如果读操作状态机的当前状态是FIFO_B读状态,当写操作状态机处于FIFO_A写状态,即表2中的wr_cur.wra有效,且FIFO_A写满标志信号有效,则读操作状态机的下一个状态是FIFO_A读状态,否则,读操作状态机状态不跳转。

3 系统集成及功能测试

3.1 系统集成

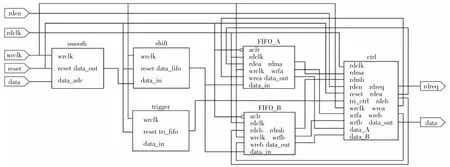

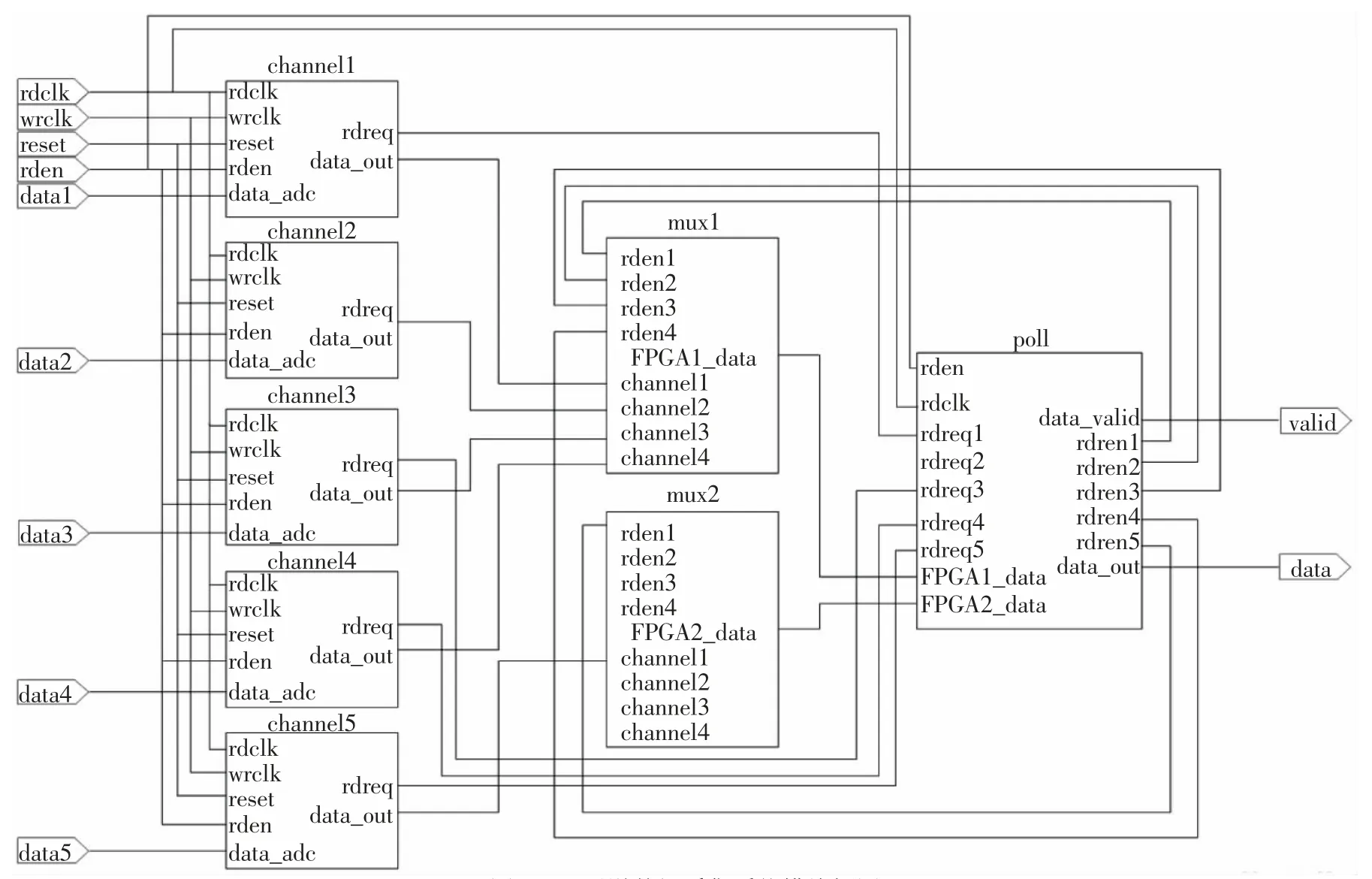

在上述理论分析的基础上,使用硬件描述语言,搭建了基于连续数据流预触发缓存结构的单通道数据采集系统,综合后模块框图(见图8)。多通道数据采集系统是在单通道数据采集系统的基础上进行搭建,综合后模块框图(见图9),其搭建方法也很简单,只需将多路独立的预触发信号或运算后输入各通道控制逻辑模块,然后各通道数据在高速读时钟的作用下轮询输出即可。

3.2 功能测试

3.2.1 仿真测试 利用采集的砂砾撞击管壁产生的振动信号,针对五通道数据采集系统的设计要求,制作测试所需的数据文本文件,编写测试脚本。使用Modelsim软件进行测试。

图8 单通道数据采集系统模块框图

图9 五通道数据采集系统模块框图

图10 板级测试系统框图

由测试结果可以看出,触发模块正常工作,未受信号幅值变化的影响;五组有效信号组成的连续数据流被成功缓存,未出现有效数据丢失现象。这说明基于连续数据流预触发缓存结构的五通道数据采集系统工作各子通道工作正常,并满足指定设计要求。顶层模数据输出端口在每个读缓存周期都会读出五组同一有效信号,这说明在单通道数据采集系统的基础上搭建的五通道数据采集系统工作正常,可以实现连续数据流的多通道同步采集,同时,也说明本文提出的连续数据流预触发缓存结构支持多通道扩展。

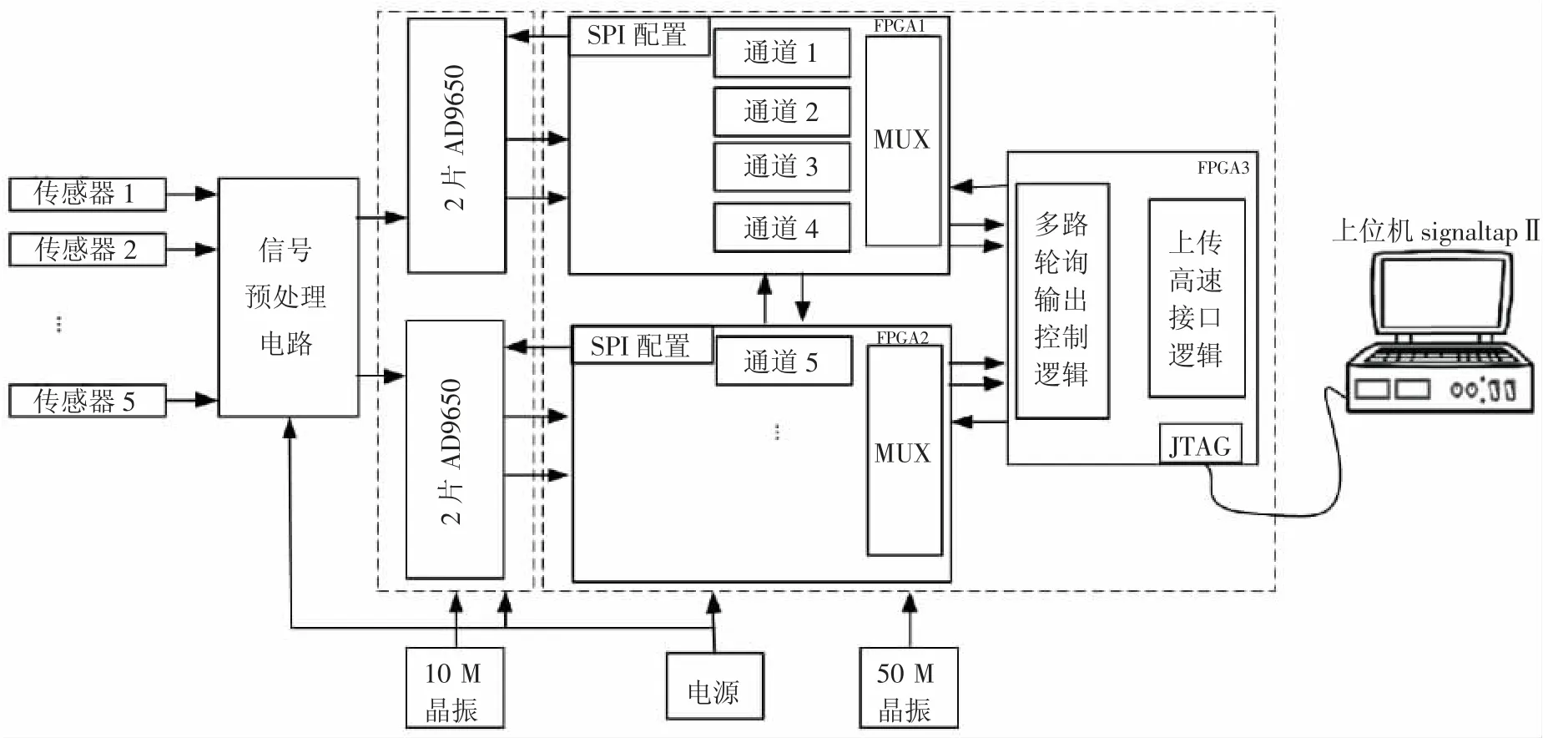

3.2.2 板级测试 在仿真测试的基础上,为测试基于连续数据流预触发缓存结构的五通道数据采集系统的实际工作性能,利用实验室现有的多通道数据采集板卡、任意信号发生器及signaltap II嵌入式逻辑分析仪进行了系统的板级测试。多通道数据采集板卡载有4片AD9650模数转换器,采样率为10 MHz,输出数据格式为有符号16位。板卡载有FPGA芯片三片,为Intel公司的EP4CE6E22C8芯片。AD9650与FPGA芯片之间的数据通信接口为16位并行接口。完成五通道数据采集系统的移植后,板级测试系统框图(见图10)。现设置系统模数转换器为10 MHz,即数据写时钟频率为10 MHz,数据读时钟频率为50 MHz,任意信号发生器充当信号源,signaltap II逻辑分析仪作为上位机。

板级测试结果与仿真测试结果一致,实测结果进一步证明了连续数据流缓存结构功能的完整性。此外,由图10板级测试系统框图可知,连续数据流缓存结构具有良好的通道扩展性,且这种扩展性不局限于单片FPGA器件。

4 结语

仿真和实测结果表明基于自适应触发方法和乒乓操作原理的多通道出砂振动信号缓存系统架构能够实现数据自适应触发及连续数据流缓存,可有效降低由于信号幅值引起的误触和漏触概率,避免传统数据缓存架构读写访问冲突所引起的有效数据帧丢失问题。此外,该多通道数据缓存系统架构具有良好的通道扩展性及模块功能独立性,加之架构所使用资源均为常规FPGA器件片上资源,所以系统架构具有良好的可移植性。该多通道数据缓存系统架构不仅能够解决油气出砂监测系统的数据缓存问题,还能够为其他应用场景下的多通道数据采集处理系统的设计提供参考。