基于核间中断实现的嵌入式多核系统通信方法*

(中船重工(武汉)凌久电子有限责任公司 武汉 430074)

1 引言

随着VLSI技术的发展和多核结构模型理论的进一步成熟,2001年IBM公司推出第一个商用的多核处理器POWER4,至此开启了多核处理器新纪元。经过数十年的发展,多核处理器已被广泛应用于多媒体计算,嵌入式设备,个人计算机,商用服务器和高性能计算机等众多领域[1]。多核系统被认为是最能满足那些对性能要求不断增加的嵌入式系统和高性能计算领域[2],通过增加处理器核心数目来提高性能。与单核系统相比,多核系统运行在更低的频率范围来减少能量的消耗以及降低处理器的发热量,通过有效管理多指令同步执行提升多核系统整体性能[3]。

多核处理器带来性能的提升的同时,也有其自身不可避免的缺点。在多核处理器系统中,各核心共用缓存,外部存储空间,网络控制器等资源。运行在多核处理器上的应用程序在共享使用这些资源同时,也会有一些信息交互[4],如果各核间不能进行有效的通信,势必会影响系统整体性能,核间通信成为多核系统的性能瓶颈[5]。

2 核间中断原理

本文选取TI公司的TMS320C6678 DSP平台为研究对象,该处理器是8核同构处理器,采用TI最新的KeyStone架构。每个C66x内核频率为1.25GHz,提供每秒高达40GB MAC定点运算和20GB FLOP浮点运算能力[6]。TMS320C6678处理器内部以及处理器与外部间的通信离不开多核导航器、共享存储器、TeraNet高速互联总线和Hyper-Link 接口[7~8],这些丰富的功能组件配合中断机制的使用能为TMS320C6678芯片提供多种灵活的通信方法。中断机制是现代计算机系统中的基本机制之一,它帮助系统完成对外部各种事件的响应和处理,是实现多道程序设计的必要条件。

2.1 CorePac中断机制

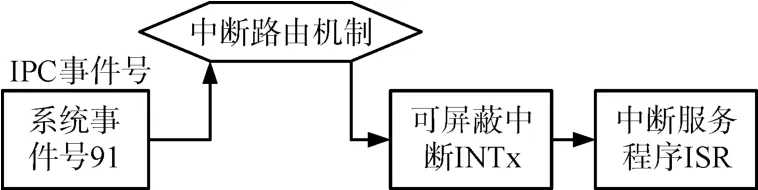

TMS320C6678设备有8个C66xCorePac核心,每个CorePac内部集成了一个中断控制器(INTC),中断控制器对系统中断源进行配置,中断控制器允许最多128个系统事件被路由到12个可屏蔽中断输入(INT4~INT15)中去,这128个系统事件可以是内部事件或者外部事件。中断控制器内部集成有Interrupt Selector和 Event Combiner部件,Interrupt Selector使得编程人员可以将这128个系统事件中的任一事件映射到INT4~INT15中的任何一个,从而完成事件响应。CorePac中总共有128个系统事件,其中4~127号事件是来自芯片内部或者外部的事件,有实际物理意义的。Event Combiner可以将第4~127号系统事件中若干个合成为0~3事件中的任一个,则系统等效有128个事件[9]。CorePac内部中断路由结构如图1所示。

2.2 核间中断

在TMS320C6678设备中91号事件默认对应为核间中断[10](IPC_LOCAL),每个核心通过配置中断寄存器让事件控制器产生91号事件中断。主要配置的寄存器有IPCGRx和IPCARx两种类型,其中IPCGRx为中断生成寄存器,IPCARx为中断确认寄存器,他们共同完成核间中断。TMS320C6678有8个 IPCGRx(0~7)寄存器和 8 个 IPCARx(0~7)寄存器[11]。当向IPCGRx中的IPCG位写1时,将向corex发送一个核间中断,与此同时寄存器将相应的中断确认寄存器的SRCCx位置1。当中断被确认后,寄存器将SRCCx和相应的SRCSx位同时置0。通过查询中断确认寄存器中对应位值,中断服务程序可以知道中断的来源。C6678多核处理器间的核间中断即完成一次中断通信过程。此处的核间通信仅能起到同步通知作用,并不能传输数据信息。核间中断实现过程如图2所示。

图2 核间中断实现过程

DSP工作在有许多外部异步事件存在的环境中,当事件发生时他们要求DSP能够立即去处理该事件。中断是事件用来停止CPU当前运行的任务转而去执行该事件的过程。事件的来源可以是芯片内部或者芯片外部,例如时钟,AD转换,其他外设等。

3 核间通信设计与实现

在嵌入式系统中,中断机制可以平衡外部设备与处理器之间的速度差异,实现更友好的人机交互,是所有处理器必须具备的一个能力。在多核系统中,各种通信方式几乎都离不开中断机制。如SRIO通信方式[12]中有SRIO中断,PCIe通信方式有PCIe中断,EDMA通信方式有EDMA中断[13]等。

中断机制在数据通信中起着重要作用,灵活运用中断机制能够为系统性能带来提升。本文基于TMS320C6678提供的共享存储器,利用多核处理器核间中断机制,设计并实现了一种简易的核间通信方法,下面从通信数据结构、核间中断请求和响应、消息发送、消息接收及消息通信过程五个部分进行详细介绍。

3.1 通信数据结构

在进行数据通信时,消息都是以一定的结构存放于系统内存中,称之为通信数据结构,本文设计的通信数据结构如下:

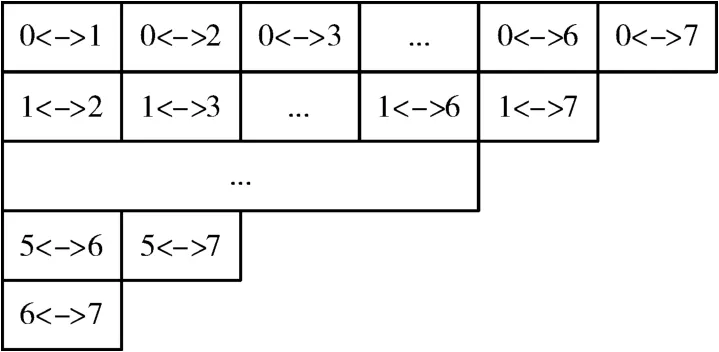

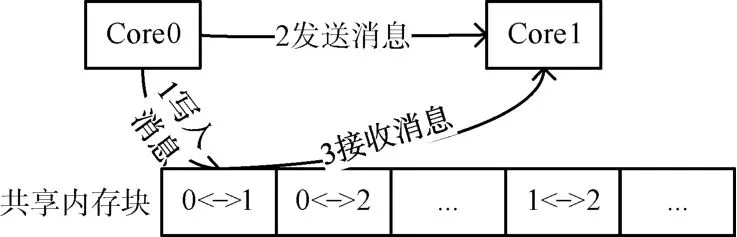

基于TMS320C6678的存储体系结构,将用于通信的数据(即sysMsg类型数据)存放于共享内存(如:DDR3)中,以实现多核间的数据通信。由于多核之间可相互进行通信,且多核之间并行运行,如果使用同一块共享内存,那么多核之间必然存在竞争,可能导致系统死锁或者数据无效,因此,需要对共享内存空间进行划分。本文设计的通信方法为每一对通信核单独划分一块固定的共享内存块,这样可以避免多核并行运行时系统出现错误,如图3所示,TMS320C6678有8个核,两两组成一对通信核,因此,将共享内存划分为28个固定存储块用于存放sysMsg类型数据,并且,通过sysMsg类型中的标志位域进行通信双方的同步。

图3 共享内存空间划分

3.2 核间中断请求和响应

当消息发送方完成数据发送后,本文设计的通信方法通过核间中断唤醒接收方进行数据接收,避免了查询,提高了处理器利用率和通信效率。

核间中断主要包括中断请求(即触发中断)和中断响应(即运行中断服务程序)。其中,发送方可以通过配置核间中断寄存器产生核间中断,同时将发送方所在核(源核)信息保存在中断确认寄存器中,详细方法参见本文第二章。当接收方所在的核(目的核)响应该核间中断时,将从中断确认寄存器中获取源核信息,同时处理消息数据。由于同一个核可能同时接收来自不同核发送的消息数据,因此,本文设计了一个全局中断服务函数表gFunc,用于存放源核x对应的中断服务函数。当目标核收到源核发送的核间中断后,立即响应该中断跳转到中断服务程序,调用中断服务函数表中的函数进行消息数据处理。中断处理过程如图4所示。

图4 中断处理过程

3.3 消息发送

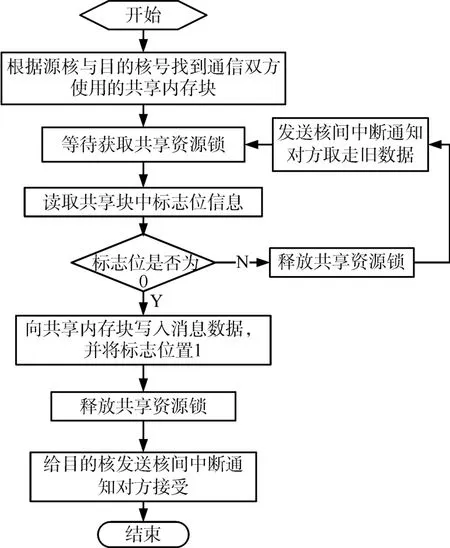

完成通信数据结构定义、共享内存空间划分和中断服务函数设置后,通过消息发送函数进行核间通信。在消息发送过程中,首先,指定发送目的核号;其次,根据通信双方核号查找对应的共享内存块;然后,获取共享资源互斥锁,循环检查标志位状态信息,直到共享内存块可写(即标志位为0);接着,向共享内存块中写入消息数据,设置共享内存块不可写(即标志位置为1),释放共享资源互斥锁;最后,向目的核发送核间中断,通知目的核接收消息。其发送流程如图5所示。

图5 消息发送流程图

3.4 消息接收

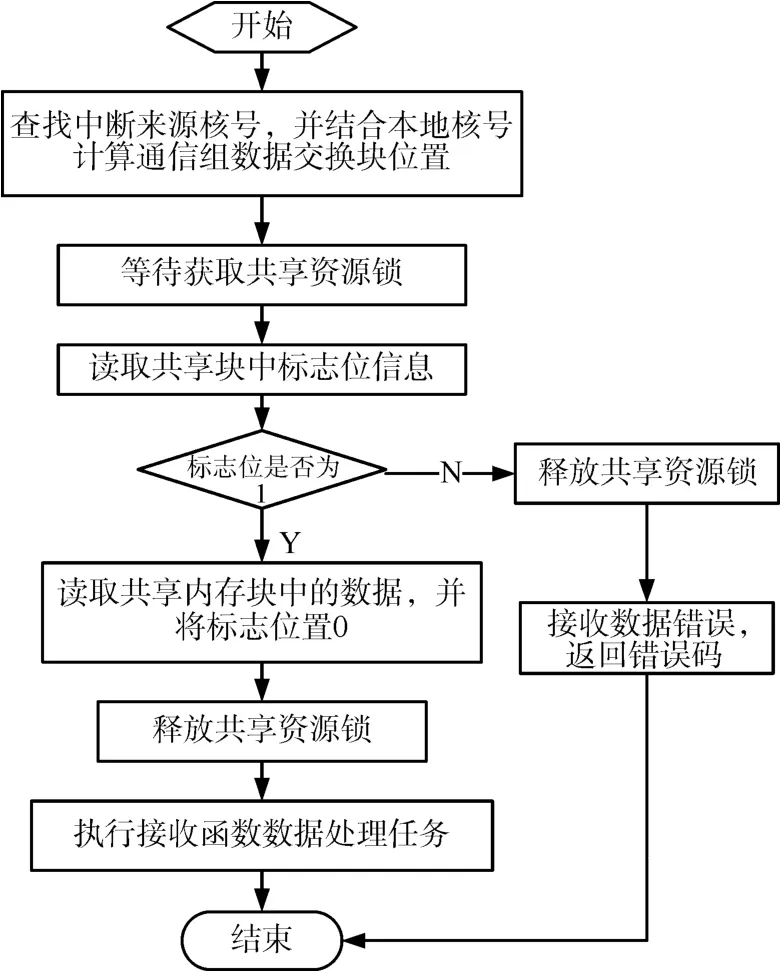

当源核消息发送完成后,通过核间中断通知目的核进行消息接收,即源核将消息写入共享内存块后,向目的核发送核间中断,目的核收到该中断后,立即响应并执行中断服务程序,并根据源核号跳转到对应的中断服务函数中进行消息接收处理。在消息接收过程中,首先,根据源核号与目的核号查找存放消息的共享内存块;然后,获取共享资源互斥锁,循环检查标志位状态信息,直到共享内存块可读(即标志位为1);接着,从共享内存块中读出消息数据,设置共享内存块可写(即标志位置为0),释放共享资源互斥锁;最后,对消息数据进行处理。消息接收流程如图6所示。

图6 消息接收流程图

3.5 消息通信过程

结合消息发送流程和消息接收流程,一次完整的核间消息通信过程如图7所示。

图7 消息通信过程图

消息块结构体包含两个成员,标志位和消息体。标志位用于监控当前传输状态,当标志位为0时,发送方才能向消息体写入数据,当标志位为1时接收方才能从消息体中读取数据。标志位可以保证频繁发送时,前一次发送的数据不被覆盖。下面以核0向核1发送消息为例对传输过程进行说明:

1)核0查看0核和1核这一对通信核对应的共享内存块标志位是否为0,若为0,则转入步骤2);若不为0,则表明上一次传输的消息还没处理,核0向核1发送核间中断,并转入步骤1)。

2)核0向共享内存块的消息体写入数据,并更改共享内存块的标志位为1。

3)核0向核1发送核间中断,通知核1进行处理消息。

4)核1收到核0的核间中断后,进入中断服务程序函数,对共享内存块中的消息体数据进行处理,处理完成后更改共享内存块中的标志位为0。

4 核间通信测试

本文选择TI的TMS320C6678开发板卡作为实验平台,对本文设计的核间通信方法进行压力测试和性能测试。

压力测试通过选取DSP任意一个核作为主核向其他从核连续发送消息,从核收到消息后立即回发给主核一个应答消息,主核收到所有的从核应答消息后进行下一轮测试,该过程持续测试4h,检查系统是否正常运行。

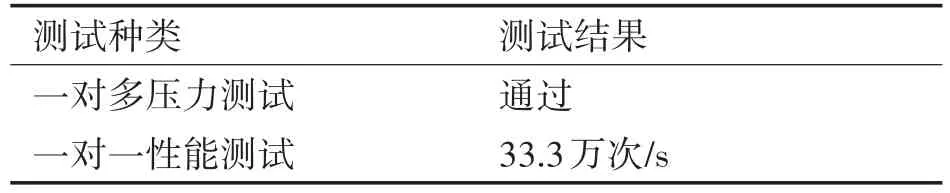

性能测试通过选取任意两个核进行通信,发送核循环向目标核发送100万次消息,目标核收到消息后立即处理,统计发送100万次所耗时间,并计算发送速率,其测试结果如表1所示。

表1 核间通信测试结果

经测试,该核间通信方法可以完成核间消息传输;在进行4h的一对多核传输压力测试过程中,消息无丢失且数据传输正确,该方法可保证消息传输的有效性;在一对一传输速率测试中,测试100万次,其发送速率可达到33.3万次/s。

5 结语

采用多核处理器是提高嵌入式系统性能的一个重要途径,虽然多核系统能较大地提高系统的运算能力,但同时也给应用开发人员带来了一些困难。嵌入式多核系统应用开发所面临的难题之一是多核之间的通信,只有保证通信数据的有效性和实时性,运行在多核处理器上的任务才能高效并行运行,多核处理器的性能才能得到充分发挥。

本文在研究了嵌入式多核处理器架构的基础上,充分利用多核处理器核间中断机制,将共享内存块作为消息载体,设计并实现了一种包含消息发送与接收的多核处理器间消息通信方法。经过测试验证,该方法可以满足多核处理器之间的高效、稳定通信。在后续的研究工作中,可对本方法进行功能扩展与优化,以满足日益复杂的应用场景需求。