FPGA 技术在数字电子技术课程中的探索与实践

王肖君,宋子轩,范越

(海军工程大学 电子工程学院,湖北 武汉)

一 引言

EDA 技术指电子设计自动化技术,已成为现代电子设计的核心技术,是以计算机为工作平台,融合应用电子技术、计算机技术、智能化技术最新成果的电子设计技术,广义上包括IC 设计、电子电路设计、PCB 设计和电子电路仿真等[1]。数字电子技术课程主要侧重数字电子系统设计领域,可编程逻辑器件的应用,而FPGA作为典型的可编程逻辑器件,由于具有高集成度、灵活性和更强的逻辑功能,在通信、人工智能、机器学习等方面应用十分广泛。

二 数字电子技术课程教学思路

数字电子技术课程是本校电子信息类专业必修的学科基础课,在整个人才培养方案中,它是介于科学文化课和首次任职课之间的重要专业背景课,是学员从理论思维转向工程实践思维的重要纽带。现采用的是理论和实验合二为一,总学时数为60 学时,其中包括40 学时理论和20 学时实验实践。传统的教学模式为教员课堂讲理论为主体、实验室实践为辅助,但是由于内容不断更新增加、学时数减少和实验室教学环境限制,存在很多学员在课堂理论学习过程中知识理解不到位、实验照搬课本的问题,课程结束后,大部分学员都难以达到运用电子技术知识解决专业领域问题的水平。针对这种传统教学模式的弊端,在课程教学过程中以强化学员现代电子技术应用能力为目标,以综合实践为主线,将数字电路与FPGA 技术中的部分内容进行融合,重构教学内容,优化教学手段[2]。

(一) 优化调整教学内容

本课程在学时不变的基础上将传统通用逻辑器件与FPGA 技术相结合,教学重点从“培养集成器件的外部特性及应用能力”调整为“器件应用能力+数字逻辑设计思维+语言建模能力”。

课程共十个章节,分别是绪论、逻辑代数与硬件描述语言基础、逻辑门电路、组合逻辑电路、锁存器和触发器、时序逻辑电路、半导体存储器、CPLD 和FPGA、脉冲波形的变换和产生、数模与模数转换器。理论授课时压缩传统卡诺图、多项式化简的学时,减少原有小规模集成电路的讲解,削减TTL 逻辑电路方面的知识。第二章至第六章,每章节结尾穿插讲述Verilog HDL 语言基础知识,讲述硬件描述语言的语法结构及基本建模方法,用硬件描述语言设计常用组合逻辑电路及时序逻辑电路,内容精简但是包含了所有核心要素。学员完全可以通过学习本课程中Verilog HDL 部分就能完成所有的基础的FPGA 设计开发。对于在后续项目设计中遇到需要特殊解决的问题,可通过百度等手段查找资料或参考其他书籍文献。

实验实践课时讲解相关软件和硬件平台的使用,学员一方面需完成简单的74 系列电路实验,同时增加FPGA 相关实验内容,配合自编实验指导书,通过典型实例开展教学,学员通过模仿实例可在短时间内快速掌握Verilog HDL 语言和可编程逻辑器件的基本设计方法。课程以较适合入门的Altera Max 系列FPGA 开发为主线,紧密结合数字电子技术课程内容,层层递进,先对理论课电路的实现进行验证,再进一步深入到FPGA 的综合应用和进阶应用。

(二) 改进教学方式

课程实施过程中全面落实“以学员为中心,突出能力培养”的现代教育理念,探索形成了以“问题驱动、理实一体、自主实践、多维互动和评价反馈”为核心要素的混合式教学,以培养能力为目标、以综合实践为主线,从相互讨论中潜移默化地消化吸收理论知识、加深理解,分析学员数字电子技术学习认知过程的形成规律,统筹规划各类教学实践环节,通过自主实践培养其创新意识和创新精神及独立探索和解决问题的能力。

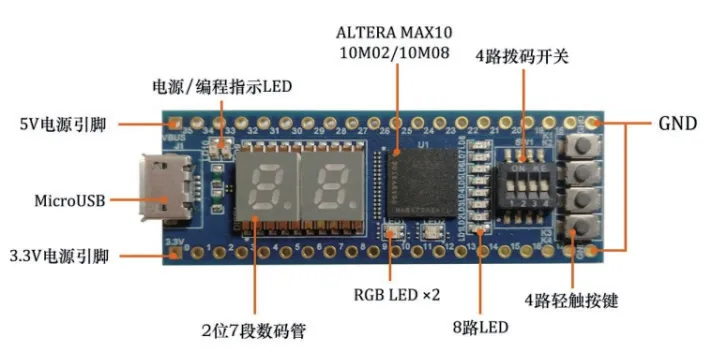

特别是对于FPGA 开发设计的教学仅靠课上时间是不够的,而传统实验箱体积大、价格高,通常放在指定实验室,不便于学员课下自主探究,故在数字电子技术课程中利用“FPGA 口袋实验室”进行实践教学及学员课外DIY 扩展。“FPGA 口袋实验室”选用思得普信息科技公司打造的STEP 小脚丫FPGA学习模块,板卡尺寸仅有52mm×18mm,小巧方便,打破时空限制,可应用在任何学员愿意实验和学习的地方。同时利用信息化资源和手段,如中国大学MOOC、爱课程、雨课堂等推送筛选过的相关内容,形成线上线下、课内课外多维度学习方式。

三 FPGA 实验内容设计

20 学时实验实践共包括6 个由易到难循序渐进的实验,其中5 个基础实验,每次实验2 学时,1 个综合设计实验,10 学时。虽然总学时不多,但是融入FPGA 设计后,相比传统实验箱,新实验内容反而更加充实和实用[3]。实验平台包括传统数电实验箱和STEP 小脚丫FPGA 学习模块。FPGA 开发板核心芯片选用了Intel-Altera 公司MAX10 系列产品,同时板上集成了USB-Blaster 编程器和按键、拨码开关、数码管、LED 等多种外设资源,支持Intel-Altera 工具Quartus 系列开发软件,如图1 所示。板上的IO 接口都通过2.54mm 通孔焊盘引出,可以根据自己的需求搭建硬件外设开发学习,如可以和面包板配合使用,或灵活的嵌入到其他的系统中,方便学员学习和扩展使用。

图1 STEP FPGA 开发板

实验一为小规模组合逻辑电路的分析与设计。第一部分在数字实验箱完成,测试TTL 与非门74LS00 逻辑功能及参数, 用现有芯片74LS00/74LS20 完成三人表决电路设计。第二部分介绍FPGA 学习模块,包括开发板布局、引脚分配及Quartus Ⅱ开发工具的基本操作,了解FPGA 器件的一般开发流程,学员点亮LED 灯,通过这个简单工程掌握开发的各个步骤,初步感受硬件描述语言,因此是第一个工程,非常适合入门。

实验二为中规模组合逻辑电路的分析与设计。第一部分测试译码器74LS138 的逻辑功能,学会用MSI 设计组合逻辑函数的方法,用74LS138 与门电路设计全加器;掌握译码显示原理,使用译码器74LS47/74LS48 和LED 数码管显示数字0-9。第二部分用Verilog HDL 描述组合逻辑电路,实现3-8 译码器,加强学员对译码器逻辑功能的理解,巩固对Verilog 行为描述中case 语句的掌握。

实验三为触发器及其应用,第一部分为集成JK触发器74LS112 和D 触发器74LS74 的逻辑功能测试,并用D 触发器构成三位二进制加法计数器。在本次实验前已要求学员课前自行学习仿真文件编写及Modelsim 仿真软件使用方法,故第二部分实验用Verilog HDL 描述时序逻辑电路,要求用开发板实现边沿触发的D 触发器,并通过STEP FPGA 开发板12MHz 晶振作为触发器时钟信号,拨码开关的状态作为触发器输入信D,触发器的输出信号用来驱动开发板上的LED,在时钟信号上升沿的驱动下,当拨码开关状态变化时LED 状态发生相应变化,并用ModelSim 观察仿真结果和实验现象。

实验四为中规模时序逻辑电路分析与设计,第一部分掌握常用中规模计数器的逻辑功能和使用方法,用74LS161 设计模10 及模48 计数器。第二部分用Verilog HDL 实现分频电路,即将12MHz 时钟信号分频以产生1Hz 的秒脉冲输出,要求输出信号的占空比为50%,同样用ModelSim 观察仿真结果和实验现象。

实验五为数字流水灯,实验课前要求学员查阅相关资料,对实现流水灯的方式有初步了解。这是一个数字电子技术实验的典型案例,将译码器、计数器、分频器、移位寄存器、FPGA 器件、Verilog HDL 及EDA 技术等相关知识结合起来,实现一个功能比较简单、又具有一定趣味性的流水灯实验项目。本实验的过程是掌握了基本的数字电路的基本知识和相应的FPGA 知识的基础上实现一个比较完整的实验。实验分为基本要求可扩展要求两部分,基本要求为利用小脚丫实验板上自带的12MHz 时钟进行分频,合理设置LED 灯变换的时间间隔,实现8 路LED 灯从上到下/从下到上依次熄灭。扩展要求如下:(1)8 路LED灯分成两半,全亮后由两边向中间对称依次熄灭,全灭后再从两边向中间对称地依次点亮。(2)8 路LED灯一起点亮,然后一起熄灭,点亮与熄灭的时间间隔相同,时间间隔自定,重复4 次,完成闪烁功能。(3)以上4 种模式在变换的同时,将模式的编号通过一个数码管显示出来,比如,流水灯的显示效果为模式1时,数码管显示数字“1”,四种模式编号由设计者自定。(4)自定LED 灯的变换方式。(5)设置快慢两种节拍的变换,变换速率自定,但要以人眼睛便于观察为准。扩展要求不安排课内学时,供有兴趣、有能力的同学在课外选做。如果学员完成了扩展实验,也将作为平时成绩的一部分。

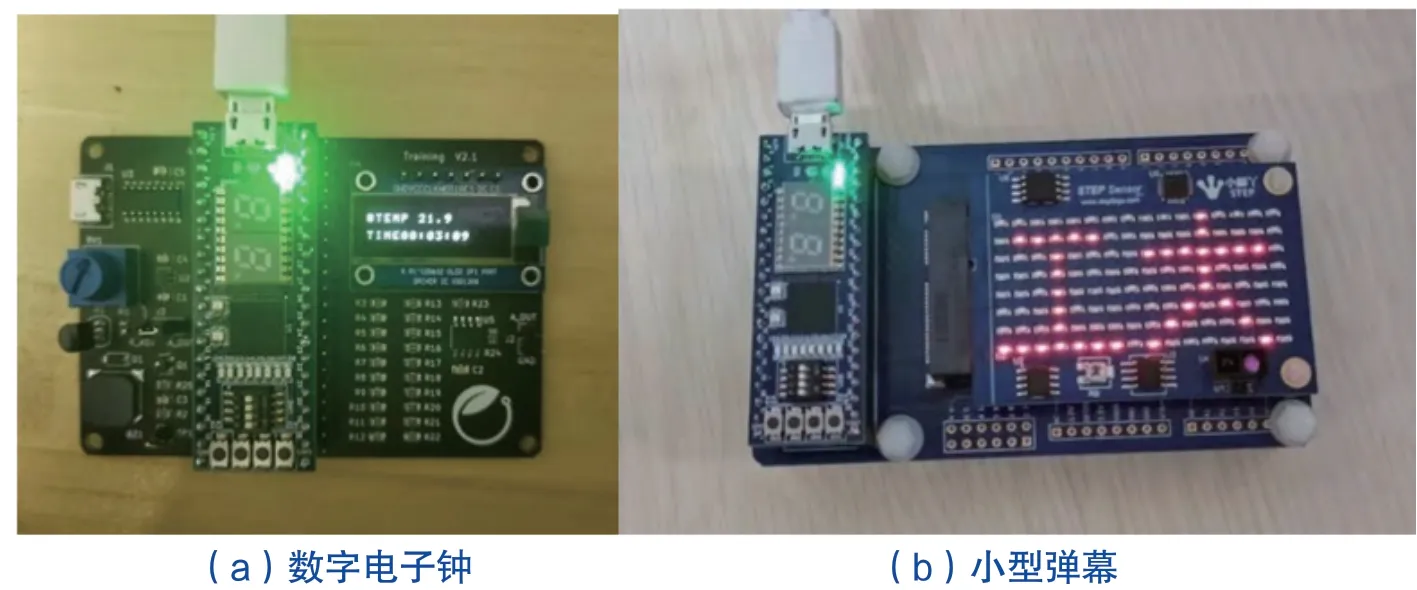

实验六为综合设计实验,学员2~3 人一组,以组为单位,每组增加一块扩展板,可在简易交通灯、数字电子钟、抢答器、密码锁中选择,或学员自主构思设计内容。实验内容如下:(1)简易交通灯实验要求交通灯主路上绿灯持续15s、黄灯3s、红灯10s的时间;交通灯支路上绿灯7s、黄灯3s、红灯18s的时间。(2)抢答器实验要求至少4 组选手,主持人复位开始抢答,获得抢答的选手对应LED 显示,答题时间超过30 秒报警,每位选手初始分数5 分(RESET 复位),主持人控制加分减分按键,每次增加或减少1 分(最多9 分),选手分数显示在数码管。(3)数字电子钟实验基本要求为准确计时,以数字形式显示时、分,并用OLED显示当前时间,具有校时、整点报时功能。扩展功能为小脚丫通过板上的温度传感器实时测量环境温度,实现温度计的功能,并同时间一起显示在OLED 的屏幕上。(4)密码锁实验基本要求为通过按键输入密码,OLED 显示输入密码,开锁成功或者密码输入错误后,可以进行清零重新输入。扩展功能为具有更改密码功能;输入过多错误密码,锁死功能;密码正确,指示灯给出指示;不正确,蜂鸣器给出报警。(5)自定义实验要求学员在自定义的系统中包含4 个以上模块,在实践前由学员自主提出设计目标,后期检验目标达成度。评分时,若学员完成简易交通灯得7 分、抢答器得8分、数字电子钟或密码锁视完成情况得8~10 分,自定义实验视完成情况得7~10 分。学员作品展示如图2 所示,图(a)为实现时间显示、温度显示、校时及整点报时功能的数字电子钟;图(b)为学员自主设计项目,配合使用点阵LED 显示板及PCIE 转接板,实现小型弹幕,如文本的滚动、暂停、互换显示等。

图2 学员作品展示

除实验课外,为了加快学员从74 系列芯片硬件实验向FPGA 口袋实验室的顺利过渡[4],同时配合课下DIY 设计。共分为三次DIY,第一次DIY 在实验二之后,要求学员自行学习如何编写仿真测试文件以及掌握Modelsim 仿真软件使用方法,任选一电路进行仿真验证。如图3 所示即为学员仿真截图,图(a)为触发器仿真波形,图(b)为计数器仿真波形。第二次DIY 在实验三之后,要求学员实现三位二进制加法器,拨码开关作为输入,结果由数码管显示。第三次DIY 在实验四之后,要求写出数字钟的小时时间计数器程序,即从1 开始计数到12,然后又从1 开始,周而复始,带有复位端和计数控制端,并进行逻辑功能仿真,给出仿真波形。

图3 modeIsim 仿真波形图

实验及DIY 要求将设计电路下载至实验板进行功能仿真/验证,可拍摄小视频简单讲解,一份电子版报告,包括实现方案(如系统设计、每个模块介绍等)、实验结果总结、制作过程中遇到的问题及解决方法或心得体会,当然如有其他呈现形式,也可自行选择。

上述实践内容设计兼顾传统与现代数字逻辑电路设计方法,由简单到复杂、由基础到综合,循序渐进,易于学员理解掌握,既能培养学员的自主学习能力,又能训练其工程综合能力[3]。数字电路是学习FPGA的基础,而通过FPGA 实践能够真正掌握数字电路。

四 结语

数字电子技术课程具有理论和实践紧密结合的特点,在内容设计时重视基础理论知识的认知过程,通过由易到难的实验及课外DIY 设计逐步提高理论基础及培养开发能力。同时为学员创设探究学习、应用知识的情境,搭配FPGA 口袋实验室,学员将自己的设计或创意在FPGA 上实现,有利于全开放、自主学习实验教学模式的实施[4],让学员经历一定程度的“学习尝试”和“学习探险”,促进实验教学内容改革。

——以中国民用航空飞行学院为例