一种具有子沟槽结构的屏蔽栅MOSFET 的研究

朱晨凯 ,赵琳娜 ,顾晓峰 ,周锦程 ,杨 卓

(1.江南大学电子工程系 物联网技术应用教育部工程研究中心,江苏无锡 214122;2.无锡新洁能股份有限公司,江苏 无锡 214122)

随着垂直刻蚀沟槽技术的进步,硅基沟槽(Trench) 型金属氧化物半导体场效应晶体管(MOSFET,Metal Oxide Semiconductor Field Effect Transistor)逐渐取代了平面型MOSFET,在计算机、手机、汽车电子等领域具有广阔的应用市场[1-2]。但在高频开关应用中,特别是当工作频率超过1 MHz 时,由于具有较大栅漏电容(Cgd),Trench MOSFET 面临着高栅极驱动电流、较大的栅极驱动损耗、瞬态响应变差等问题[3]。为了解决上述问题,研究人员提出了多种可有效减小Trench MOSFET 栅极电荷(Qgd)和Cgd的器件结构。Kim 等通过使用低压化学气相沉积(CVD,Chemical Vapor Deposition)技术,在沟槽底部沉积较厚的氧化物,从而减小Cgd的沟槽底部分量[4]。但是由于工艺的限制,无法保证不同批次Cgd垂直分量的一致性。为了同时减小Cgd的沟槽侧壁分量和底部分量,Blanchard 和Hirler 等提出在沟槽的下部(包括侧壁和底部)使用厚氧化物,由此产生阶梯状栅电极,形成一个具有场板(FP,Field Plate)结构的栅极,减小沟槽附近的电场强度和Cgd。尽管FP 有助于缓解沟槽底部的电场集中现象,但由于其和栅极连接,FP 引起的寄生电容仍是构成Cgd的一部分[5-6]。2003 年,Baliga 等首次提出了屏蔽栅沟槽(SGT,Shield Gate Trench) MOSFET 结构,将晶体管的栅极分为上下两部分,上部为控制栅(CG,Control Gate)连接栅电极,下部为掩埋式FP 接地[7]。分离栅结构将部分Cgd转化为漏源电容(Cds),显著降低了Cgd和Qgd,提升了器件的开关频率,降低了开关损耗。

为了进一步优化SGT MOSFET 内部的电场分布,改善器件的击穿电压(BV,Breakdown Voltage)和特征导通电阻(RON,On-Resistance) 之间的折衷关系,Kobayashi 等提出了阶梯场氧结构,调节了外延层的纵向电场分布,提高了器件的BV[8]。Chien 等通过使用三层外延结构,在不同浓度外延的交界处引入新的电场峰值,使得器件纵向电场分布更接近于矩形分布[9],从而提高器件的性能。但是这些结构需要多重淀积和蚀刻步骤,使制造成本增加。本文提出了一种具有子沟槽(ST,Sub Trench)结构的SGT MOSFET (STSGT),即在相邻的主沟槽之间插入子沟槽。该结构工艺步骤与传统SGT-MOS(C-SGT)结构的基本相同,不需要复杂淀积与刻蚀工艺。基于Sentaurus TCAD 软件对ST-SGT 的电学特性进行了研究,并与传统SGT的性能进行了仿真对比。

1 器件结构

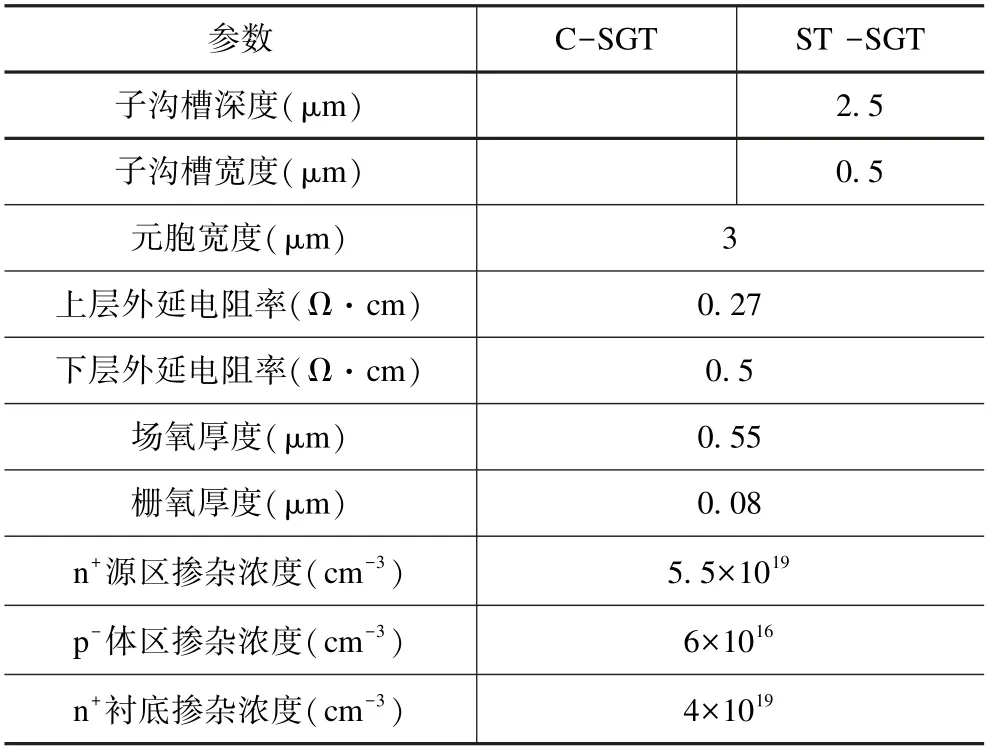

图1 所示为C-SGT 结构和本文提出ST-SGT 结构的截面示意图。C-SGT 结构中沟槽顶端两侧为CG 接栅电极,中间是多晶硅形成的FP 作为屏蔽栅接源极电位(地)。两种器件结构的区别在于,ST-SGT 结构在主沟槽之间插入了子沟槽,子沟槽内淀积多晶硅连接栅电极。两种器件均采用双层外延技术,下层外延厚度为4 μm,上层外延厚度为5 μm。ST-SGT 的主沟槽与C-SGT 结构沟槽的深度和宽度均相同,分别为5.5 μm 和1.45 μm。表1 列出了两种器件的部分参数。

表1 C-SGT 和ST-SGT 结构参数Tab.1 Parameters of C-SGT and ST-SGT

图1 C-SGT 和ST-SGT 的截面示意图Fig.1 Cross-sectional views of C-SGT and ST-SGT

2 仿真结果和讨论

2.1 工艺仿真

首先使用工艺仿真软件TSUPREM4 搭建C-SGT和ST-SGT 器件结构。图2 所示为制备ST-SGT 器件的工艺仿真流程[10]。在双层外延衬底上通过两步刻蚀工艺进行主沟槽和子沟槽的刻蚀,沟槽底部为圆弧状,如图2(a)~(b)所示。然后在沟槽中淀积氧化物和n型多晶硅,并刻蚀多晶硅至硅表面下方形成主沟槽内的屏蔽栅,并刻蚀场氧层形成栅极沟槽,如图2(c)~(e)所示。接着热生长栅氧,在栅极沟槽处生长出较薄的栅氧层,热生长的条件为湿氧环境,温度高于1000 ℃,如图2(f)所示。之后淀积n 型栅极多晶硅填满栅极沟槽,回刻多晶硅形成器件栅极;注入硼(Boron)杂质,经过高温热退火形成p 型体区;注入砷(Arsenic)杂质,激活后形成n+源区,如图2(g)~(i)所示。最后淀积和选择性刻蚀厚二氧化硅,刻蚀硅外延形成接触孔,然后注入氟化硼与硼杂质来降低接触电阻,淀积金属铝,将接触孔填满形成源极金属。

图2 ST-SGT 结构工艺步骤示意图Fig.2 Process flow for the proposed ST-SGT

接着,利用Sentaurus TCAD 软件对C-SGT 和提出的ST-SGT 结构进行模拟仿真和优化。仿真物理模型包括Schockley-Read-Hall(SRH)复合模型、俄歇(Auger)复合模型、掺杂依赖(Doping Dependency)模型和高场速度饱和(High Field Velocity Saturation)模型等。本文引入品质因数(FOM,Figure-of-Merit)来比较MOSFET 的性能。品质因数的定义为:

2.2 C-SGT 优化

图3 所示为C-SGT 器件在外延厚度固定的情况下,不同沟槽间距和上层外延电阻率对器件FOM 值的影响。从图中可以看出,当上层外延电阻率为0.15 Ω·cm,沟槽间距为0.8 μm 时,器件具有最优FOM 值为425.7 MW·mm-2,对应的BV 为127.2 V,RON为38 mΩ·mm2。

图3 FOM 随上层外延电阻率的变化Fig.3 FOM changes with upper epitaxial resistivity

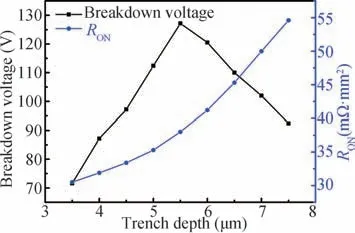

图4 所示为固定C-SGT 器件的上层外延电阻率为0.15 Ω·cm,沟槽间距为0.8 μm 时,不同沟槽深度对器件的BV 与RON的影响。从图中可以看出,当沟槽深度为5~6.5 μm 时,满足器件100 V 耐压需求。当沟槽深度小于4.5 μm 时,随着沟槽深度的减小,屏蔽栅的电荷补偿效应减弱,导致器件击穿电压降低;当沟槽深度大于6.5 μm 时,随着沟槽深度的增加,耗尽层逐渐展宽至衬底,电场集中于沟槽底部,器件击穿电压逐渐下降。因此选取屏蔽栅沟槽深度为5.5 μm,此时对应的FOM 值最大。

图4 BV 和RON随沟槽深度的变化Fig.4 BV and RON change with trench depth

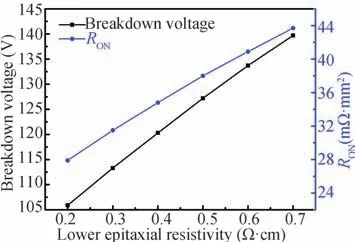

最后对下层外延电阻率进行优化。图5 为当CSGT 器件的上层外延电阻率为0.15 Ω·cm,沟槽间距为0.8 μm,沟槽深度为5.5 μm 时,不同下层外延电阻率时器件的BV 与RON曲线。由图中可以看出,器件的BV 与RON会随着下层外延电阻率的增加而增大,当下层外延电阻率为0.6 Ω·cm 时,具有最优FOM 值,此时C-SGT 器件的BV 值为133.7 V,RON为40.9 mΩ·mm2,FOM 值为437 MW·mm-2。

图5 BV 和RON随下层外延电阻率的变化Fig.5 BV and RON change with lower epitaxial resistivity

2.3 ST-SGT 优化仿真

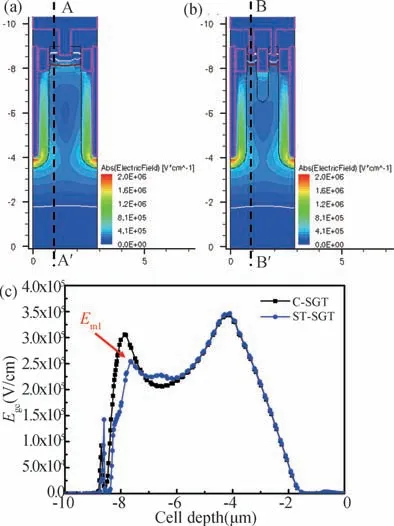

图6(a)、(b)分别为C-SGT 和ST-SGT 器件在栅极和源极接地、漏源电压Vds为120 V 条件下的二维电场(EF,Electric Field)分布图。从图中可以看出,两种器件的电场峰值均位于主沟槽底部,为3.5×105V/cm,这是由于接地的屏蔽栅深入外延层,当漏极接正向高电压时会在主沟槽底部引入高电场,此处电场强度比器件的体二极管(n-drift 层与p-body 层形成的pn结)处的电场强度更强,因此场氧的质量是影响器件性能的关键因素[11]。

(a) C-SGT 电场分布;(b) ST-SGT 电场分布;(c) 切线AA’ 和BB’ 处的电场强度曲线图6 C-SGT 和ST-SGT 结构在Vds=120 V 时的电场分布对比Fig.6 Comparison of EF distribution between C-SGT and ST-SGT structure when Vds=120 V

图6(c)为C-SGT 和ST-SGT 器件沿AA′和BB′的垂直EF 分布曲线。从图中可以看出,插入子沟槽明显降低CG 附近的EF 峰值,从而降低了栅氧化层击穿的风险,并同时抬升了外延层中部的电场,使得ST-SGT 结构的纵向电场分布更加均匀,这是由于子沟槽的插入调节了外延层的电荷平衡程度。

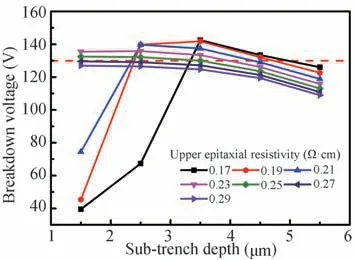

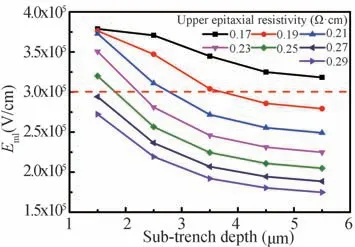

由于子沟槽的深度和外延掺杂浓度对器件的电场分布产生很大的影响,因此结合仿真研究了子沟槽深度和上层外延电阻率对ST-SGT 器件电学特性的影响。为了与主沟槽中的栅极宽度保持一致,子沟槽的宽度固定在0.5 μm。图7~8 所示为上层外延电阻率从0.17 Ω·cm 到0.29 Ω·cm、沟槽深度从1.5 μm 到5.5 μm 几种情况下仿真得到的BV 和RON随子沟槽深度的变化曲线,图中虚线为C-SGT 结构的BV 值(129.9 V)和RON值(45.3 mΩ·mm2)。从图7 中可以看出,当上层外延电阻率小于0.23 Ω·cm 时,随着子沟槽深度的增加,ST-SGT 的BV 值呈现先增大后减小趋势,且变化范围较大;当上层外延电阻率大于0.23 Ω·cm 时,随着子沟槽深度的增加,ST-SGT 的BV 值呈现逐渐下降趋势,变化范围较小。从图8 中可以看出,在不同的上层外延电阻率情况下,随着子沟槽深度的增加,器件的RON值均呈现逐渐增加的趋势,这是由于随着子沟槽深度的增加,相对减少了外延层的面积,使得RON变大。

图7 BV 随子沟槽深度和上层外延电阻率的变化Fig.7 BV changes with sub-trench depth and upper epitaxial resistivity

图8 RON随子沟槽深度和上层外延电阻率的变化Fig.8 RON changes with sub-trench depth and upper epitaxial resistivity

为了探究图7 中ST-SGT 的BV 值显著下降的原因,研究了不同上层外延电阻率情况下,电场强度Em1随沟槽深度的变化曲线,如图9 所示。从图中可以看出,当上层外延电阻率小于0.23 Ω·cm、子沟槽深度小于2.5 μm 时,ST-SGT 器件栅极附近的电场强度明显高于C-SGT 器件相应位置的电场强度(3×105V/cm),导致栅氧化层过早击穿,降低了器件的BV 值。

图9 Em1随子沟槽深度和上层外延电阻率的变化Fig.9 Em1 changes with sub-trench depth and upper epitaxial resistivity

通过上述分析,调整ST-SGT 器件的上层外延电阻率可优化器件纵向电场,达到一个类矩形的分布,但同时器件的RON也会随着外延层电阻率的调整而发生改变,因此需要对器件的BV 和RON进行折衷考虑[12]。综合仿真结果,符合设计要求的ST-SGT 器件的子沟槽深度为2.5 μm、上层外延电阻率为0.23 Ω·cm,其FOM 值最大为445.45 MW·mm-2。此时器件的BV 值为135.8 V,RON为41.4 mΩ·mm2。

2.4 仿真结果对比分析

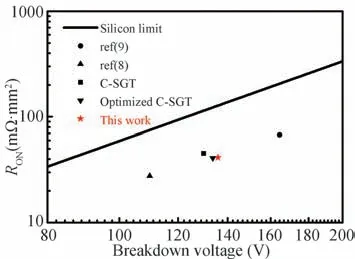

图10 对比了优化后的ST-SGT 器件、C-SGT 器件、优化后的C-SGT 器件和其他参考文献提出的器件的性能。优化后的ST-SGT 器件的FOM 值与C-SGT器件、优化后的C-SGT 器件、阶梯状氧化物FPMOSFET[8]、三层外延层结构SGT 器件[9]相比,分别提高了19.6%,1.9%,2.2%和11.6%。

图10 SGT 结构RON与BV 的关系和理想硅极限的比较Fig.10 Comparison of RON-BV relationship of SGT structures with the ideal silicon limit

3 结论

本文提出了一种具有子沟槽结构的 SGT MOSFET。在相邻的主沟槽间插入子沟槽,使器件的纵向电场分布更加均匀,同时改善了由高密度深沟槽带来的晶圆翘曲问题。通过仿真对提出的ST-SGT 结构进行优化设计,提高了器件的击穿电压,减小了特征导通电阻,最后得到:当子沟槽深度为2.5 μm,上外延电阻率为0.23 Ω·cm 时,器件的FOM 值最大,为445.45 MW·mm-2。与C-SGT、优化后的C-SGT、阶梯状氧化物FP-MOSFET 和三层外延层结构SGT 相比,其FOM 值分别提高了19.6%,1.9%,2.2%和11.6%。