基于FPGA的非易失性存储器NvRAM时序分析方法

马 雪,段宇博,安书董

(中航工业西安航空计算技术研究所 陕西 西安 710068)

0 引言

随着航空技术的快速发展,机载设备的更新换代,计算机技术在航空机载设备中日趋成熟。存储器作为计算机硬件中必不可少的一项设备,其性能及熟练的使用方式显得尤为重要。而非易失性存储器(Non-Volatile Random Access Memory,NvRAM)因其断电后数据仍然能够保留的特性大受推崇,并且NvRAM还具有速度快、自动保存和自动恢复数据等功能,电路设计相对简单,被广泛使用在机载设备当中[1-2]。随着存储器的性能逐渐在计算机系统中占据了越来越重要的位置,能否高效准确运用存储器就有了更高的要求。

在工程中,开发者们逐渐发现对于存储器的控制逻辑相对复杂,时序要求也比较严格,且在调试过程中,存储器出现异常后的故障定位也因为时序的复杂性而变得非常纷繁复杂,这就使得开发人员在硬件调试过程中耗费了相当多的资源[3-4]。本文重点介绍利用FPGA作为存储器控制器来对非易失性存储器进行控制的过程,采用VHDL语言编写FPGA中的控制逻辑,来实现对存储器的使用;通过ISE Design Suite环境进行系统仿真,使用ChipScope技术分析FPGA控制存储器进行数据交换的时序逻辑。采用FPGA控制实现的NvRAM控制器,结合ChipScope逻辑分析技术可以明显提高系统调试期间的可控性。

1 NvRAM的结构

采用深圳市国微电子有限公司的SM14CA8-NF45型存储器,该存储器是一款128 K*8 bit容量的快速非易失性静态随机存储器芯片。存储器中的每个存储器单元都自带1个非易失性存储单元。芯片提供了快速的读写访问周期,方便使用,并且作为常规的SRAM具有无限的读写寿命。

当检测到掉电,数据会自动保存到非易失性存储单元(STORE操作)。一旦上电,数据会自动从非易失性存储单元加载到SRAM(RECALL操作)。STORE和RECALL均有逻辑软件控制。

该芯片的控制信号有:片选信号()、写使能信号()、输出使能信号()、STORE操作状态信号(),其中#代表低电平有效。数据位使用DQ[7:0]表示,地址位使用A[16:0]表示。

当和为低,和为高时,SM14CA8-NF45执行读操作。

当和为低,为高时,执行写操作。此时一般会在整个写操作周期使保持为高,以避免通用I/O上的数据总线竞争。如果被拉低,内部电路将在变低后tWLQZ(写使能到输出无效)时间内关闭输出缓冲器。该存储器的工作原理如图1所示:

图1 NvRAM结构框图

2 NvRAM的通用工作时序

图2给出了SM14CA8-NF45型NvRAM工作时读时序的波形。Q(Data Out)表示存储器输出的数据。A(Address)表示地址信号。分别是存储器高8位,低8位的数据线使能信号。表1给出了符号的代表含义。

图2 NvRAM读周期时序

表1 NvRAM读时序图符号解析表

由图2可知,在NvRAM的读操作时序内,分为3个阶段:读建立、读触发、读保持。tAVAV是一个读周期时间,地址信号A在该时间段内始终有效。一次完整的读数据的过程是:读建立阶段(Setup_State),信号先置为低电平,片选有效。读触发阶段(Pulse_State),信号保持低电平不变化,和信号同时置为低电平,数据有效,从存储器中读出。读保持阶段(Hold_State),和号设置为高电平,而信号仍然低有效,在读保持阶段的末期,信号位置高,结束一次读操作。

图3展示了SM14CA8-NF45型NvRAM一次写操作的时序波形。其中D(Data IN)表示主控向数据输入输出口所写入的数据。表2给出了符号所代表的含义。tAVAV是一个写周期时序,在写操作的一个周期tAVAV内同样分为3个阶段,在Setup_State时,和同时置低,片选有效产生,在Pulse_State阶段,置低,开始写入数据,该阶段为真正数据传输的阶段。在Hold_State阶段,先置高,随后和置高,结束一次写操作。

图3 NvRAM写周期时序

表2 NvRAM写时序图符号解析表

3 NvRAM控制器的设计

在对NvRAM控制器的设计中,需要用户将存储的数据地址、数据内容、数据长度、时序参数等信息发送给控制器,控制器按照读写时序自动进行配置完成整个数据的读和写[5]。如图4所示,本次采用58所公司JXCSX95T型FPGA作为该控制器的硬件载体,结合VHDL语言编程,用有限状态机(finite state machine,FSM)实现存储器控制器。同时控制器中还需要配置计数器对时序图中的各个参数状态进行计数,数据通路用来实现数据地址、数据的传递。

图4 NvRAM控制器结构

对于配置寄存器而言,主要用来定义NvRAM的存储类型、字长、地址、时序参数等。对于读/写操作,主要定义读写时序的逻辑有限状态机的有限个状态、状态跳转函数、开始状态以及终止状态。以NvRAM的一个写操作为例,在SM14CA8-NF45使用手册上查到AC特征表可知,写建立时间为小于9 ns或者大于42 ns的区域内,若控制器工作频率100 MHz(即周期为10 ns),则写建立共需要一个时钟周期即1拍。经时序图和时序参数可以计算出读触发的时间至少为8 ns,因此,写触发至少需要一个时钟周期。在写保持阶段,也需要一拍[6]。

本设计采用4个状态机实现,各状态之间的跳转需要满足各自计数器的节拍数根据时钟进行倒计数,若计数的值不是0,则保持当前状态,若等于0则进入下一状态。NvRAM的一个写操作的状态转移图如图5所示。图中状态名称与第2节状态名含义保持一致。其中IDLE状态表示不在一个读写操作内的例外状态。一次写操作的状态开始状态即为“IDLE”,当满足进入状态机的条件“片选有效且写使能有效时”,状态机跳转到“写建立”状态,在写建立周期结束(write_setup_time = 0)后,状态机跳转进入“写触发”状态,在写触发周期(write_Pulse_time)内,该控制器可以将数据有效写入。在一个写触发周期结束后,逻辑状态机跳转进入“写保持”状态,写保持周期(write_Hold_time)内,数据不再写入,但只有结束一次写保持周期,状态机才会跳转进入“IDLE”状态。这样才能再次进入下一次写操作或者读操作。否则逻辑状态机错误运转。

图5 NvRAM逻辑状态机状态转移图

根据NvRAM的读写状态机,使用VHDL实现一个写操作的伪代码如图6。伪代码先定义了写操作状态机的有限个状态,是有限个状态跳转条件。然后一次begin到end case的过程,即为一次写操作的逻辑状态机使用VHDL语言实现的具体过程。

图6 NvRAM写操作状态机VHDL伪代码

4 ChipScope在线调试结果

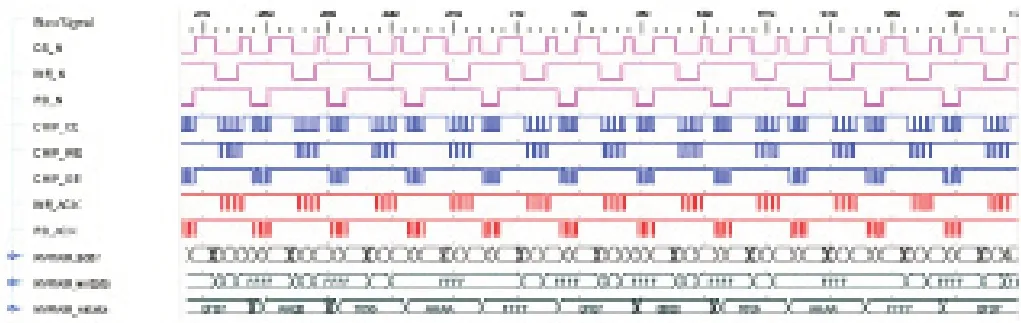

通过上述分析,结合有限状态机设计存储器控制器,利用VHDL语言作为控制逻辑编写语言,以ISE Design Suite 13.3和IMPACT为开发环境,以FPGA为硬件载体,对程序进行下载。与此同时,采用Xilinx开发环境自带的ChipScope逻辑分析仪在具体调试中进行时序分析,ChipScope使用方法大致为:设置一个触发条件,一般为逻辑状态的时钟条件,当存储器控制器开始运转,时钟生效,则ChipScope开始监控该控制器的所有读写操作时序。同时ChipScope可以允许用户根据自身调试需要,来自主选择需要监控的变量,该调试方法具有灵活性和可操作性。通过自主调试,在一次逻辑分析中,监控了该存储器控制器中的片选信号、读写使能信号以及数据流的状态。发现NvRAM可以正常工作,满足各种读写要求,且得出的时序图与NvRAM使用手册的时序图一致,在一次片选有效的周期内,能够正确进行读操作或者写操作。因此证明本文所设计的NvRAM控制器可以有效控制,该方法已经成熟运用在机载计算机中,满足各类机载试验要求。

NvRAM存储器工作时的读写操作时序图如图7所示。

图7 NvRAM控制器工作时序图

5 结论

综上所述,本文通过FPGA作为NvRAM存储器的控制器,有效按照时序控制存储器进行读写操作,具有较高的灵活性,同时结合ChipScope逻辑分析仪可以进行在线调试,提高设计及调试系统的工作效率,可以为后续工程上对存储器的控制提供技术参考。